FPGA在数字示波器中的应用研究

2015-12-23严世胜钟承尧吴建清

严世胜,钟承尧,吴建清

(海南师范大学物理与电子工程学院,海南海口571158)

示波器在电子领域是十分常用而且重要的电子测量仪器,它能够直接观察以及显示被测量的信号,在工农业生产、军事、医疗以及教育等方面均有广泛的运用.然而传统的模拟示波器过于笨重、操作复杂、耗能高,这些缺点为我们的使用带来了诸多不便.而数字存储示波器是近年来随着计算机技术的飞速发展而发展起来的一种新型示波器,它是在模拟示波器的基础上不断地发展,增加了波形存储、测量数据的运算和分析等诸多功能[1].数字存储示波器是利用ADC技术把模拟信号转换成数字量进行存储再现的示波器,具有时间和幅度测量准确度大大提高的优点.

在数字存储示波器的数据采集系统中,A/D 转换器进行采样控制,传统的方法一般选用单片机完成.但由于单片机控制周期较长、速度慢,极大地限制了高速A/D转换器的性能和速度.而采用FPGA作为高速A/D 转换器的采样控制,其采样周期只有时钟频率为12 MHz单片机采样周期的千分之一,完全能胜任高速A/D转换器的要求.系统中利用了Altera公司生产的Cyclone 系列EP1C6Q240 作为设计的核心器件.使得示波器具有体积小、耗能低、结构简单和低成本等优点.

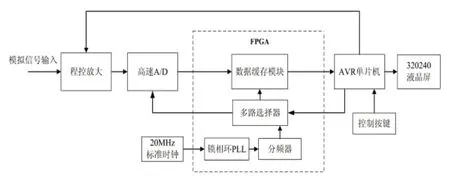

1 总体方案设计

该系统主要由程控放大电路、高速A/D转换器、数据缓存模块、多路选择器、分频器、LPM 嵌入式锁相环、AVR 单片机和液晶屏等组成[2-4],如图1 所示.除了程控放大电路、高速A/D转换器、AVR单片机和液晶屏外,其他电路的全部由一片FPGA完成.

模拟信号首先从外部输入到程控放大电路,放大或衰减到合适的幅度,然后再送入高速A/D 转换器中进行采样,采样后的数据存储到先入先出锁存器中,最后通过单片机将数据送到液晶屏中显示出波形.标准频率由20 MHz有源晶振提供,为FPGA提供标准时钟信号.

图1 数字示波器系统结构框图Fig.1 System diagram of a digital oscilloscope

2 功能模块电路设计

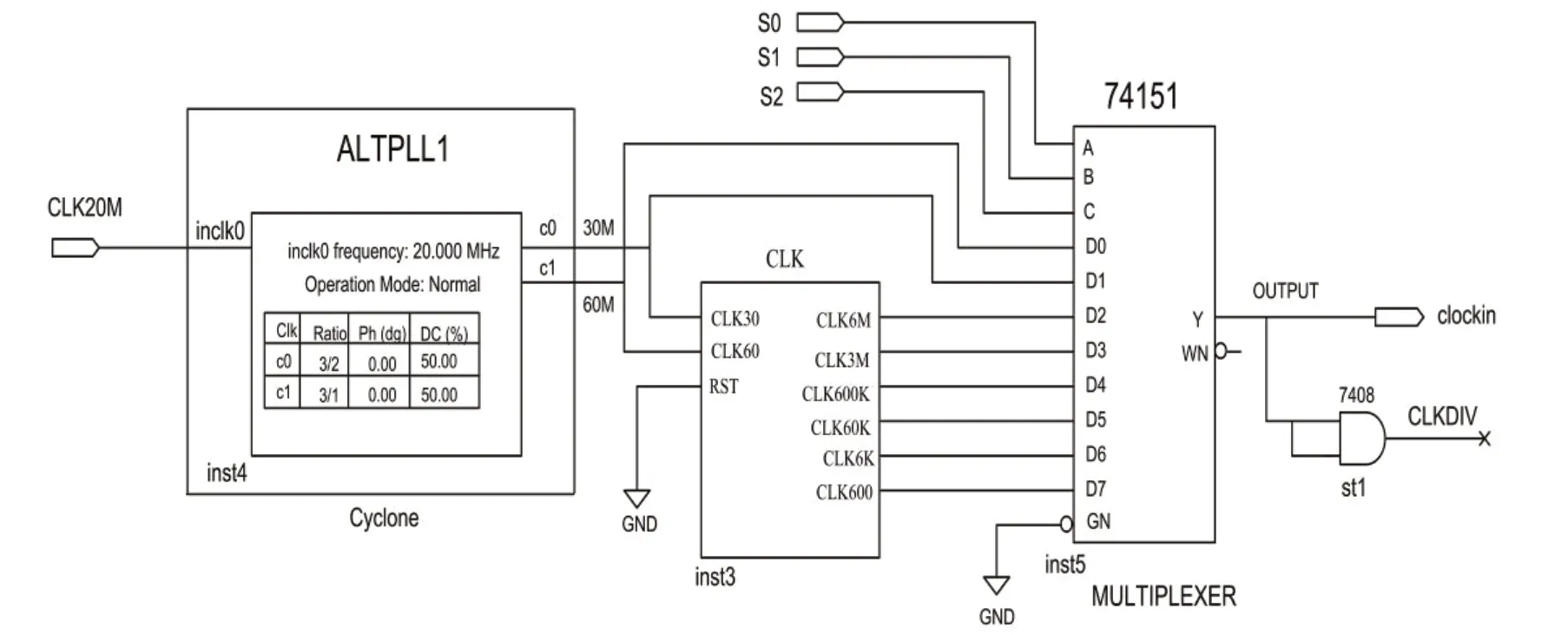

2.1 分频器和多路选择器模块的设计

分频器与多路选择器由锁相环ALTPLL1、分频器模块CLK、八选一数据选择器74151元件等共同构成了系统的时钟及选择器模块,见图2.

图2 时钟产生及选择器模块Fig.2 Clock generator and selector module

Cyclone系列的FPGA内含高性能的嵌入式模拟锁相环,这个锁相环PLL 能够和一个输入的时钟信号同步,并且以其作为参考信号实现锁相,从而输出多个同步的倍频或者分频的片内时钟.利用锁相环实现的内部时钟与直接来自外部的时钟相比,能够有效地减少时钟延时与时钟变形,改善时钟的建立与保持时间,从而减少来自外部的干扰,使系统能够更加稳定地工作.设计时由外部提供一个20 MHz的标准时钟信号给ALTPLL1 的输入端口inclk0,设置锁相环输出的两个信号c0、c1 分别为60 MHz 和30 MHz,并经若干个10分频模块后得到6 MHz、3 MHz、600 kHz、60 kHz、6 kHz和600 Hz的时钟信号,将这8种不同频率的时钟信号送到74151 的8 个输入端口D0-D7,通过AVR单片机控制S0、S1、S2三根选通信号线来控制多路选择器最后的输出时钟.这8 个不同频率的时钟是用来控制A/D 转换器的采样频率,即分别是示波器的8个时基档位:0.5μs/div、1μs/div、5μs/div、10μs/div、50μs/div、500μs/div、5ms/div 和50ms/div.

2.2 数据缓存模块的设计

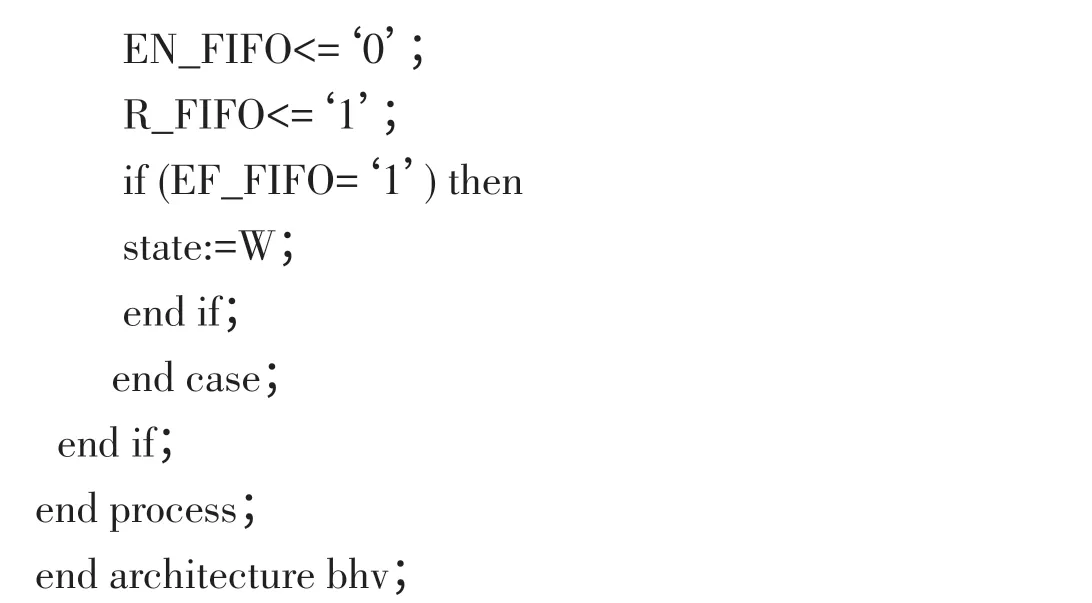

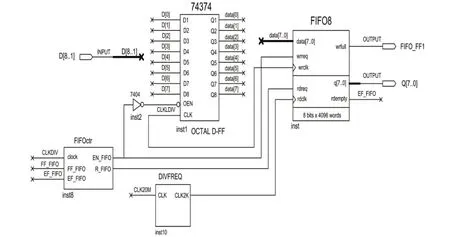

数据缓存模块由先入先出存储器FIFO8、锁存器74374、FIFO 读写控制模块FIFOctr、反相器7404和二十四分频器模块DIVFREQ等组成[5],见图3.

2.2.1 FIFO和锁存器模块

由于经过A/D 转换器传来的数据频率很高,显示屏无法直接显示,故而在A/D 转换器之后加上一个异步FIFO来起到高速数据缓冲的作用.在QuartusⅡ软件的Tools菜单中找到MegaWizard plug-in Man⁃ager工具,在其打开的窗口下选择LAM_FIFO+项,然后再对其进行简单的设置即可得到FIFO8 模块.这里只用到FIFO8 的3 个标志位中的2 个:满标志FF和空标志EF,FIFO8的数据宽度设置为8bits,深度设置为4096.FIFO8 模块中的wrfull 为FF 标志位,rdempty为EF标志位,wrreq 和rdreq分别为写数据位和读数据位,它们分别由wrclk 和rdclk 时钟来控制其读写的操作.data[7‥0]为FIFO的数据输入端,q[7‥0]为FIFO的数据输出端[6-8].

实验表明,A/D 转换器在开机启动后的几个时钟周期内采样不是很可靠,这将使得FIFO8 存储的数据也不准确,从而导致在显示屏上显示的波形不准确.为了解决这个问题,可以让A/D转换器一直工作,通过FIFO8 来控制A/D 转换器采样.在FIFO8 之前接入一个74374 锁存器,这样就达到了锁存数据以及提高数据稳定性的目的.

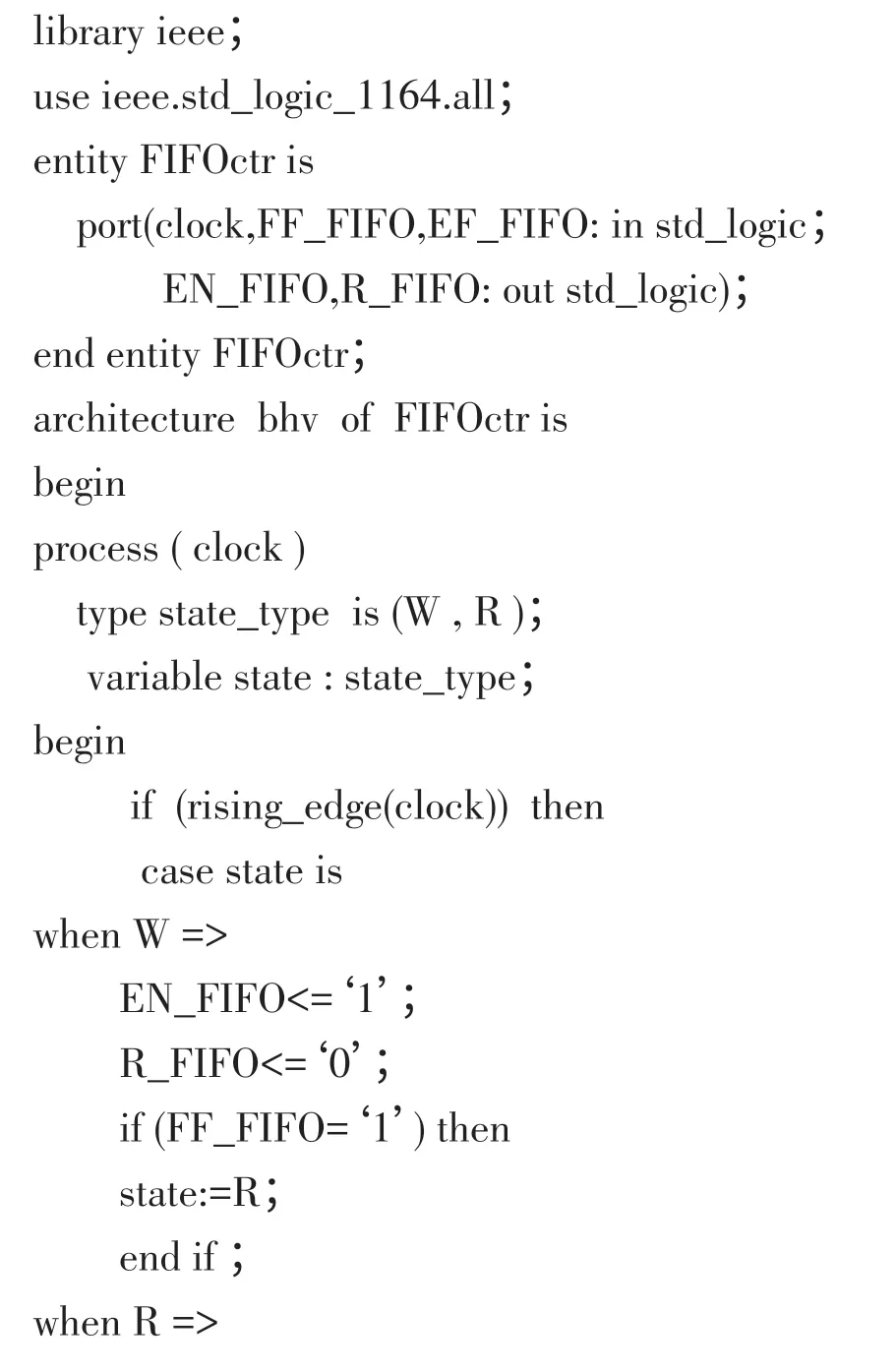

2.2.2 FIFOcrt读写控制模块FIFO8 写时钟wrclk 与A/D 转换器采样时钟一样,由八选一多路选择器提供.读时钟rdclk 由二十四分频器模块DIVFREQ 提供.由于FIFO8 读数据的速度比写数据的速度要快很多,避免读取数据时经常出现间断的现象,需要控制wrreq 和rdreq 位,让FIFO8 写数据写满时才开始读取数据,当数据被读空时将不进行任何读取的操作,此时只能进行写数据的操作.为此利用FIFOctr 模块来实现对其控制,实现FIFOctr模块的VHDL源程序如下[9]:

图3 数据缓存模块Fig.3 Data caching module

2.3 高速AD转换器

数字示波器中最重要的电路之一是A/D 转换器,它的作用是将被测信号采样并转换成数字信号存入存储器,因为它直接决定着数字示波器所能测量的最高频率,根据乃奎斯特定理,采样频率至少是被测信号最高频率的2 倍才能复现出被测信号.而在数字示波器中采样频率至少应该是被测信号频率的5~8倍,否则根本观察不到信号的波形.设计中选用美国德州仪器(TI)公司的8位半闪速结构的TLC5510,它是一种采用CMOS 工艺制造的8 位高阻抗并行A/D 转换芯片,转换速率为5MSa/s~40MSa/s.通过改变FPGA 输出不同的时钟来控制TLC5510 的采样频率,并将采样后的数据送到FPGA中缓存[10].

3 实验结果

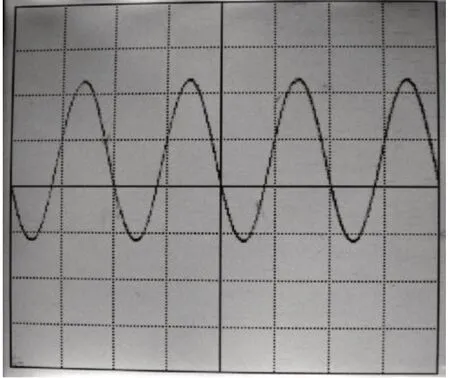

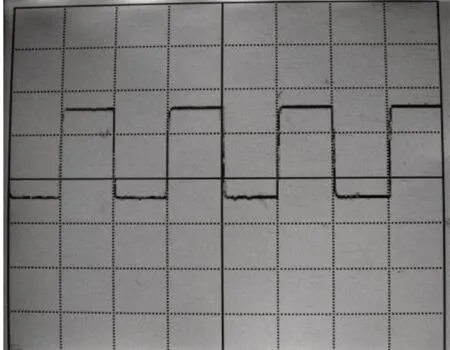

系统中选用320×240点阵的液晶显示屏作为波形显示;选用AVR 单片机Mega64 作为系统控制.该示波器能实现信号幅度和频率的测量,达到一定的精度要求.在5μs/div的时基档位下对输入的100kHz正弦波和方波信号进行测量,测试波形见图4、图5.

图4 100kHz正弦波测量Fig.4 100kHz sine wave measurements

图5 100kHz方波测量Fig.5 100kHz square wave measurement

4 结论

以FPGA作为A/D转换器采样控制和数据缓存,完成相关电路的设计与测试.实验测试表明,FPGA在数字存储示波器中得到了很好的运用,工作稳定、可靠,达到了较好的效果.而且系统还具有频带宽、体积小、开发成本低和扩展方便等特点,具有较高的应用前景.

[1]程志强,汪思静,杨杰,等.嵌入式数字存储示波器的设计[J].电子设计工程,2013,21(2):162-164.

[2]孙盛坤,丁昊,宋杰.基于FPGA 和TFT 彩屏液晶的便携示波器设计[J].电子设计工程,2011,19(4):158-161.

[3]申礼斌,李立欣,冯浩.基于SOPC 的便携式数字示波器设计与实现[J].电子设计工程,2014,22(18):65-68.

[4]王庆春,何晓燕.基于FPGA的手持式示波器设计[J].现代电子技术,2013,36(10):106-108.

[5]石明江,张禾,河道清.基于FPGA 的手持式数字存储示波器显示驱动设计[J].液晶与显示,2010,25(5):738-742.

[6]宋鹏飞,王厚军,曾浩.高速深存储数据采集系统研究与设计[J].仪器仪表学报,2011,32(4):904-912.

[7]杨培善,许忠仁,付贵增,等.基于FPGA的高速A/D转换控制器设计[J].电子技术应用,2009,35(6):65-68.

[8]杨军,孔兵,宋克俭,等.基于FPGA的高速异步FIFO存储器设计[J].云南大学学报:自然科学版,2007,29(6):560-565.

[9]潘松,黄继业.EDA 技术实用教程[M].北京:科学出版社,2010:211-214.

[10]于胜学.闪速8位A/D 转换器TLC5510 与单片微机的接口技术[J].微计算机信息,2009,25(9):15-16.