DSP和FPGA技术在通用数字信号处理系统设计中的应用

2015-12-21钟先芳江西信息应用职业技术学院江西南昌330043

钟先芳(江西信息应用职业技术学院,江西南昌,330043)

DSP和FPGA技术在通用数字信号处理系统设计中的应用

钟先芳

(江西信息应用职业技术学院,江西南昌,330043)

DSP和FPGA技术在数字信号处理系统设计中的应用,使得系统的处理能力更强、开发灵活性更显著。本文通过对通用数字信号处理系统中的软硬件设计分析,研究了DSP和FPGA技术在系统中的具体应用。

DSP;FPGA;数字信号处理系统

0 引言

图1 系统工作流程

到上位机,最后在上位机程序进行处理结果的显示,同时将其与仿真结果进行比较分析。

信号处理的主要功能是借助于对被测信号再时域或变换域的特性分析与处理,更明确的认识信号特性与本质,进而得到所需信号形式,提高信息的利用程度。随着DSP和FPGA技术的开发,其在通用数字信号处理系统设计中的应用,对系统的改造升级注入了新的血液。因此,本文试图通过对DSP和FPGA技术在通用数字信号处理系统中的应用进行研究,探索数字信号处理系统优化新路径。

1 系统总体设计

系统主要由数字信号处理单元、FPGA控制电路、外设电路三部分组成。其中。数字信号处理单元则主要实现数字信号的处理工作,FPGA的主要作用是实现电路接口时序控制,并进行数据缓冲,外设电路包括信号发生与采集电路、USB接口电路、语音信号控制电路。图1为系统工作流程。

由图1可知,系统在工作过程中,首先是通过上位机进行数字信号处理功能的选择,并借助于USB接口将控制命令传输到FPGA;然后FPGA在接收到控制命令之后,将其传输给DSP,接着再由DSP根据命令要求进行数据处理,并将处理后的数据再传输给FPGA,并再次借助于USB接口将处理后的数据传输

2 硬件设计

2.1 DSP 部分设计

TMS320C6455是TI的6000系类中一款性能较高的定点数字信号处理器,期频率最高可达1.2GHz。片内不仅有高性能的C64x+数字信号处理器内核,还有充足的外设资源,如用于片级互联的RapidIO接口、McBSP接口、DDR2接口、JTAG仿真接口、I2C接口、64位的EMIF接口、千兆以太网控制器、PCI接口等。板卡采用2片TMS320C6455进行协议解析及数据处理,两片DSP采用RapidIO接口互联,以实现两个DSP之间高速的数据交互功能,其双向传输速率最高可达3.125Gbps。同时每片DSP提供对外RapidIO接口2路,可与其他模块进行RapidIO总线数据通信。DSP通过DDR2接口直接扩展2片DDR2存储,用来存贮数据和程序,两片DDR2采用是数据线并联方式,形成32位存储位宽,有效提高系统的性能。每片DSP会单独外挂一片FLASH,用来存储程序代码,系统上电后,DSP通过二次加载将代码加载至DSP。DSP的EMIF总线连接至FPGA,实现资源共享,扩展外围接口。

2.2 FPGA部分设计

FPGA作为整个设计的核心模块,在系统的设计方面起着重大的意义,极大的增强了系统的灵活性,在本设计中FPGA与DSP的EMIFA总线的CE2、CE4空间相连,充分利用了TMS320C6455的处理能力,需要将EMIFA的数据线、地址线、控制线均与FPGA进行连接;LVDS外挂到FPGA上,减少DSP的EMIF总线压力的情况下同时增加了LVDS处理的灵活性;两个FPGA都需要通过CPLD进行加载,设计采用主并行的加载模式,CPLD模拟PlatformFLASH的作用,所以FPGA的并行配置管脚与CPLD连接。同时,每个FPGA对外有一路RS422接口、一路RS485接口和一路RS232接口。

DSP与FPGA的通信接口设计中,通过DSP的EMIF总线与FPGA进行连接,将DSP的CE2空间与CE4空间分配FPGA,将DSP的EMIF总线的数据线、地址线、控制线等与FPGA连接。DSP与FPGA可以通过EMIFA总线进行通信,同时可以对EMIFA总线上的外设进行操作;FPGA与DSP通过一个McBSP连接,可以快速的进行数据交换;同时DSP的GPIO口与FPGA连接,方便测试与功能扩展。

3 软件设计

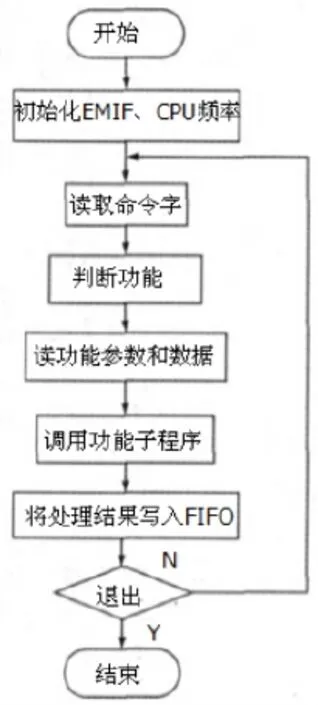

DSP程序设计开发环境选择TI公司的CCStudiov3.3,编程语言选择标准C语言。DSP程序通过对由上位机发出的控制命令进行数据信号处理后,经FPGA内部FIFO,借助USB接口再传输到上位机,若传输正确,则直接结束,若传输有误,则需要退出,重新读取FPGA传输的命令字。其工作流程如图2所示。

由图2可以看出,DSP首先通过合理配置内部寄存器,初始化EMIF、CPU频率,然后根据地址解读FPGA传输的命令字,并对其进行功能类别的判定,读取功能参数与数据,调用功能子程序进行数据处理与计算,最后再将处理后的数据传输到FPGA,借助于USB接口将处理后的结果传输到上位机,同时通过信号发生或语音模块输出。

图2 DSP程序流程图

4 系统测试

结合数字信号处理系统功能与技术要求,本文对基于DSP和FPGA的通用数字信号处理系统进行了测试。测试结果表明:DSP程序能够正常工作,顺利实现其数字信号处理功能;PGA逻辑工作稳定,可依据上位机控制命令控制好各个电路模块;系统其他各项功能均符合系统运行要求,数据处理结果与软件仿真结果一致,完成了数字信号处理任务。

5 结论

本文通过对通用数字信号处理系统软硬件设计的具体分析,体现了DSP和FPGA技术在系统中的具体应用,并通过系统测试验证了系统设计的可行性与合理性。系统测试结果表明本系统中的DSP和FPGA部分均能正常工作,实现了通用数字信号处理的基本功能,可应用于各个所需领域。

[1]郑运冬.基于FPGA的FIR滤波器设计与实现[D].复旦大学,2013.

[2]何浩. 基于DSP和FPGA的图像处理平台的研究和实现[D].南京航空航天大学,2011.

[3]詹振环. 基于双多核DSP的图像处理平台设计[D].中国科学院研究生院(西安光学精密机械研究所),2013.

Application of DSP and FPGA technology in the design of general digital signal processing system

Zhong Xianfang

(Information Application Jiangxi Vocational and Technical College,Jiangxi Nanchang,330043)

The application of DSP and FPGA technology in the design of digital signal processing system, which makes the system's ability to handle more, develop more flexible. In this paper, the design and analysis of the software and hardware design of the general digital signal processing system, the application of DSP and FPGA technology in the system is studied.

DSP; FPGA; digital signal processing system

TN911.72

A