基于FPGA+DSP的振动主动控制系统设计

2015-12-20董淑伟杜鹏飞

董淑伟,郑 宾,杜鹏飞

(1.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原030051;2.中北大学 山西省光电信息与仪器工程技术研究中心,山西 太原030051)

0 引 言

振动主动控制具有通用性较大、控制效果好等优点,特别是对抑制低频振动以及随机振动具有无法比拟的优点[1,2]。然而在实现中由于振动信号频率高、算法处理复杂及实时性要求高等特点,采用传统的采集处理系统无法满足要求,因此在实际应用中需采用多个处理器协同的方法完成振动主动控制。

随着电子技术和信息技术的飞速发展,各领域对系统的采集和处理速度的要求越来越高,传统的FPGA+USB+PC系统已无法满足实际要求。而如果采用FPGA+DSP的架构,由于FPGA 运算速度快且逻辑控制能力强,DSP复杂算法运算能力强,通过对分别FPGA 和DSP进行功能划分,可以充分发挥各自的优点;其次无需PC 机的介入,系统运用起来会十分方便灵巧[3-5]。于是本文提出了一种FPGA+DSP的协同处理架构,很好地把两者的优点结合到一起,兼顾了速度和灵活性,能够达到致动器对控制目标的实时控制,可以满足实验要求。

1 系统整体设计

FPGA+DSP构成的处理系统结构如图1所示。FPGA主要完成外围电路的时序控制和寄存器的配置,DSP 完成各种复杂算法处理[6,7]。当系统完成配置正常工作后,模拟信号源经过转化率为40MPSP的A/D 转化成数字信号,在FPGA 内进行简单处理后送入外部存储器DDR 中进行缓冲,当DDR 存满后,在FPGA 内部定制的软核处理器MicroBlaze通过指令读取缓冲区的数据进行简单处理,处理后的数据经过EMIF接口送给DSP 进行复杂算法处理,从中提取控制信息并将其送回FPGA,在FPGA 内将其分成两路,一路通过VGA 进行显示,另一路通过D/A 转换成模拟信号驱动致动器对目标进行控制。

图1 FPGA+DSP处理系统结构框架

2 系统定制与实现

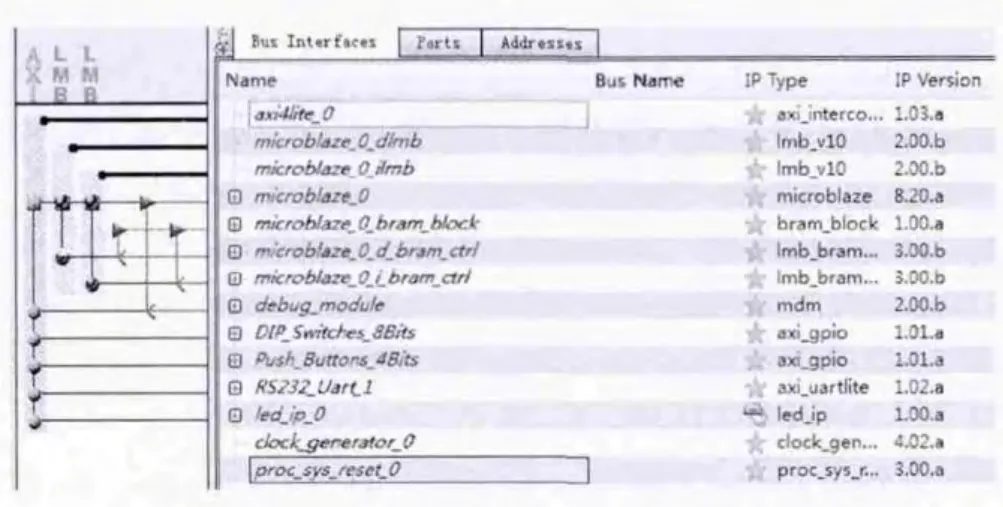

采用Xilinx公司的XPS和SDK 工具包进行基于FPGA的嵌入式开发,其中系统架构的搭建和外设IP核的设计在XPS中完成,板级支持包BSP 的创建和软件代码的设计在SDK 中完成。系统整体架构如图2所示,AXI总线控制器、DDR 控制器、RS_232 外设核等由XPS 的工具定制,而A/D 和D/A 的外设IP核和与DSP通信的外设IP核是采用XPS中外设向导添加的。

2.1 软核处理器的定制

MicroBlaze软核处理器的定制如图3所示,MicroBlaze采用指令和数据空间分离的哈佛结构,有32个32位通用寄存器,32位的地址总线可寻址空间4GB[8-10]。本设计中系统总线选用AXI System,时钟频率和参考时钟都为100 MHz,片上存储器由FPGA 内嵌的BRAM 组成,大小设定为8KB。在添加I/O 接口栏中添加LED_8bits、DIP_Switchs_4bits、RS_232,其中RS_232可用于系统调试和低速数据传输。对于I/O 设备的访问MicroBlaze处理器采用存储器映射的方式,本设计采用高级可扩展接口AXI4进行存储器访问。

图2 系统整体架构

2.2 DDR 控制器设计

差分形式的数据流在A/D 转换器的外设核内使用FPGA 原语将其转换成单端信号,然后通过自制的adc_to_ddr总线送往DDR 控制器中。其中adc_to_ddr总线是从AXI4总线中截取的一部分,使用IBA 核连接到两条总线上,然后用ChipScope Pro软件观察,可以发现AXI4总线中s_axis部分的时序和adc_to_ddr总线的一样。

由于数据流的速率非常快而且数据量大,如果采用指令或中断的方法来传输字节信息,会造成大量CPU 的资源被占用,同时也容易造成数据丢失,而对于DMA 传输方式,由于可以使外设和存储器不经过CPU 直接进行数据交换,且是由硬件电路直接实现,所以适用于本系统的高速数据传输[11,12]。

图3 MicroBlaze软核处理器的定制

在该控制器中先对数据流进行乒乓操作,其仿真结果如图4所示,然后触发DMA 控制器向CPU 发出DMA 请求,CPU 响应DMA 请求把总线控制权交给DMA 控制器并配置其存储地址和传送数据块长度等寄存器,执行DMA传送将数据流缓存到DDR2中,最后当DMA 操作结束后又把总线控制权交还给CPU。

图4 乒乓操作仿真结果

2.3 EMIF接口控制器设计

EIMF接口是DSP 的外部存储器接口,通过对寄存器的设置可以将其配置成同步、异步等类型的高速数据接口,可实现与外部存储器的无缝连接[13-16]。本系统采用同步类型的EMIF与FPGA 互连,通过在线逻辑分析仪可以观察EMIF接口时序,如图5所示。由于FPGA 和DSP 是跨时钟域系统,需在FPGA 中添加异步FIFO 进行数据缓存,其中写时钟为FPGA 读DDR 的时钟,读时钟由DSP 提供的ce、awe、aoe信号组成。

图5 DSP外设核的Analyzer仿真结果

在FPGA 和DSP 之间利用DMA 方式进行数据传输,有利于提高数据传输的吞吐量。FPGA 控制DDR 进行读写,在读操作下,当FPGA 内部FIFO 出现非空信号时,控制DSP的中断管脚触发全局中断,外部数据通过EDMA转存到DSP 内部的RAM 中,当数据传输完成后会触发EDMA 完成中断。数据在DSP中经复杂算法处理后将处理后数据缓存到内部RAM 中,再通过EDMA 方式经过EMIF接口将处理后的数据传回FPGA。

3 实验分析

本实验中DSP 芯片选用TI 公司的C600 系列TMS320DM642芯片,主频为600MHz,EMIF接口工作时钟为100MHz,数据总线宽度为64bit。FPGA 选用Xilinx公司的Spartan6系列的XC6SLX150T,内部软核处理器和AXI总线 的 工 作 频 率 为100MHz。A/D 选 用 双 通 道12bit 的ADC6222芯片,转换率为65MSPS;D/A 选用双通道16bit的AD9777芯片,转换率为160MSPS。系统上电后MicroBlaze软核对外设核进行初始化并配置A/D 和D/A 的寄存器,A/D的采样率采用50MHz,经模数转换后的数据流通过FPGA缓存和简单处理后发送给DSP进行复杂算法处理,处理后的结果如图6所示,最后将提取到的振动控制信息发送给FPGA,经D/A转换成模拟信号驱动致动器对目标进行控制。

图6 自由振动控制曲线

对5片40mm×20mm×0.5mm 的PZT 在致动器300V最大控制电压条件下进行实时采集控制,实验结果表明,该系统可将20g振动加速度下的振动幅值降低30%。

4 结束语

本文设计了一种FPGA+DSP 的振动主动控制系统,充分发挥了两者的优点,使速度和灵活性得到兼顾。在FPGA 内部采用基于MicroBlaze处理器和AXI4总线的可编程SoC系统设计,通过软硬件协同开发使系统的吞吐量得到了优化并缩短了开发周期。采用工作频率为400MHz的DDR2对数据流进行缓冲,解决了数据速率高且数据量大的问题,给复杂算法处理预留了足够的时间;在FPGA 内部设置乒乓操作,保证了FPGA 和DSP的协调工作,同时解决了不同时钟域的问题;FPGA 与DSP 之间使用DMA方式进行数据传输,提高了数据传输吞吐量。实验测试结果表明,该振动主动控制系统可以稳定可靠地工作。

[1]GUAN Tao.Design of active vibration controller based on FPGA and DSP [D].Harbin:Harbin Engineering University,2012 (in Chinese).[官涛.基于FPGA+DSP 的振动主动控制器的研制 [D].哈尔滨:哈尔滨工程大学,2012.]

[2]ZHOU Yi,ZHOU Qinggen,QIAO Peng,et al.design of micro SINS based on FPGA &DSP [J].Electronic Measurement Technology,2008,32 (2):119-122 (in Chinese). [周益,周清根,乔鹏,等.基于FPGA+DSP的微小型捷联惯导系统的设计 [J].电子测量技术,2008,32 (2):119-122.]

[3]WEN Yuchen.Design and implementation of GPS receiver based on FPGA and DSP [D].Chengdu:University of Electronic Science and Technology of China,2013 (in Chinese).[文雨辰.基于FPGA+DSP 架构的GPS 接收机设计和实现[D].成都:电子科技大学,2013.]

[4]LIANG Yuheng.High-precision data acquisition and DSP+FPGA high-speed signal processing hardware system design [D].Xi’an:XiDian University,2012 (in Chinese). [梁宇恒.高精度数据采集及DSP+FPGA 高速信号处理硬件系统设计[D].西安:西安电子科技大学,2012.]

[5]GAO Yang,LIU Rongke,HU Wei.Design and implementation of high definition video image system based on FPGA+DSP[J].Electronic Measurement Technology,2011,35 (1):69-73 (in Chinese). [高杨,刘荣科,胡伟.基于FPGA+DSP的高清视频图像系统设计与实现 [J].电子测量技术,2011,35 (1):69-73.]

[6]CHEN Wenhe,BI Xin,CAO Yunxia,et al.Design of radar data transmission interface between DSP and FPGA [J].Control Engineering of China,2011,18 (S1):60-62 (in Chinese).[陈文鹤,毕欣,曹云侠,等.FPGA 与DSP的雷达数据传输接口设计 [J].控制工程,2011,18 (S1):60-62.]

[7]LI Le,XIONG Zhihui,WANG Bin,et al.High-speed data communication between DSP and FPGA in embedded panoramic video processing system [J].Journal of Electronics &Information Technology,2010,32 (3):649-654 (in Chinese). [李乐,熊志辉,王斌,等.DSP+FPGA 折反射全景视频处理系统中双核高速数据通信 [J].电子与信息学报,2010,32(3):649-654.]

[8]LIU Yongjian.Soft-core embedded processor MicroBlaze [J].Computer &Network,2012,38 (15):64-66 (in Chinese).[刘永健.软核嵌入处理器MicroBlaze [J].计算机与网络,2012,38 (15):64-66.]

[9]WU Zhongzheng.Embedded system design based on MicroBlaze[D].Nanjing:Nanjing University of Science and Technology,2014 (in Chinese).[巫忠正.基于MicroBlaze的嵌入式系统设计 [D].南京:南京理工大学,2014.]

[10]WANG Ershen,ZHANG Shufang,ZHANG Zhixian.Study on embedded gps receiver based on Xilinx MicroBlaze [J].Communications Technology,2010 (10):28-30 (in Chinese). [王尔申,张淑芳,张芝贤.基于Xilinx MicroBlaze的嵌入 式GPS 接 收 机 研 究 [J].通 信 技 术,2010 (10):28-30.]

[11]MEI Kun,HU Shuling,LIU Honghai.High-speed data acquisition system of the radar based on FPGA and DSP [J].Electronic Design Engineering,2010,18 (12):159-161 (in Chinese).[梅坤,胡姝玲,刘宏海.基于FPGA 与DSP的雷达高速数据采集系统[J].电子设计工程,2010,18 (12):159-161.]

[12]DAI Shaosheng,NIU Daowei.Fabrication of uncooled infrared imaging system based on SOPC [J].Semiconductor Optoelectronics,2013 (1):126-129 (in Chinese). [代少升,牛道伟.基于SOPC 的非致冷红外热成像系统的研制 [J].半导体光电,2013 (1):126-129.]

[13]LUO Ming.DSP control system design based on EMIF interface[J].Light Industry Science and Technology,2013,30(4):82-83 (in Chinese).[罗鸣.基于EMIF接口的DSP控制系统设计 [J].轻工科技,2013,30 (4):82-83.]

[14]ZHANG Feng,REN Guoqiang,WU Qinzhang.Design of high-speed image transmission system based on EMIF [J].Semiconductor Optoelectronics,2011 (1):146-149 (in Chinese).[张峰,任国强,吴钦章.基于EMIF 的高速图像传输系统设计 [J].半导体光电,2011 (1):146-149.]

[15]FANG Dong,ZHANG Guobao.Design of data acquisition system based on EMIF [J].Electronic Design Engineering,2011,19 (2):174-178 (in Chinese).[方冬,章国宝.基于EMIF接口的数据采集系统的设计 [J].电子设计工程,2011,19 (2):174-178.]

[16]ZHOU Shunyan,WU Dan.TMS320C6713DSP EMIF interface design and realization of high speed data exchange board[J].Computer Measurement & Control,2010,18 (7):1654-1656 (in Chinese). [周 顺 燕,吴 丹.TMS320C6713 DSP的高速EMIF数据接口设计与实现 [J].计算机测量与控制,2010,18 (7):1654-1656.]