基于Encounter的低功耗时钟树综合研究

2015-12-20冯万鹏纪应军宋志鹏

冯万鹏,王 鸥,纪应军,宋志鹏

(西南技术物理研究所1部,四川成都 610041)

随着集成电路工艺节点的不断提高,芯片的工作频率越来越高,对芯片的低功耗要求也越来越高,现在的工艺尺寸可缩减到20 nm、16 nm或更小,先进的工艺技术可提高集成电路器件集成度及生产出更大的芯片尺寸,但同时意味着时钟网络的负载越来越重并可能穿过更长的距离。随着时钟网络越来越复杂,时钟网络的功耗占整个芯片高达约50%。所以,为了降低整个芯片功耗,可从降低整个时钟网络的功耗着手,本文将介绍门控技术在时钟网络的应用,以及多阈值电压的器件在时钟网络的应用,并最终讨论了不同驱动能力的缓冲器和反向器对整个时钟网络功耗的影响。

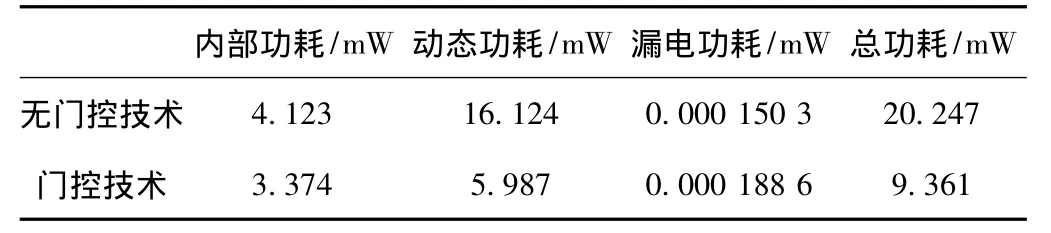

1 门控技术

芯片中动态功耗较大一部分是消耗在时钟网络,甚至超过50%的动态功耗是消耗在时钟树的缓存器上的。这是由于时钟树缓存器具有最高的翻转率,数量过多,且为了减少时钟树的延时,时钟树缓冲器通常具有较强的驱动能力。此外,在触发器时钟信号接收端接收到时钟信号时,即使触发器的数据输入端和输出端保持不变,也会消耗一些动态功耗。减少时钟树上动态功耗的最常用方法是在无需时钟信号时将时钟关断。该种方法就是所谓的门控时钟技术[1-2]。现在的综合设计工具支持门控时钟技术的自动化流程,工具可自动识别门控时钟单元,并在不改变电路逻辑功能的前提下,将门控时钟单元插入到电路中根据门控时钟单元插入的位置不同,门控时钟技术又分为粗粒度门控时钟和细粒度门控时钟。粗粒度门控时钟技术就是将门控时钟单元插入到整个模块的时钟输入端,而细粒度门控时钟技术则是将门控时钟单元插入到模块中每个寄存器的时钟输入端。相对而言,粗粒度门控时钟技术虽控制粒度不如细粒度门控时钟技术,但其能节省芯片的面积,并减少了过多门控时钟单元引入的功耗。因此,粗粒度门控时钟技术应用更为普遍。

实验数据表明,在添加了门控时钟技术后,芯片的面积减少了约20%,功耗根据不同的操作条件节省了30%~40%;其面积节省是由于单个的门控时钟单元取代了多个选择器;其功耗节省是芯片的部分电路采用了门控时钟技术;其结果是在实际的芯片上,处理器处于闲置状态时测量得到的。且其对比了将时钟门控单元插在时钟树不同位置上所得出的功耗分析结果,发现时钟门控单元越靠近时钟根节点,节省的功耗越多,且面积也越小。

图1 门控技术示意图

表1 无门控技术和门控技术的功耗

2 多阈值电压

当工艺制程下降到20 nm或更低的工艺节点时,使用多阈值电压工艺库成为减少泄露功耗的一种常用方式。亚阈值泄露功耗与阈值电压相比呈指数关系增长,延时也同样依赖于阈值电压,但依赖关系明显弱于亚阈值泄漏功耗。目前而言,工艺厂商会提供3种类型的标准单元:低阈值电压标准单元(LVT)、标准阈值电压标准单元(SVT)和高阈值电压标准单元(SVT)。综合工具和后端实现工具会充分利用以上标准单元来同时优化时序和功耗。在利用多阈值电压[3]工艺库进行综合时,其首要目标就是降低高速高泄漏低阈值电压晶体管的使用,只有当需满足性能时序的情况下才会使用。通常默认情况下,工具在达到最低的性能指标后方会进行功耗优化。实际上,对不同需求的模块,可进行不同的设置来决定优先处理某个标准单元库。若一个模块中的路径处于整个芯片的关键路径上,可先采用高性能低阈值标准单元库进行综合,然后对于非关键路径上的标准单元替换成相应功能的低性能高阈值标准单元。由此,既可满足能要求,又可降低芯片的泄露功耗。相反,若对一个模块的性能要求较低,而功耗要求较高,则可优先采用高阈值电压标准单元库进行综合,然后根据性能要求对关键路径上的标准单元使用低阈值电压标准单元进行替代。图2表示器件的阈值电压与泄露电流、延时的关系图。

图2 泄露电流和延时关系图

表2 LVT、SVT和HVT的特性

从表2可看出,LVT类型的cell具有驱动能力强、器件延时小、速度快及灵敏度高的高性能指标,但又因泄露电流大导致功耗大的缺点;SVT性能次之;HVT类型的cell具有驱动能力小、器件延时大、速度慢,且灵敏度低的低性能指标,但却有泄露电流小带来功耗低的优点;故在选择器件时,要权衡器件性能和功耗。

选用一个音频芯片做完preCTS并存储DataBase,使用Cadence CCOPT引擎做时钟树,使用相同驱动能力(X8)的缓冲器,分析 LVT、SVT、HVT下的功耗情况。

表3 8X驱动能力缓冲器LVT、SVT、HVT的功耗

实验数据表明,LVT的各功耗指标比SVT大,SVT的各功耗指标比HVT大。时钟树综合通常用到缓冲器和方向器,如何选择缓冲器和反相器在时钟树综合始终存在争议。以TSMC 20 nm工艺库为列,在同一类型的缓冲器和反相器条件下,分析使用不同驱动能力大小的缓冲器和方向器对整个时钟功耗的影响。

3 基于功耗优化的时钟树综合

3.1 CMOS电路中的功耗分析

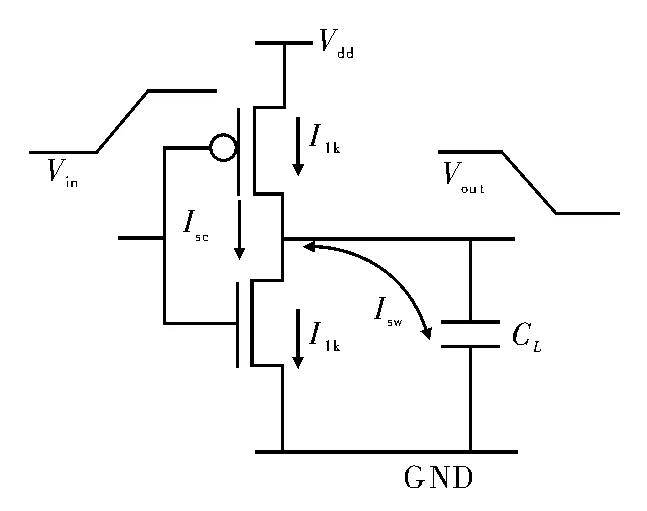

CMOS 电路中,功耗有4 种来源[5],PTotal=PDynamic+PLeakage+PShort-circuit+PDC,PDynamic动态功耗主要来源于开关的功耗,即对输出电容进行充放电所消耗的功耗;PLeakage由两部分组成,一部分是MOSFET开关的非理想动态特性所引起的亚阈值功耗,另一部分是载流子隧道效应通过栅氧化层导致的栅极泄露功耗;PShort-circuit是CMOS晶体管栅极的上拉和下拉打开时的输入信号跃迁所产生的瞬态功耗,PDC是CMOS电路在低电压摆幅输入信号驱动时所消耗的静态直流功耗。

图3 CMOS电路的功耗示意图

与此同时,当前EDA工具对功耗的评估公式为

式(1)中,PInternal由标准门单元的短路功耗和PShort-circurt标准门单元内部节点充放电功耗 PInternal-switch两部分组成

其中,VDD为电源电压,TR为信号在单位时间内的翻转次数,CL为负载电容

其中,VDD为电源电压;ILeakage(i)为漏电流;每个cell的ILeakage(i)是固定的,且与信号翻转速度无关。

3.2 功耗优化方案及结果

时钟树综合有3种方法[4]:使用反相器、使用缓冲器以及二者结合使用。在具体的设计中,采用反相器还是缓冲器来构建时钟网络进行时钟树综合,始终是个有争议的问题。本次优化的目的是在满足时序的前提下,尽可能地降低时钟网络的功耗,因此分别采用反相器和缓冲器的方法进行时钟树综合,选出最优方案。

表4 1X-16X驱动能力缓冲器功耗

从 library中选用 1X,2X,4X,6X,8X,10X,12X,16X驱动能力的缓冲器。从表4中可看到,随着驱动能力的增大,时钟树的功耗越来越大,同时无时钟树占整个芯片的功耗也在不断增大从22.19%增加到29.56%。根据DRV violation可看出,选用驱动能力在6~12驱动的能力缓冲器较为合适,在该驱动能力的缓冲器DRV的violation较低。

表5 1X-16X驱动能力反向器功耗

从 library中选用 1X,2X,4X,6X,8X,10X,12X,16X驱动能力的反方向器。从表5中可看到,随着驱动能力的增大,时钟树的功耗越来越小,同时无时钟树占整个芯片的功耗也在减小从57.5%减小到33.83%。根据DRV violation可看出,选用驱动能力在6~12驱动的能力方向器较为合适,在该驱动能力的缓冲器DRV的violation较低。

表6 8X驱动能力反相器和缓冲器功耗

从library中选用8X驱动能力的反相向和缓冲器器,从表6中可以看出,只选用缓冲器向器的功耗最小,缓冲器和反相器混用功耗次之,而只选用反相器的功耗最大。

4 结束语

使用门控技术可有效节省时钟树上的功耗,同时也可节省芯片的功耗及面积。代工厂提供的HTV、SVT、LVT 3 种类型的 cell[6],在保证时序收敛的情况下,使用HVT替代LVT来达到降低时钟树上的功耗的目的,在使用同一类型的缓冲器和反相器时,可单一地选用缓冲器,也可单一选用反相器,还可将缓冲器和反相器同时使用,无论选择哪种使用方式,均可保证在无DRV的情况下,使得功耗最低。

[1]孙佳.信息安全芯片的低功耗后端设计研究[D].上海:复旦大学,2012.

[2]谢晓娟,蒋见花.一种基于门控时钟的低功耗电路实现方案[J].电子器件,2010,33(2):154 -157.

[3]石玉龙,张立超,柏露.ASIC后端设计中低功耗时钟综合的方法[J].信息通信,2009(4):24-26.

[4]潘静,吴武臣,侯立刚,等.ASIC物理设计中的时钟树综合优化研究[J].微电子学,2011,41(6):872 -875.

[5]王昌林,张勇,李东生.CMOS集成电路功耗分析及其优化方法[J].舰船电子工程,2006,6(3):123 -125,166.

[6]Michael Keating,David Flynn,Robert Aitken Alan G,et al.Kaijian shi low power methodology manual for system-onchip design[M].Berlin:Springer Press,2007.