基于DM8148的视频处理系统设计

2015-12-18陈彦化

陈彦化,李 晃,巩 峰

(西安电子科技大学电子信息攻防对抗与仿真技术教育部重点实验室,陕西西安 710071)

随着我国安防产业迅速崛起,高清摄像机逐渐得到普及,促使当代安防系统逐步向高清晰度、高智能化转变。但由于高清智能视频监控系统所要处理的数据量庞大,使得目前多数的嵌入式处理器均难以应对。基于这种需求,本文设计了基于DM8148的高清视频处理平台以满足高清视数据处理的需求。

1 基于DM8148视频处理系统硬件结构

本高清视频处理系统以TI公司出品的TMS320DM8148视频处理器为核心,辅以各种外设接口。图1为系统硬件结构框图,整个系统主要分为[1]:采集模块、视频处理模块、外部存储器模块和电源模块。

2 采集模块

采集模块主要由丹诺高清摄像机DN-HDC20-CN、一个DVI输入接口和Silicon Image公司的 SiI1161[2]芯片组成。SiI1161的PD用于控制整块芯片的电源供给,当PD为高电平时,芯片正常工作;当PD为低电平时,芯片的所有输出引脚输出为高阻态。

图1 视频处理器结构框图

由图2[3]可知,从DVI接口输入的 TMDS差分信号对直接输入到SiI1161中,为防止干扰,在差分信号上接入一个10 kΩ的电阻到地;图中U7(24C02A)为EDID存储器(128 Byte),存放DVI接口所对应的显示格式、分辨率等显示属性数据,再由信号源端通过DDC信道读取。右侧 QE[0:23]直接与DM8148的VIN0信号输入引脚相连。

图2 采集模块电路

3 视频处理模块

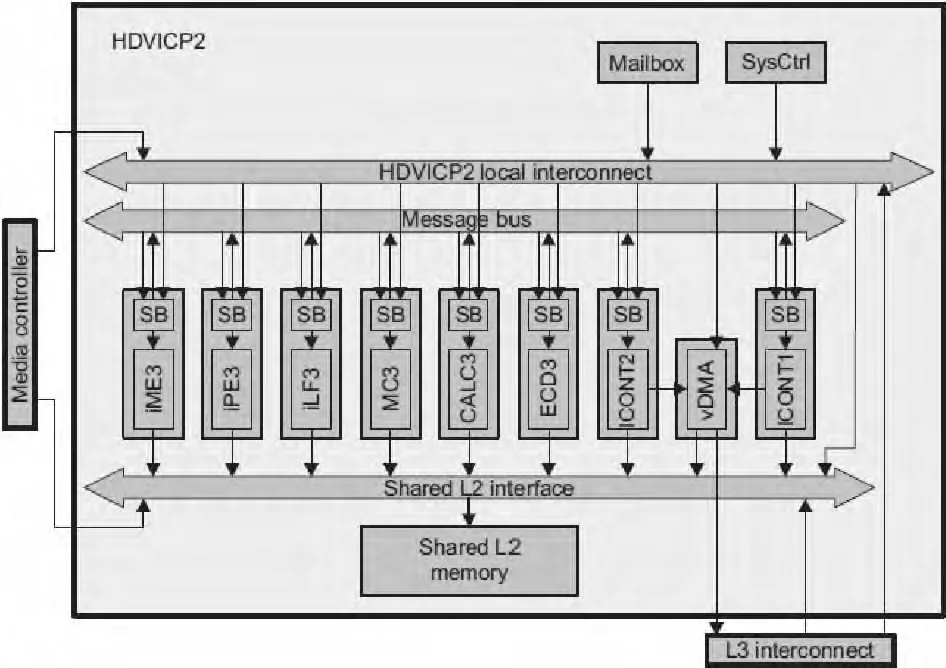

系统的视频处理模块[4]主要由C674xDSP、高清视频处理子系统HDVPSS和高清视频协处理器HDVICP2[5]3部分组成。

VPSS的视频输入接口支持 RGB、YUV422和YUV420的数据存储格式。采集模块采集到的24位RGB信号可通过VPSS的VIP0被接收。之后,VIP0所支持的可编程颜色空间转换将24位RGB信号转化为YCbCr信号,即YUV信号,具体设计为YUV422。

RGB输入视频数据转换完成后,将YUV422数据流送入VPSS的主通道(Primary Pipelines)。VPSS的主通道采用内置包含一三维动态自适应去隔行扫描器和一无边界自适应缩放器的算法,专门用于处理视频以产生全高清视频输出。在对YUV422做去隔行和缩放处理后,通过回写通道0(write back 0)将数据流发送到指定的外部存储器DDR3中。

VPSS上的处理流程完成后,ARM端应用程序调用C674xDSP中添加OSD信息的算法为视频加上文字信息。

图3为HDVICP2的基本框图[7],HDVICP2与VPSS有一块256 kB共享内存,其局域互连功能保证其各个模块与媒体控制器互连,并可通过L3 Interconnect与其他外部模块如Cortex A8、外部存储器互连,从而完成接收指令和读取数据的任务[6]。

图3 HDVICP2基本框图

当DSP上的工作完成后,A8端应用程序通过符合xDM(eXpress DSP Digital Media)标准的 API调用HDVICP2对同时通过DMA传送到HDVICP2中的视频进行H264编解码操作。

4 外部存储器模块

4.1 SDRAM模块

DM8148芯片内部有 32 kB的一级程序缓存,32 kB的一级数据缓存和256 kB的程序数据共享二级缓存。但对于实时视频图像采集处理系统是不够的,因此需要对系统的数据存储器空间进行外部扩展。系统扩展了两片DDR3(MT41J128M16JT-125)同步动态数据存储器[6](SDRAM),数据总线均为16位,共512 MB。

DM8148片上带有两个外部存储器扩展接口EMIF0和EMIF1,数据总线宽度均为32位。DM8148通过EMIFs访问外部存储器。

从片内资源有效地将数据移动到外部DDR3SDRAM器件时,DDR3内存控制器即EMIF使用了一个命令FIFO,一个写数据FIFO,一个回传命令的FIFO和两个读数据FIFO。图4显示了EMIF的FIFO框图,命令、写数据、读数据到达EMIF并行地与对方交互。而用来写和读外部存储器以及内部存储器映射寄存器中的数据采用的是同一条外围总线。

图4 EMIF的FIFO框图

命令的FIFO存储所有来自OCP命令接口的命令;写数据的FIFO存储来自OCP写数据接口的写入数据;回传命令的FIFO存储所有将发给OCP的回传接口的回传事务。两个读数据的FIFO存储将被送至OCP回传接口的数据;一个读数据FIFO存储读自内存映射寄存器的数据;另一个读数据FIFO存储从外部存储器中读取的数据。

4.2 NAND Flash模块

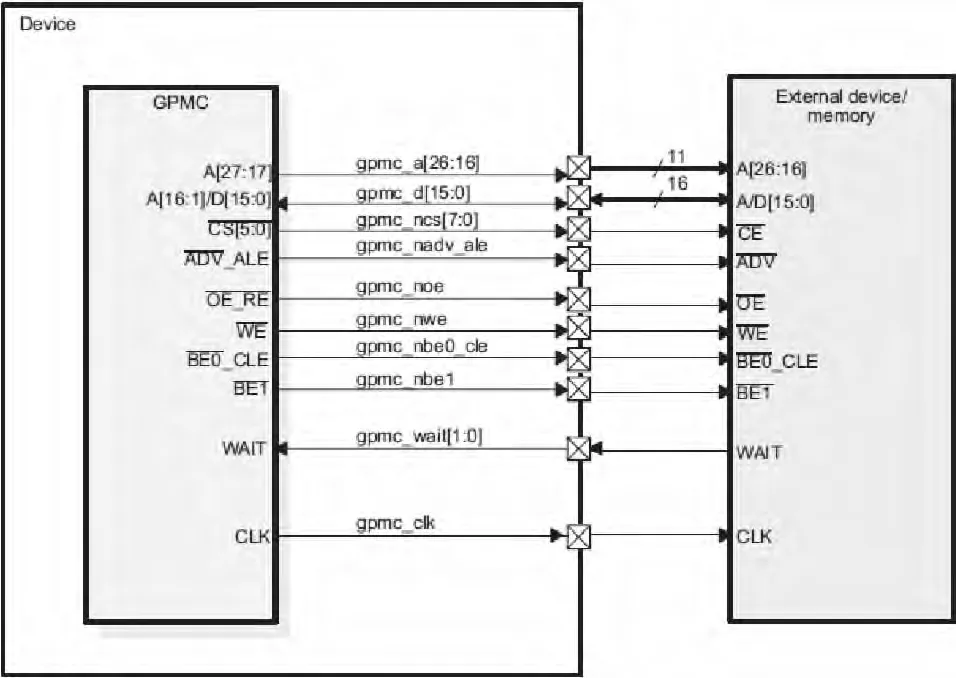

系统需要对程序的运行代码进行存储,且DM8148片上无掉电不丢失的程序存储器,所以必须扩展。系统的程序存储器选用的是Flash芯片,该芯片较EPROM存储数据更快速、容量更大、且具有掉电不丢失数据、在线可编程、拥有足够多的擦除次数等优点。图5为GMPC与外部存储器NAND Flash的连接示意图。

图5 GMPC与外部存储器NAND Flash的连接示意图

NAND[9]设备的数据读取和写入访问均是通过一个读完成或写请求给芯片选择相关的存储区域或通过一个读或写请求给GPMC_NAND_DATA_i(其中i=0~5)寄存器所在位置。GPMC_NAND_DATA_i不是真正的寄存器,而是一个地址位置,使能RE或WE信号控制。

从GPMC_NAND_DATA_i位置或者从相关芯片选择存储区域读取数据,将激活一个异步读访问。记录数据到GPMC_NAND_DATA_i位置或相关的芯片选择存储区域写数据,则将会激活一个异步写访问。

5 应用程序设计

应用程序由多个链接组成,主要链接有:捕获链接、去隔行链接/尺寸调节链接、显示链接、编码器连接、解码器链接、算法链接、空链接、IPC位输入/输出和帧输入/输出链接。图6为系统数据流图,可从中直观地看出各个链接间的关系。

链接是视频数据流处理过程中的基本单元,其中包含一个BIOS6/Linux线程和一个消息盒子,消息盒子允许用户应用程序和其他链接与其所在的链接交互。由于每个链接作为单独的线程运行,所以多个链接可并行。每个链接均创建了一个专用的接口以允许其他链接与该链接交换视频帧或比特流。一旦一条链接开始运行,ARM端应用程序可向链路中的链接发送命令以控制其运行状态,如改变输出显示的马赛克分布,但命令或是中断并不是必须的。

图6 数据流图

应用程序调用Link API(链接应用编程接口)创建、控制链接,构成一条数据流的链路:CaptureLink→DEILink→SclrLink→NsfLink→IpcOutM3Link→IpcInDSPLink→OsdAlgLink→IpcOutDSPLink→IpcInVidLink→EncLink→IpcOutVidLink→IpcInA8Link→IpcOutA8Link→IpcInVidLink→DecLink→IpcOutVidLink→SWMosaicLink。

应用程序的链接各自实现了不同的功能,其既是一个独立的模块,也是一个不可分割的整体,通过各个链接组成的链路可清晰明确地控制和显示出系统的数据流。

6 结束语

介绍了高清视频获取和综合处理平台设计与实现。该平台采用TMS320DM8148,依靠DM8148处理器和外围设备、接口来完成经DVI接口的视频图像数据的抽取。然后将采集到的视频数据通过VIP0口送入VPSSM3做去隔行、尺寸调节、去躁处理再到DSP添加OSD并将数据送往Video M3进行编解码,最终通过HDMI接口输出。经测试,系统符合设计指标要求。但由于系统的数据率较高,处理器和外围负载多,开发难度大。因此,本系统难免存在局限性和有待完善的部分,该系统可在以下方面进行改进:尝试使用多线程软件编程的方式进行应用程序的编写;对输入信号的改进,输入音视频混合数据进行外理,音视频分别处理后再整合输出。

[1]王文俊.基于双处理器架构的视频服务器的设计与实现[D].武汉:华中科技大学,2008.

[2]Texas Instruments.TMS320DM814x DaVinciTM数字媒体处理器[M].Texas:Texas Instruments,2012.

[3]SREEDHARA K.TI DM8148原理图[EB/OL].(2011-10-19)[2012-10-15]http://wenku.baidu.com.

[4]张兴华.基于TMS320DM6446的视频实时处理系统的研究与开发[D].北京:北京交通大学,2010.

[5]张琦,苏苑新.基于达芬奇技术的数字视频系统设计与实现[J].微计算机信息,2008(24):183-185.

[6]刘丹,孙丽云,胡伟,等.基于DM642的视频处理系统设计[J].DSP开发与应用,2007(6):157-159.

[7]Texas Instruments.TMS320DM814x DaVinci digital media processors technical reference manual[M].Texas:Texas Instruments,2011.

[8]王强.基于DM642的多路视频采集及传输系统[D].保定:河北大学,2011.

[9]伍令杰.基于TMS320DM641的视频监控系统硬件研究与实现[D].成都:西南交通大学,2007.