基于RocketIO的FPGA互连研究及应用

2015-12-18席鹏飞范晓星

席鹏飞,范晓星,冉 焱

(西安电子科技大学电子信息攻防对抗与仿真重点实验室,陕西西安 710071)

随着现代数字处理技术和计算机技术的不断发展,实时处理复杂系统采集到的大容量数据成为可能。一个大型的数据采集系统,需要采集成百上千个实时数据,数据的高速、实时、可靠传输是一个关键技术[1]。而传统的并行传输技术已接近理论极限,仍不能满足要求,因此高速串行传输技术正在成为主流。在实际设计中,采用现场可编程门阵列(FPGA)实现高速串行接口是一种性价比较高的技术途径[2-3]。

RocketIO是Xilinx公司FPGA芯片内部集成的可编程高速串行收发器。本文主要介绍了Virtex-6 LXT以及Virtex-5 FXT中的RocketIO GTX版本,提出了设计要点,并实现了FPGA之间的通信并给出了采样波形图。

1 RocketIO收发器

RocketIO是Xilinx公司内嵌的可配置高速串行收发器,串行传输速度在 600 Mbit·s-1~ 6.6 Gbit·s-1[4]。由于Virtex-5与Virtex-6系列内嵌的GTX结构、工作原理基本相同[5-6],故本文以 Virtex-6 GTX 为重点进行介绍。

1.1 RocketIO主要特点

(1)每个通道收发器支持从 600 Mbit·s-1~6.6 Gbit·s-1的全双工传输速率。(2)收发器内嵌发送时钟生成电路和接收时钟恢复电路。(3)支持可编程差分输出电压摆幅(110~1 130 mV)和可编程预加重。(4)收发器支持直接和交流耦合方式,可兼容多种高速接口标准。(5)片内集成可编程差分终端电阻。(6)支持片内多种环回测试模式。(7)支持8B/10B编码,可编程边界检测符(Comma),提供对多种标准协议的支持。

1.2 RockerIO主要组成部分

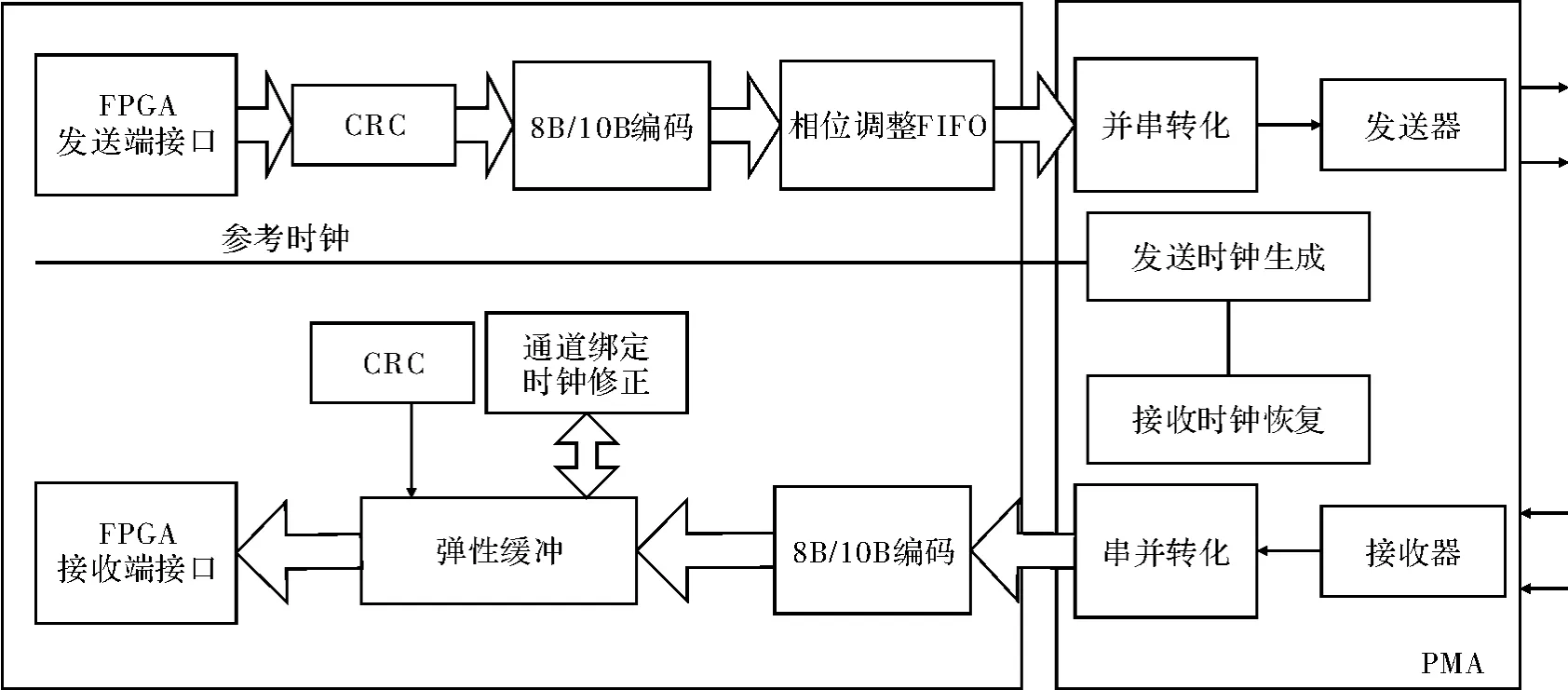

一个完整的RocketIO收发器主要包括PMA(物理媒介适配层)和PCS(物理编码子层)两个子层,如图1所示。

图1 RocketIO收发器内部结构示意图

其中PMA部分主要包括串行器和解串器、发送和接收缓冲区、高速时钟产生器和线路时钟恢复单元;PCS部分主要包括8B/10B编解码、弹性缓冲区和CRC32校验。

(1)8B/10B编解码。RocketIO收发器采用标准的8B/10B编码机制将8位字符转化为10位字符,保证了良好的直流平衡特性,有利于交流和直流耦合和时钟恢复。

(2)串行器和解串器。在发送端,收发器把输入GTX的参考时钟作20倍频,作为发送线路的参考时钟,然后将经过编码的并行数据转化为串行数据,从串行差分端发送出去;在接收端,时钟恢复电路从比特流中提取出时钟相位和频率,恢复出接收时钟,将串行数据解码并转化为并行数据,送入用户接口以进行其他操作。

(3)CRC校验。CRC循环冗余检测用于对被接收数据的出错检测,RocketIO收发器CRC检测逻辑支持32位常量 CRC,被用于如 Gigabit Ethernet、Fibre Channel、Infiniband、User-defined 等通信模式[7]。

2 RocketIO设计要点

要达到RocketIO模块的最佳性能,需考虑诸多设计因素,本文针对在设计过程中遇到的具体问题展开讨论。

2.1 参考时钟

为满足高速数据通信的需求,GTX收发器必须具备高性能和低抖动的参考时钟。一般GTX收发器提供了3种参考时钟的驱动方式:(1)由外部晶振直接驱动GTX专用时钟路由得到。(2)从相邻Quard的专用时钟路由获取;(3)从FPGA内部获取。

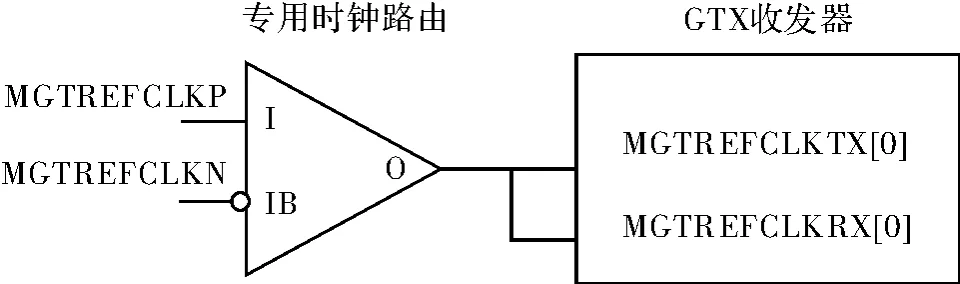

每个Quad拥有两个专用差分参考时钟输入MGTREFCLK0[P/N]、MGTREFCLK1[P/N],它们用于连接到外部时钟源。要使用这些参考时钟,必须对原语IBUFDS_GTXE1进行实例化。用户设计必须将IBUFDS_GTXE1的输出连接至GTXE1的端口MGTREFCLKTX[0]、MGTREFCLKRX[0]。需要注意的是,即使在设计中未使用 TX PLL,MGTREFCLKTX[0]仍需要被连接[5],单个外部参考时钟用法如图2所示。

图2 单个外部参考时钟用法

前两种参考时钟的驱动方式的本质都是使用GTX专用时钟路由,而第3种方式是通过FPGA全局时钟网络,会引入更大的抖动,因此在实际应用中不推荐使用。

2.2 用户时钟

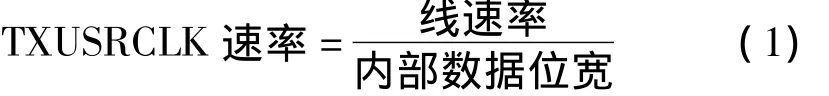

FPGA的发送端接口包括TXUSRCLK和TXUSRCLK2两个时钟。其中TXUSRCLK2是GTX收发器发送端的用户时钟,允许用户直接使用,由GTX的内部时钟TXOUTCLK驱动。用户将并行数据传输到发送接口,在用户时钟上升沿被采样并送入发送缓冲,经过编码以及串行化后发送出去。TXUSRCLK是PCS内部逻辑时钟,不允许用户直接使用,其大小取决于

由于选择了8B/10B编码方式,故16 bit并行数据在GTX内部传输时为20 bit。在双字节模式中,需要设置属性 GEN_TXUSRCLK=TRUE。此时,TXUSRCLK端口必须降低,逻辑时钟TXUSRCLK由GTX内部提供,并且用户时钟TXUSRCLK2大小与TXUSR-CLK相同。根据线速率3 Gbit·s-1,可以计算出用户时钟TXUSRCLK2为150 MHz。其时钟结构示意图如图3所示。

图3 TXOUTCLK驱动TXUSRCLK2(双字节模式)

FPGA的接收端接口情况类似,包括RXUSRCLK和RXUSRCLK2两个时钟。其中,RXUSRCLK2是GTX接收端的用户时钟,由恢复时钟RXRECCLK驱动。RXUSRCLK的驱动方式和属性设置与发送端一致。

2.3 Comma检测

GTX收发器接收端有可编程的Comma检测机制,可以实现双字节符号的检测[8]。接收器在输入数据流中搜寻Comma字符,若找到,解串器就调整序列边界可以匹配检测到的Comma字符序列,且扫描是连续进行的,一旦对齐后,后续的所有数据均已对齐。则要求在任意的序列组合里,Comma字符必须唯一。

常用的控制字符有 K28.1、K28.5,设计选择K28.5。发送数据时,应先发送足够数量的K字符序列以保证通信链路的成功建立和接收端的对齐,实际设计中发送至少2 000 K字符即可,然后再发送数据部分。发送端发送K字符序列时,赋值TXCHARISK=2'b01,TXDATA=16'h43BC。其中TXCHARISK低位赋值为1表明对应数据的低字节为K字符,对应比特流中的Comma字符。注意,当设置TXCHARISK=2'b11,TXDATA=16'hBCBC时,在接收端存在可能错位8位的情况,如图4所示。

图4 Comma检测出错情况

这是因为在发送的K字符序列中,前一个K字符的低字节和后一个K字符的高字节恰好组合为一个新的K字符。如果接收端依据这个伪K字符进行对齐操作,则后续所有数据均会错位8位。而当设置TXCHARISK=2'b01时,则不会出现这种伪对齐的情况。

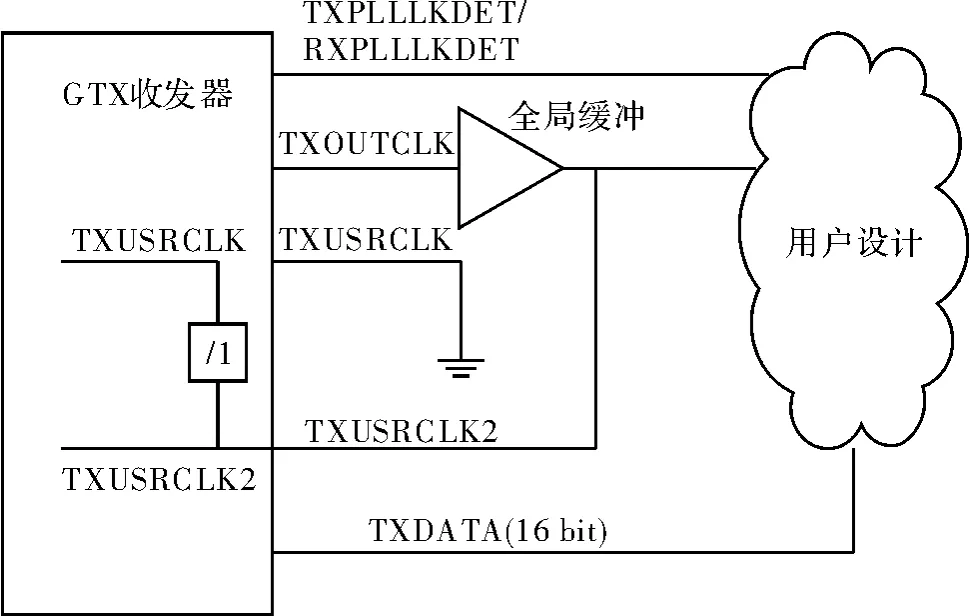

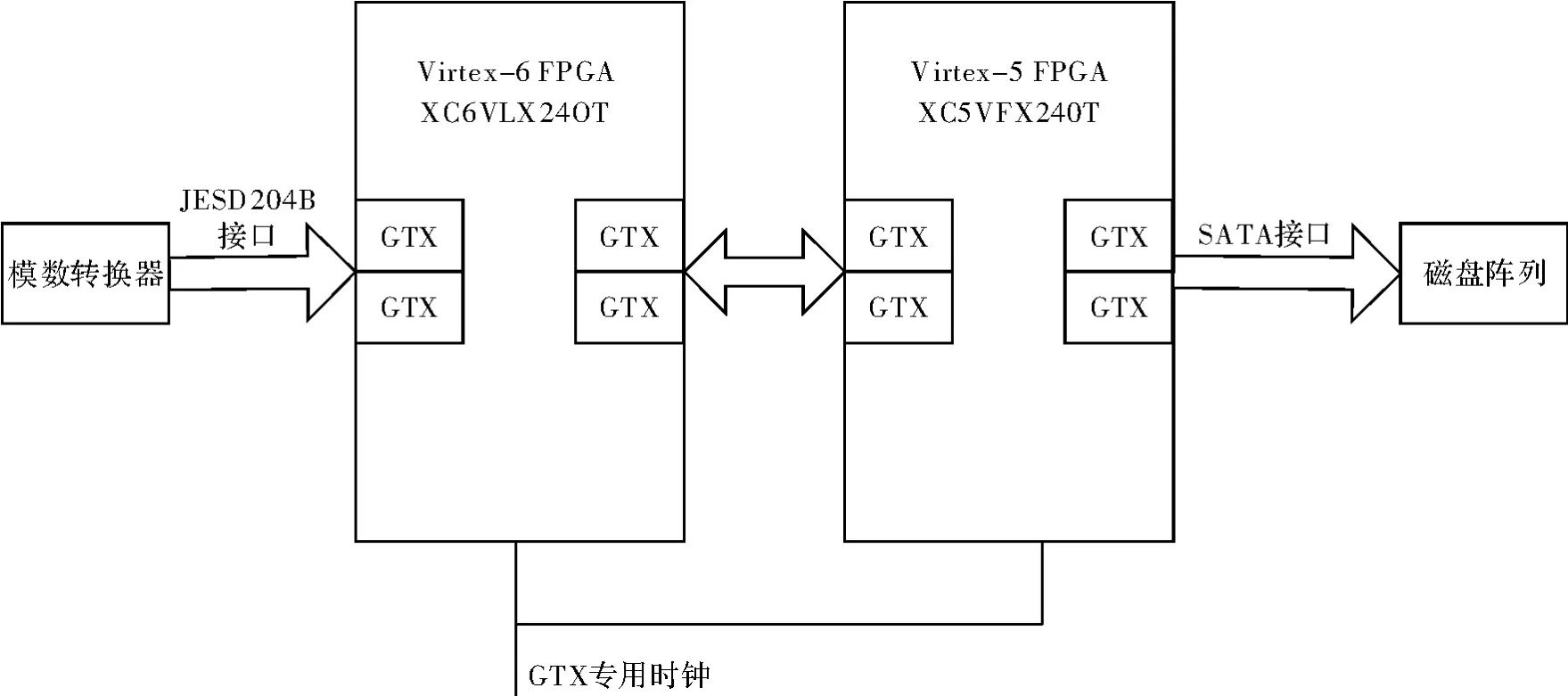

3 系统架构

本文构建了一个高速数据采集存储系统,FPGA分别选择Xilinx公司Virtex-6系列的XC6VLX240T和Virtex-5系列的 XC5VFX240T。采用 GTX实现FPGA之间数据的传递,其中,参考时钟150 MHz,数据位宽 16 bit,传输速率 3 Gbit·s-1,系统架构如图 5所示。

图5 高速数据采集存储系统架构

高速数据采集存储系统由模数转换器、FPGA、磁 盘阵列、时钟芯片等几个部分构成。其中,GTX收发器被配置成不同的协议接口以适应数据传输。模数转换器将采集到的高速数据通过GTX送入Virtex-6 FPGA内部,经过处理后再通过GTX传递给Virtex-5 FPGA,然后再通过GTX存入磁盘阵列。可见,RocketIO收发器是数据传输的核心。

4 实验结果和分析

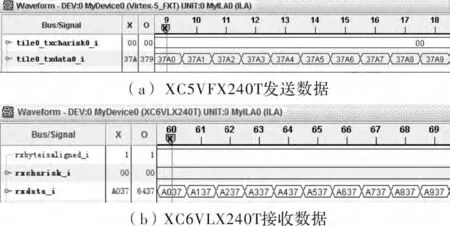

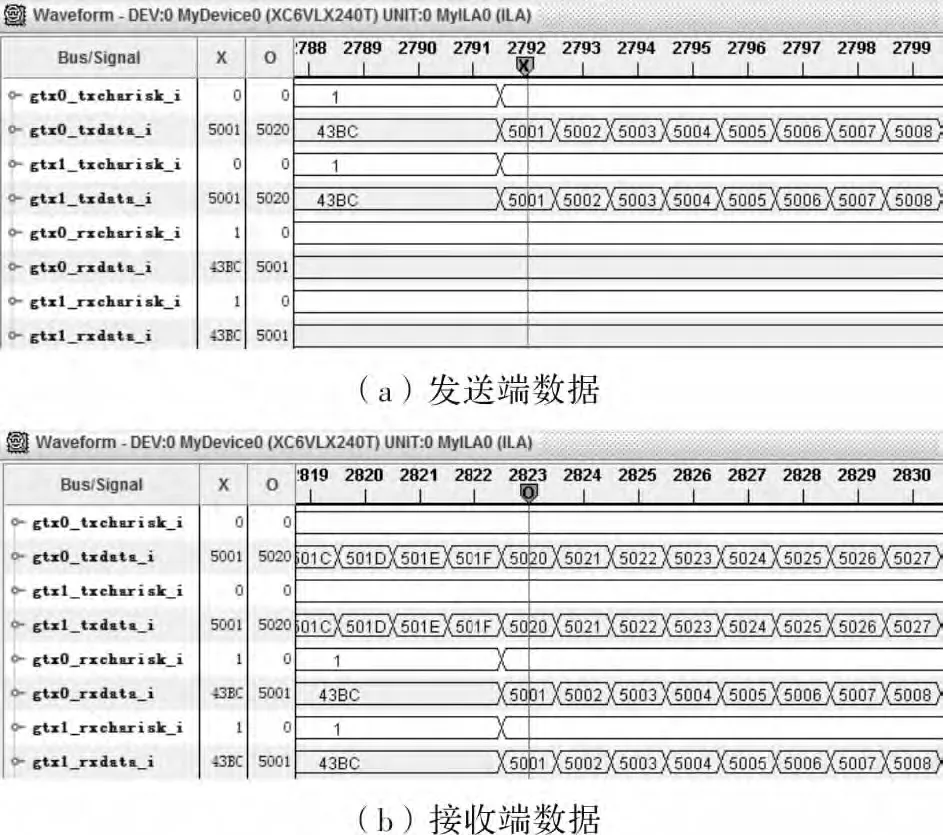

本文实现了高速数据在FPGA之间的传输。为测试方便,采用XC6VLX240T GTX的远端PCS环回模式进行测试。Chipscope采样波形如图6所示。

图6 XC6VLX240T远端PCS环回测试

由于远端PCS环回模式可以同时测试两端GTX的通信情况,所以由图 6可知,XC6VLX240T和XC5VFX240T可以正常通信。

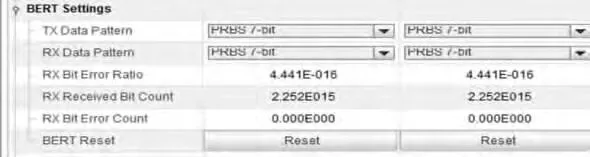

IBERT即集成式比特误码率测试仪,是Xilinx专门用于具有高速串行接口的FPGA芯片的调试和交互式配置工具[9]。使用IBERT测试GTX通信质量情况,配置MGT/IBERT选项,选取测试时间3 600 s,其测试结果如图7所示。在测试期间没有出现误码,设计满足高速数据的可靠传输要求。

图7 GTX误码情况

5 结束语

本文介绍了Xilinx公司Virtex-6系列FPGA集成的RocketIO收发器的原理和设计实现。可以看出,利用RocketIO进行高速数据的串行传输,可以在较大程度上简化物理层和链路层之间的数据连接,并提高了芯片之间信号传递的速度和可靠性,这对于提高高速数据采集存储系统的整体性能是有利的[10]。

[1]田耕,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2012.

[2]李大鹏,陈长胜,王世奎,等.基于FPGA的高速串行传输接口研究与实现[J].航空计算技术,2008,38(2):100-103.

[3]杜旭,于洋,黄建.基于FPGA的高速串行传输接口的设计与实现[J].计算机工程与应用,2007,43(12):94-96.

[4]Xilinx Conpration.Virtex-6 family overview[M].USA:Xilinx Conpration,2012.

[5]Xilinx Conpration.Virtex - 6 FPGA GTX transceivers user guide[M].USA:Xilinx Conpration,2011.

[6]Xilinx Conpration.Virtex - 5 FPGA GTX transceivers user guide[M].USA:Xilinx Conpration,2011.

[7]李江涛.RocketIO高速串行传输原理与实现[J].雷达与对抗,2004(3):48-50.

[8]张守将.基于RocketIO的高速数据传输系统研究[D].西安:西安电子科技大学,2013.

[9]徐妍,马丽珍,张丽.IBERT在 FPGA中的应用[J].电子科技,2012,25(7):103 -105.

[10]王向阳,赵艳杰.Gbit·s-1试验系统中高速串行接口的设计与实现[J].现代电子技术,2008(22):4-7.