基于混合原型平台的UART IP核设计与验证

2015-12-16赵新超彭智聪

赵新超,陈 岚,冯 燕,彭智聪

(中国科学院微电子研究所,北京 100029)

基于混合原型平台的UART IP核设计与验证

赵新超,陈岚,冯燕,彭智聪

(中国科学院微电子研究所,北京 100029)

传统的软硬件设计方法已无法满足SoC快速验证的应用需求。针对此现状,阐述了虚拟平台与硬件平台相结合的混合原型验证技术,主要介绍了UART IP混合验证方案,分析了UART IP核协议、功能模块设计以及FPGA平台搭建,最后通过构建虚拟平台和编写测试脚本,对IP核进行混合原型验证。验证结果表明,该IP核复用性好,完全可以应用于SoC设计中。

UART IP核验证;混合原型平台;硬件原型;虚拟原型

0 引言

随着片上系统(System on Chip,SoC)设计复杂度的增加,验证过程也变得更加复杂。传统的软硬件设计方法是在软硬件划分之后,软件和硬件同步进行设计,直到硬件(指芯片或开发板)完成后才可以与软件集成测试;如果此时发现软件或者硬件设计中存在缺陷需要重新修改设计时,势必增加设计周期,影响产品的上市时间。所以,当前迫切需要一种在硬件流片之前,便可以对SoC设计进行软硬件协同验证的方法。混合原型验证便是很好的解决方案。

混合原型验证是虚拟原型与硬件原型相结合的一种验证技术,通常情况下,SoC设计由硬件设计和软件设计两部分组成,硬件设计主要采用寄存器传输级(Register Transfer Level,RTL)代码实现,软件设计主要在中央处理器(Central Process Unit,CPU)中实现,并通过加载Linux内核、编译驱动和应用程序来控制硬件与外界进行交互。混合原型验证是两者功能相结合的一种验证方法,可以进行软硬件协同开发与调试。下面介绍混合原型验证平台的设计方法,并以 UART IP核为例,详细阐述其验证过程和验证结果,为IP核设计用户提供一种新型的验证方案。

1 混合原型验证平台

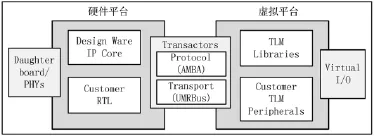

如图1所示,混合原型验证平台由硬件平台和虚拟平台两部分组成,两者之间通过高速接口 Transactors (XACTOR)互联。其中硬件平台基于HAPS(High-performance ASIC Prototyping System,HAPS)原型验证系统实现,平台中有一款容量高达 450万门的 Virtex-6 LX760 FPGA (Filed Programmable Gate Array),可以为用户提供较大容量的RTL验证;虚拟平台主要由一套完善的开发工具包组成,在添加虚拟模型时,通过引入已经搭建好的虚拟软件开发包,为软件开发人员将虚拟原型演变为一套现成可用的参考开发工具[1];XACTOR接口通过高速总线UMRBus(Universal Multi-Resource Bus)进行数据传输[2],UMRBus是一种高性能、低延时通信总线,它能为所有板载FPGA、存储器、寄存器和其他资源提供连接功能,其传输协议基于 AMBA(Advanced Microcontroller Bus Architecture)协议实现。

图1 混合原型验证平台示意图

1.1硬件平台

HAPS原型验证系统由一套 HAPS-61高性能 ASIC原型验证平台和一套复杂的支撑软件组成,支撑软件包括:Certify FPGA代码分割工具、Synplify FPGA综合工具、Xilinx ISE布局布线工具、Confpro下载工具以及 I-dentify在线调试工具。HAPS-61原型验证系统的主要特点包括:容纳高达450万门的门级电路;843个用户I/O接口;12个外部差分时钟输出;一个100 MHz的晶振,2个PLLs能够产生高达700 MHz的时钟频率;可配置的电源网络;高速UMRBus数据传输。

1.2虚拟平台

与传统RTL级验证相比,虚拟平台的验证建立在电子系统级(Electronic System Level,ESL)之上,运用 SystemC库和 TLM 2.0标准,可以进行快速的系统建模,仿真速度比RTL高很多。虚拟平台是由一套虚拟软件开发包(Virtualizer Development Kits,VDK)组成,可以提供软件的调试、分析和仿真功能,凭借 ARM Cortex处理器的高性能模型、基于AMBA协议的总线以及DesignWare IP,开发者可以方便地将其基于ARM处理器的设计分割到虚拟平台和硬件平台中。在虚拟平台中单独仿真时,通过搭建已经验证好的TLM模型,用户可以脱离硬件进行仿真;在与硬件进行协同仿真时,通过引入TLM Library,然后在TLM Creator中模拟PHY或测试设备,再把模拟好的 I/O模型映射到基于FPGA的硬件原型 HAPS上,最后通过HAPS端口连接真实的外部世界,从而实现软件和硬件之间的协同开发,加快了系统开发进度。

2 UART IP核混合验证方案

2.1整体方案设计

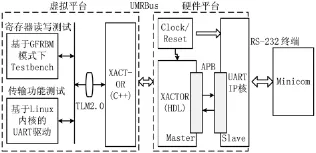

为了验证已经设计好的UART IP核,构建如图2所示的混合验证方案。图中,中间部分为HAPS硬件平台,包含了全部FPGA硬件实现,其中UART IP核是自主设计的基于 APB(Advanced Peripheral Bus)接口的待验证IP核,XACTOR是由本系统提供的接口IP,两端分别通过APB总线连接UART IP核,再通过UMRBus高速总线连接虚拟平台;Clock/Reset是由 HAPS提供的时钟和复位模块。左半部分为虚拟平台,通过基于标准TLM2.0的XACTOR接口,用户可以访问硬件单元,从而实现基于事务级模型的协同仿真。虚拟平台中事务级建模测试方法可以由2种方法实现:基于GFRBM(Generic File Reader Bus Master)模式的Testbench输入和基于Linux内核的UART驱动加载,分别可以对硬件RTL中的寄存器读写功能和IP核数据传输功能进行测试。右半部分为连接RS-232串口的超级终端,通过Minicom工具来观测IP核数据收发的正确性,进而协助虚拟平台完成整个系统验证[3]。

图2 UART IP核混合验证方案

2.2UART IP核设计

2.2.1UART协议

UART接口是计算机串行通信广泛使用的接口,包含了 RS-232、RS-422、RS-485等串口。本设计采用Verilog来开发符合 RS-232标准的 UART IP核。UART传输只需要两条信号线(RXD,TXD)就可以完成数据的相互通信,接收与发送是全双工实现。其工作原理是将传输数据的每个字符进行编码,一位接着一位的传输,传输的速率由波特率时钟控制[4]。其中各比特的意义如图3所示。

图3 异步串行通信协议数据传输模式

起始位:低电平信号发起,表示传输字符开始;

数据位:起始位后紧接着数据位,位数由7~8位构成一个字符,由时钟控制从低位开始传送;

奇偶校验位:数据位加上这一位后,得出“1”的位数为偶数或者奇数,以此来校验数据传输的正确性;

停止位:可以是 1位、1.5位、2位的高电平,是一个数据帧结束的标志;

空闲位:处于高电平状态,表示当前线路上没有数据传送,若空闲位后出现低电平,则表示下一个数据帧的起始位。

2.2.2功能模块设计

为了简化IP核设计,在具备基本异步串行收发功能的前提下,去掉了Modem控制器功能模块。IP核内部设计结构如图4所示,主要由波特率发生模块、线路状态与控制模块、接收模块、发送模块、接收 FIFO模块、发送 FIFO模块、中断控制模块等组成[5]。

各模块之间的工作关系如下:当发送数据时,APB总线把数据写入发送FIFO中,当发送移位寄存器是空时,先由发送逻辑根据线路状态对数据进行配置,即在数据头部加上起始位,在数据尾部加上奇偶校验位和停止位,然后把数据压入到发送移位寄存器中,最后在发送时钟的控制下,通过Data_out线把数据发送出去;接收数据时,在接收时钟的控制下,串行数据通过Data_in线逐位送入接收移位寄存器中,当检测到停止位时,数据被转换为并行数据并送入接收FIFO模块中,并被总线读取,后面进入空闲状态,等待下一次任务。

图4 UART IP核内部设计结构图

线路状态与控制模块通过地址选通信号锁存片选信号和地址信号,当片选信号有效时,锁存读、写选通信号,当检测到读或写的数据到来时,进行相关寄存器操作。

中断控制模块要求当任何中断发生时,中断使能寄存器根据中断优先级的不同,允许对应的中断发生。UART IP核的中断申请可以分为4个优先级,从高至低的顺序为:INT0(接收器状态错误),INT1(接收数据准备好),INT2(发送器空),INT3(Modem控制中断)。

2.2.3构建UART IP核的FPGA工程

设计完基于APB接口的UART IP核后,为使虚拟平台能够通过UMRBus总线访问IP核,需要把IP核添加到顶层文件包含UMRBus高速接口的FPGA工程中。该功能模块是由例化的XACTOR实现,XACTOR是由本平台提供的接口IP,主要通过AMBA协议实现软件平台与硬件平台之间的数据传输,每一个 XACTOR由一个CAPIM(Client Application Interface Module)组成,系统总共提供了5类 XACTOR供用户使用:APB、AHB、AXI、GPIO、INT。用户需要根据自己设计的IP核接口类型,选择对应的XACTOR添加到自己的工程中,然后修改相应的端口、时钟、reset信号等,从而产生包含UMRBus高速接口的FPGA工程。

2.3虚拟平台设计

2.3.1搭建虚拟平台

本方案需要在虚拟平台中创建虚拟模型,并分别搭建能够对硬件RTL寄存器读写功能测试和对IP核数据传输功能测试的虚拟平台。其中,对硬件RTL寄存器读写功能测试的虚拟平台如图5所示。图中,i_GFRBM_TLM2作为事件发起方(Initiator),通过连接 tlm2bus总线,可以与硬件平台进行操作;i_ClockGenerator是虚拟时钟产生模块,为总线和 Initiator提供时钟单元;i_ResetGenerator是虚拟模型复位模块,提供系统的复位功能;i_TlmTarget2UmrAMBA和i_IntInitiator2Umr是基于SystemC实现的并与硬件 CAPIM相对应的 XACTOR,通过标准的TLM2.0 Socket接口,实现软件平台与硬件平台的数据交互功能。

图5 进行寄存器读写操作的虚拟平台

2.3.2设计脚本

虚拟平台搭建完成后,需要在i_GFRBM_TLM2中写入测试脚本访问硬件寄存器,以测试IP核寄存器设计是否正确。在 GFRBM模式下,Testbench采用标准的STL 2.0(Socket Transactor Language)语言实现,STL是由OCPIP(Open Core Protocol International Partnership)组织提出的标准Socket语言,主要由3个不同的子集组成:

(1)Basic commands:基于单指令任务的控制传输模式;

(2)Macro statements:采用短指令的突发传输序列;

(3)Behavioral statements:用户自定义控制指令。

根据本设计需要,UART IP核可以被访问的寄存器名字和地址如表1所示。

表1 UART可访问寄存器名称及地址

可访问的寄存器确定完成后,采用STL语言编写测试脚本,示例如图6所示。

图6 基于STL语言的测试脚本

3 验证过程与结果分析

混合原型验证方案中,对IP核进行混合验证之前,首先需要使用仿真器对RTL代码进行仿真。当仿真通过之后,才可以在硬件平台上进行混合原型验证。硬件实现时,首先采用 Certify工具进行代码分割,再使用Synplify工具进行代码综合,然后使用ISE工具进行布局布线并产生可加载的.bin文件,最后使用Confpro工具配置硬件系统。当硬件系统配置完成后,按照图2所示的方式进行连接,并启动虚拟平台开始混合原型验证。

3.1寄存器读写功能测试

在虚拟平台中通过GFRBM模式对UART IP核进行寄存器读写访问时,参照 2.3.1节中搭建的虚拟平台和2.3.2节中给出的测试脚本,分别采用固定值读写和随机数读写两种方式测试寄存器,结果如下:

(1)固定值读写测试:分别对表1给出的寄存器写入固定值0x0000、0x5555、0xaaaa、0xffff,然后读取该寄存器的值。经对比,读出值与写入值完全一致。

(2)随机值读写测试:分别对表1给出的寄存器写入随机值$random,然后读取该寄存器的值。经对比,读出值与写入值完全一致。

3.2UART数据传输测试

与寄存器读写功能测试不同,在测试UART IP核的传输功能时,首先仿照 2.3.1节的方法,构建包含处理器IP核模型的虚拟平台,然后在虚拟平台中加载ARM® CortexTM处理器 IP模型,并编译 UART软件环境,包括操作系统、驱动以及应用程序等。测试时,首先在虚拟平台中对IP核进行传输配置,包括传输速率、数据位、奇偶校验等,并把发送数据通过IP核发送到TXD端口,再通过串口传送到上位机超级终端进行显示;接收数据时,超级终端发送数据至IP核的RXD端口,虚拟平台读取IP核接收的数据,然后把数据在虚拟平台中打印出来,从而确定IP核传输功能的正确性。下面分别采用单端发送和回环传输两种方法进行测试。

(1)单端发送测试:即从虚拟平台发送数据,通过UART IP核传送至超级终端 Minicom,在 Minicom中显示发送的数据是否正确。虚拟平台中,对UART IP核数据传输协议配置如下:传输速率9 600 b/s、8 bit数据、无校验位、1 bit停止位,同样在 Minicom中配置相同的传输参数。经测试,Minicom接收的数据与发送数据完全一致。测试结果如图7所示。

(2)回环测试:即从虚拟平台发送数据,通过 UART IP核传送至 Minicom,Minicom接收到数据后,再把接收到的数据发送至UART IP核,虚拟平台读取 IP核接收的数据,然后在虚拟平台显示窗口进行收发数据对比,以此确定回环传输的正确性。同样在虚拟平台和 Minicom中配置如下参数:传输速率 9 600 b/s、8 bit数据、无校验位、1 bit停止位。经测试,虚拟平台接收的数据与发送数据完全一致,从而确定整个通路传输是正确的。

图7 虚拟平台发送数据和Minicom接收数据示意图

4 结论

本文介绍了基于虚拟平台与硬件平台相结合的混合原型验证技术,并以UART IP核为例,对设计过程进行分析并对结果进行验证。由于采用了混合原型验证技术,使得SoC设计人员在开发早期便可发现设计的缺陷或故障,进而改进系统的功能和性能,降低开发风险。另外,本方案开发的IP核完全采用 Verilog语言设计,移植性好,其接口采用标准的APB总线接口协议,所以不需要用户进行修改,便可很好地应用于SoC设计中,具有较高的应用价值。

[1]Nithya Ruff.SoC设计:虚拟原型成为主流[J].电子产品世界,2013(1):25-27.

[2]UMRBus Communication System Handbook.2012,V3.14 [DB/OL].http://www.synopsys.com.

[3]吴君钦,李艳丽.一种SoC软硬件协同验证方法的设计[J].江西理工大学学报,2011,32(3):65-68.

[4]朱勤,钱敏.嵌入式 UART的设计及FPGA验证[J].通信技术,2012,45(241):150-153.

[5]董大成,张建东,史国庆.基于FPGA的 UART IP核的设计与实现[J].计算机测量与控制,2012,20(8):2251-2253.

Design and verification of UART IP core based on hybird ptototyping platform

Zhao Xinchao,Chen Lan,Feng Yan,Peng Zhicong

(Institute of Microelectronics of Chinese Academy of Sciences,Beijing 100029,China)

So far,the hardware and software design in traditional method is unable to meet the application requirements of fast SoC verification.In this situation,the mixed prototyping verification technology is provided which comprised of the virtual platform and the hardware platform.This paper mainly introduces the hybrid verification scheme of UART IP,analysis of the UART IP core protocol,the design of function modules,and the establishment of FPGA platform.Finally,the UART IP core is verified in hybird prototyping method by constructing a virtual platform and writing testsbench.According to the verification results,the IP core is of good reusability and can be applied in SoC design.

UART IP core verification;hybird prototyping platform;hardware prototype;virtual prototype

TN402

A

10.16157/j.issn.0258-7998.2015.10.009

(2015-02-15)

赵新超(1981-),男,硕士研究生,助理研究员,主要研究方向:集成电路IP核标准、SoC混合原型验证。

陈岚(1968-),通信作者,女,博士生导师,研究员,主要研究方向:超深亚微米芯片设计方法学及计算机体系结构,E-mail:chenlan@ime.ac.cn。

冯燕(1980-),女,硕士研究生,助理研究员,主要研究方向:IP核标准与 IP核共性技术。

中文引用格式:赵新超,陈岚,冯燕,等.基于混合原型平台的 UART IP核设计与验证[J].电子技术应用,2015,41 (10):39-42.

英文引用格式:Zhao Xinchao,Chen Lan,Feng Yan,et al.Design and verification of UART IP core based on hybird ptototyping platform[J].Application of Electronic Technique,2015,41(10):39-42.