基于FPGA的斜面冲击机末速度测试方案

2015-12-15王琳

王琳

(西安铁路职业技术学院 陕西 西安 710016)

基于FPGA的斜面冲击机末速度测试方案

王琳

(西安铁路职业技术学院 陕西 西安 710016)

为了评定运输包装件在受到水平冲击时的耐冲击强度和包装对内装物的保护能力,本文作者广泛研究的基础上基础上特别提出了一种基于FPGA的斜面冲击机末速度测试方案,经过作者实际测试表明此设计方案具有一定的实用性,达到了预期的结果,并且具有较高的灵活性,可靠性及稳定性,且价格低廉,有很大的实用价值和推广意义。

FPGA;斜面冲击机;末速度;保护;可靠;价格低廉

斜面冲击机主要由斜面钢轨道、安装试品的台车、牵引小车、挡板组成。主要通过牵引小车通过牵引机构将台车在斜面任意位置上自由释放,试品与台车在静止到冲击前无相对作用,在冲击时试品与台车能自由移动,最终试品与挡板冲击。此试验用于评定运输包装件在受到水平冲击时的耐冲击强度和包装对内装物的保护能力。GB/T4857.11水平冲击试验(斜面冲击、吊摆试验)要求需要确定量值的因素包括水平速度、包装件状态、包装件冲击面的外形、使用附加的障碍物。在要求中最主要的测量数据就是水平速度。

1 总体方案

斜面冲击机的结构如图1所示,其冲击末速度的测量一般采用单片机系统或嵌入式系统,单片机系统虽然价格低廉,使用方便,但是程序较易跑飞,且编程及修改较为麻烦,而嵌入式系统中基于CPU的嵌入系统价格较贵。而由于可编程逻辑器件(FPGA)具有丰富的可编程性与丰富的I/O引脚,使得它在数字系统中的应用越来越广泛[1],如同自行设计集成电路一样,可节省电路开发的费用与时间[2]。因此本文就提出了一种基于FPGA的斜面冲击机末速度测试方案。

图1 斜面冲击机示意图Fig.1 Schematic diagram of inclined impact machine

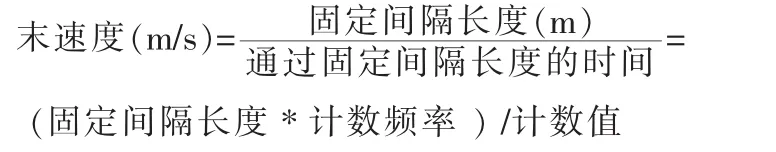

当试品随台车在斜面任开始意位置上自由释放后,在重力作用下做匀加速运动,也就是说从释放试品到试品与挡板接触,冲击速度始终在变化,因此需要采用近似测量,假设试品接近冲击末端时通过固定间隔长度的速度恒定,记录下通过固定间隔长度的时间,即可计算出试品的冲击末速度,末速度计算公式如式一所示[3]。

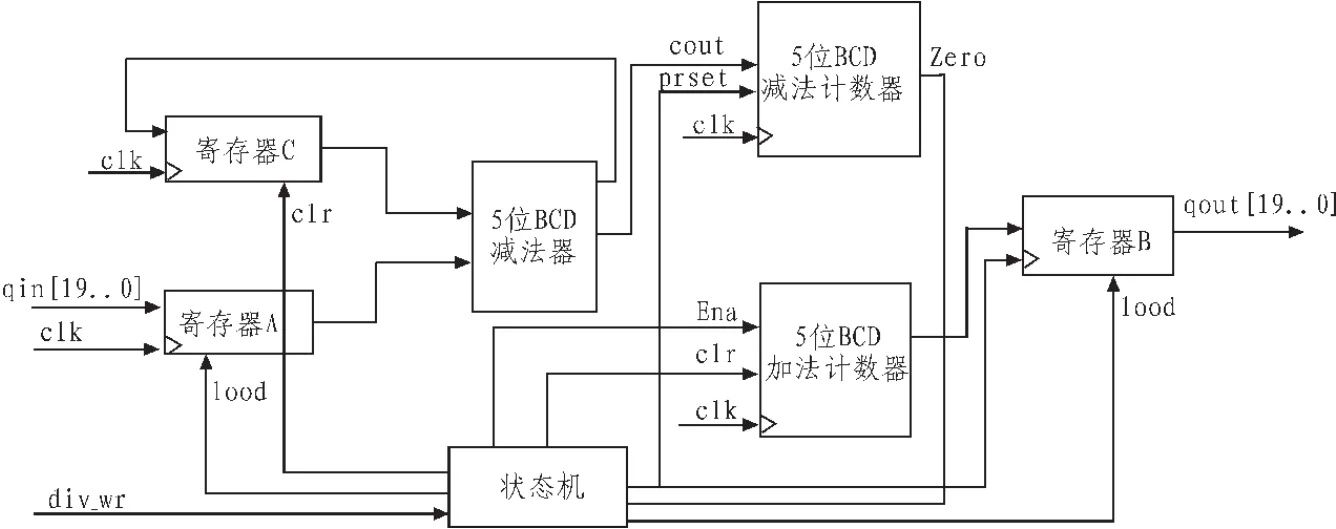

固定间隔长度的选取和通过时间的记录就是测量的关键,一般有两种做法,其一在冲击末端安装两个间距100 mm至200 mm光电传感器,记录反光板通过两个传感器的时间,即两个脉冲上升沿之间的时间;其二在冲击末端安装一个光电传感器和在滑动小车上安装固定宽度的反光板,记录反光板通过传感器的脉冲宽度。本方案选用第二种做法,其一,安装一只传感器可以通过降低间隔长度可以降低通过间隔长度两端速度变化量,更加逼近实际的末速度;其二由于减少了一只传感器可以降低成本,提高系统可靠性及维护性,另外通过提高计数频率与计数值来减小测量误差。当确定下固定间隔长度和计数频率后,末速度就等于一个常数除以计数值,系统方案如图二所示,动作控制按钮产生动作电平输入FPGA,FPGA根据相应的电平变化发出继电器控制信号,控制系统进行挂钩、上升、冲击等动作,在冲击末端由计数器模块完成计数,随后触发除法器模块计算常数除以计数值,最终通过显示模块输出信号,将末速度显示在数码管上[4]。

图2 系统硬件实现组成框图Fig.2 The hardware system block diagram

主控芯片选择 ALTERA Cyclone的 EP1C3T144,该FPGA基于SRAM架构,90个IO口,3 000个逻辑单元,还有13条M4K RAM(共6.5Kbyte),另外还有一个数字锁相环具有很高的性价比。

2 主要模块功能

2.1 计数模块

计数模块电路如图3所示。当按下冲击按钮后,shock置为0,将计数器BCDCOUNT清零,试品随台车从静止开始加速,到达冲击末端时,安转在台车上的反光板触发光电传感器,并输出一个宽度随冲击速度变化脉冲,在脉冲高电平期间将与门打开,计数器计数,脉冲高电平消失后计数完成,脉冲的下降沿反向后触发一个D触发器,产生DIV_WR的上升沿信号,读取计数值和启动除法器信号。考虑到精度与系统容量,我们将输入晶振12.288M经30分频后得到计数频率409.6K,计数器将计数值转换为5位BCD计数值,供除法器运算。

当最高速度4.0 m/s时,计数值约为4 096,1个计数脉冲引起的误差约为0.2%

当最低速度0.8 m/s时,计数值约为20 480,1个计数脉冲引起的误差约为0.03%

图3 计数模块示意图Fig.3 Schematic diagram of the counting module

可以满足速度误差要求。

2.2 除法器模块

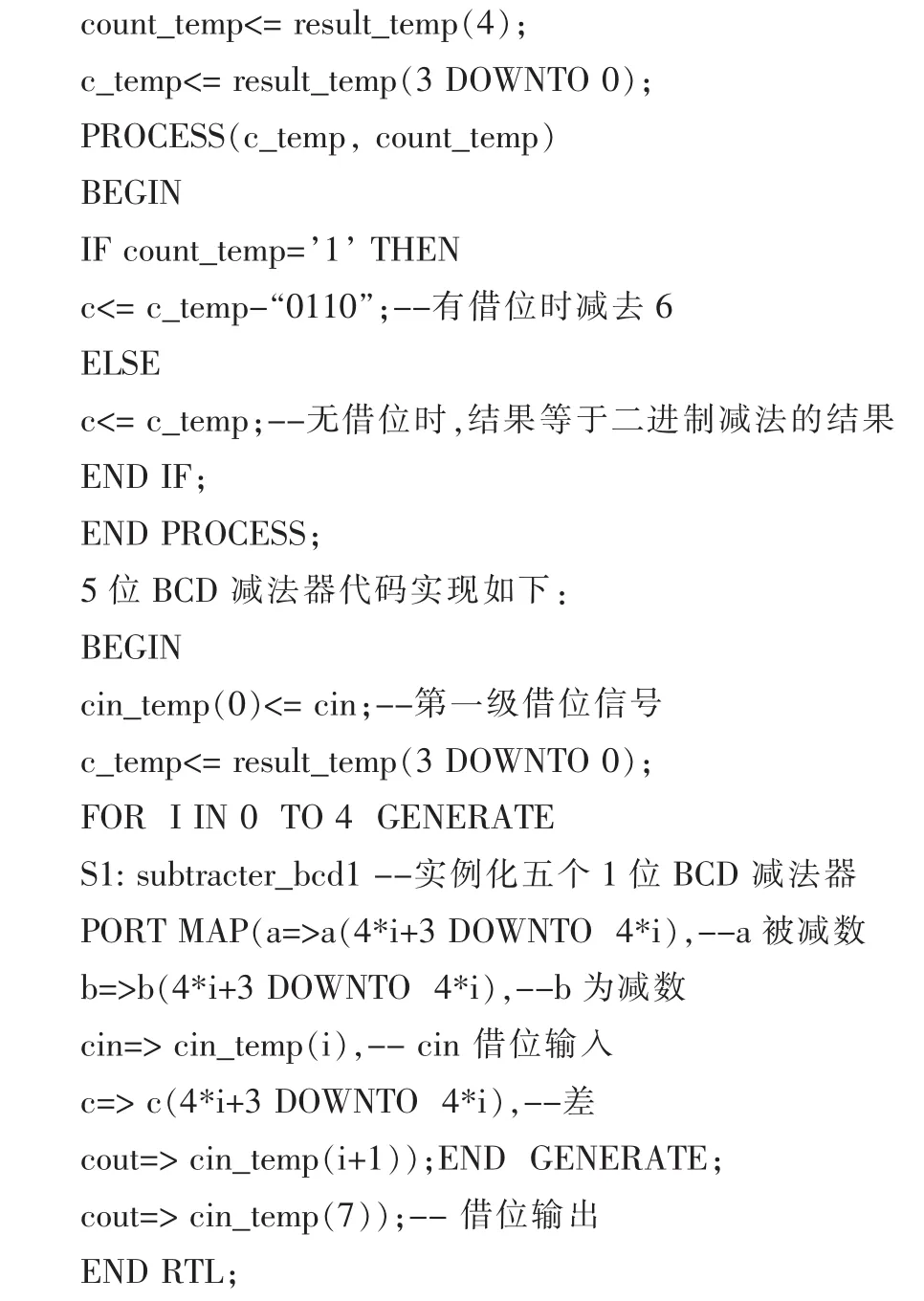

除法器模块的任务是完成计数值的倒数。由于除法器的输入和输出都是20比特信号,采用组合逻辑逻辑电路来实现该除法器将消耗很多资源,同时由于冲击试验间隔时间较长,除法器的计算速度没有必要很快,为此采用运算速度较慢的时序逻辑除法器电路,其基本思路为除法运算总可以用减法运算来实现。式一中取反光板宽度0.04 m,计数频率409 600 Hz,末速度将为(214/计数值),相当于计算214减去多少次计数值没有发生借位。实际上做减法时,数值的变化总发生在低5位的BCD数上,高5位的BCD数只是提供借位给低5位的BCD数,因此设计了一个5位BCD减法器、一个5位BCD减法计数器 来保存计数器的高5位的BCD数、一个5位BCD加法计数器用于保存做过的减法运算的次数。这种除法器的单次运算时间等于做减法的次数与晶振时钟周期的的乘积,即位商与晶振周期的乘积,其运算时间可以控制在1 s内,满足显示速度要求。 其结构图如图4所示。

状态机控制整个电路,负责给出其它模块的控制时序,在状态S0时,寄存器A并行加载数据,寄存器C和5位BCD加法计数器清零等,接着转移至状态S1;在状态S1时不断的做减法运算,直到被减数小于零,zero信号变为高电平,标志着减法运算结束,转移至状态S2;在状态S2把5位BCD加法计数器的至并行加载到寄存器B中[5]。

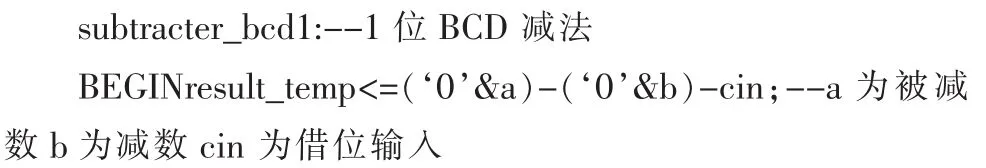

5位BCD减法计数器与5位BCD加法计数器实现较为简单,实现重点在于5位BCD减法器,其实现思路是5位BCD减法器由五个1位BCD减法器级联得到,而1位BCD减法由4位二进制减法来实现,当被减数大于减数时,1位BCD减法的结果与4位二进制减法的结果一样;当被减数小于减数时,1位BCD减法的结果等于4位二进制减法的结果再减去6,其代码实现如下[6]:

图4 除法器模块示意图Fig.4 Divider module

2.3 译码及显示模块

显示时采用5个七段的数码管,分别对应寄存器B输出5位的BCD数。在硬件上将所有的七段数码管的公用8条数据线,控制线独立连接至FPGA,利用时分原理和人的视觉暂留效应,对数码管进行动态扫描显示。

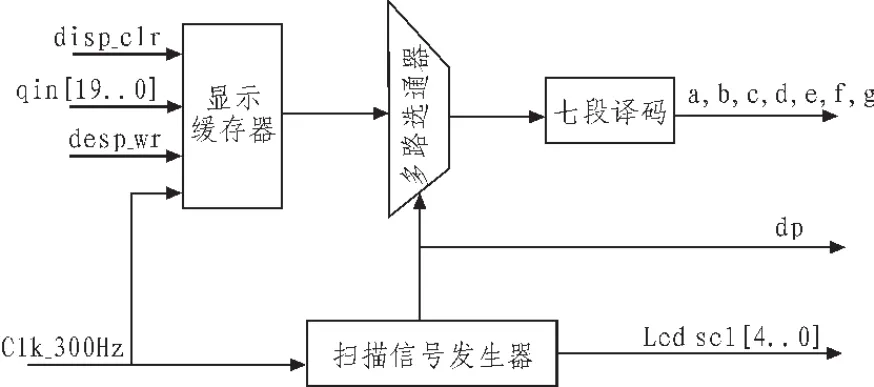

显示模块内部包括显示缓存器、多路选通器、扫描信号发生器、七段译码模块。结构图如图五所示。显示缓存器是一个存储量为20比特的寄存器,用于存储LED显示的内容,数值用4位的BCD码表示,小数点用一位二进制数表示。多路选通器用于从显示缓存器中选择出某一个LED的显示内容用于显示。扫描信号发生器产生片选信号,片选信号依次并循环地选通各个数码管。七段译码模块把4位的BCD码译码成便于显示的七段码。

图5 译码及显示模块Fig.5 Decoding and display module

扫描频率的大小必须适合才能达到很好的效果,如果扫描频率过小,每个数码管开启和关断的时间间隔就会大于人眼的视觉暂留时间,产生闪烁现象,扫描频率太大,会造成数码管频繁开启和关断,增加功耗,因此选择300 Hz作为扫描频率。

3 结论

通过实际测试可知可编程逻辑器件(FPGA)[7-8]具有丰富的可编程性与丰富的I/O引脚,在数字系统中的应用很广泛,而且可节省电路开发的费用与时间。本文提出的基于FPGA的斜面冲击机末速度测试方案表明此设计方案与预期要求基本一致,可编程逻辑器件(FPGA)具有丰富的可编程性与丰富的I/O引脚,此方案可方便的进行在线修改而不需改动硬件电路,具有较高的灵活性,可靠性及稳定性,且价格低廉,此方案也可应用于频率测量、火控系统中引信动作时间测试等领域。

[1]彭鹏,田书林.基于FPGA的CPU多UART的串行通信接口实现[J].自动化信息,2008,41(3):36-37. PENG Peng,TIAN Shu-lin.Implementation of serial communication interface of CPU based on FPGA multi UART[J]. Automating Information,2008,41(3):36-37.

[2]周润景,图雅,张丽敏.基于Quartus的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.

[3]华清软件嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.

[4]康晓文,刘亚强,崔均健,等.基于FPGA进位链TDC延时模型的建立与性能测试[J].核电子学与探测技术,2011(3): 46-47. KANG Xiao-wen,LIU Ya-qiang,CUI Jun-jian,et al.Carry chain TDC delay model and test of performance based on the FPGA[J].Nuclear Electronics&Detection Technology,2011(3):46-47.

[5]叶超,冯莉,欧阳艳晶.基于FPGA的精密时间间隔测量仪设计[J].信息与电子工程,2009(2):13-15. YE Chao,FENG Li,OUYANG Yan-jing.Design of precision time interval measuring instrument based FPGA[J]. Information and Electronic Engineering,2009(2):13-15.

[6]刘东斌,曹闹昌,胡其明.基于FPGA高精度时间间隔测量系统的设计与实现[J].弹箭与制导学报,2009(2):20-21. LIU Dong-bin,CAO Nao-chang,HU Qi-ming.Design and implementation of high precision time interval measure system based on FPGA[J].Jonual of Projectiles,Rockets,Missiles and Guidance,2009(2):20-21.

[7]黄志林.基于FPGA的并行DDS技术研究[J].现代电子技术, 2013(7):54-56. HUANG Zhi-lin.Research of parallel DDS technology based on FPGA[J].Modern Electronics Technique,2013(7):54-56.

[8]李国兴,杨芳.基于FPGA的视频采集显示系统[J].电子科技,2013(2):22-24,27. LI Guoxing,YANG Fang.Video acquisition system based on FPGA[J].Electronic Science and Technology,2013(2):22-24,27.

Term inal velocity test technology of incline impact tester based on FPGA

WANG Lin

(Xi’an Railway Vocational&Technical Institute,Xi’an 710016,China)

In order to protect the capability evaluation of transport packages under horizontal shock impact resistance strength and packaging on contents,broad based our research on the basis of special presents a FPGA oblique impact based on machine end speed test plan,after the actual test shows that the design scheme is practical,to achieve the desired results,and has high flexibility,reliability and stability,and the price is low,there is great practical value and significance of the promotion.

FPGA;tncline impact tester;terminal velocity;protection;reliable;low price

TN270.39

A

1674-6236(2015)07-0029-03

2014-07-03 稿件编号:201407026

王 琳(1961—),男,陕西西安人,讲师。研究方向:电工电子学。