数字电路老化失效预测与防护

2015-12-14张璐雅罗兰

张璐雅,罗兰

(解放军西安通信学院基础部应用技术教研室,西安710106)

数字电路老化失效预测与防护

张璐雅,罗兰

(解放军西安通信学院基础部应用技术教研室,西安710106)

随着半导体工艺的发展,数字电路的性能得到很大的提高,但是电路老化现象变得异常严重。本文针对电路老化现象进行了预测,并提出了相应的防护措施。

数字电路老化;失效预测;防护

1 导致数字电路老化的原因及影响

现在电子技术发展很快,电子产品的集成度也越来越高,工艺相对来说比较复杂,在制造的过程中,会因为使用的材料、设计和工艺程序不合理导致产品不符合要求,在使用过程中就会出现产品老化很快,结构组织不稳定。电路的老化也很容易受温度、湿度等外在环境的影响,电路在长期工作状态下,就会因为温度过高而出现老化现象。

数字电路老化在不同的层次有不同的表现特征。在器件级,电路的老化会使逻辑门翻转的速度逐渐减慢;在电路级,老化会增大电路的整体时延,引起时序违例,最终会导致电路的失效;在晶体管级,电路老化会使晶体管发生饱和,漏极电源逐渐减小,电压升高。电路老化会使数字电路的性能大幅度下降,因此,只有对数字电路老化进行失效预测和防护才能提高电子产品的性能,也能减少后期的维护成本,延长电路寿命。

2 数字电路老化失效预测方法

2.1建立相关数字老化模型

建立老化电路模型可以更好地分析电路中比较敏感的通路,能有效预测电路的老化现象。数字电路的基本组成元件是晶体管,所以建立晶体管级的老化模型受到越来越多的关注。在现代纳米工艺中,电路老化的主要因素就是NBTI效应,所以晶体管老化模型的研究目标就是NBTI效应。在该效应中,由于表面硅氢键断裂,晶体管中就会有氢气溢出,这样就会引起阙值电压的升高。反应晶体管老化的主要参数就是阙值电压,通过电压变化和时延变化值进行整合,来进行电路老化失效的预测。

2.2对数字电路老化进行在线测试

在数字电路中采用aging sensor的老化测试方法,通过判断时钟采样沿和逻辑信号的跳变来判断电路是否存在问题。Aging sensor的在线监测是检测电路老化比较常用的方法,电路老化主要表现在路径时延的增加,图1就是基于aging sensor的老化在线测试结构。

图1 Aging sensor的老化在线测试结构Fig.1 The structure of online test structure for sensor Aging

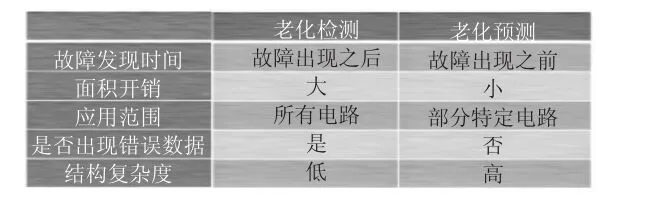

它的测试方式可分为老化检测和预测两种,检测的目的主要是发现数字电路中存在的问题和故障,如果电路存在问题时,会发出预警信号;老化测试的目的是在电路要发生故障时,发出预示信号,图2、图3揭示了预测和检测之间的区别。检测窗口在时钟采沿之后叫做Detection Slack,预测窗口采沿之前叫作Guardband[1]。

图2 老化预测和老化检测的区别Fig.2 The difference between the aging prediction and the aging test.

图3 老化检测和老化预测判定窗口的区别Fig.3 The difference between the window of the aging test and the aging prediction

在预兆单元的基础上进行老化测试,首先在电路中插入一条功能电路做参考。在测试中,要采集预兆单元上的数据和正常标准的数据相比较,通过比较数据来看电路的老化情况。

3 数字电路老化的防护

第一,调整工作参数。调整工作参数就是通过调整电路工作中的相关电气参数来防止物理器件的快速老化。目前主要通过调整电路的频率和动态电压来实现。阙值电压的不断升高,会导致器件的翻转速度下降,将电压调小,就可以减少阙值升高带来的问题。

第二,输入向量控制。输入向量控制是指在电路静止状态下,向电路输入向量,使老化的晶体管栅级保持高电平,使晶体管处于恢复时期,用来减缓电路的老化现象。

采用时序拆借的老化容忍方法也能在一定程度上延缓电路老化,主要针对的是流水电路,利用的是不同的路径时序量不同的原理,在路径增大时,挪用其他路径上的时序量增大本路径的时间,从而防止时序违例情况的发生。但是这种方法只适用于流水电路的防护[2]。

第三,合理控制受压时间来延缓电路老化。晶体管的受压时间越长,就会导致电路老化情况越来越严重。控制晶体管的受压时间能有效减缓电路老化,如果不是非常必要的情况下,尽量让它保持空载状态,这样就可以减缓晶体管的老化速度。其中最常用的方法就是控制冗余电路分流工作和控制逻辑门带电时间。

4 结语

纳米技术下数字电路的应用虽然给人们的生活带来了很多方便,但是它也存在老化严重这一问题,应该加强数字电路的预测和防护,减缓电路的老化,延长电路的使用寿命。

[1]徐辉.集成电路老化预测与容忍[D].合肥:合肥工业大学,2013.

[2]史冬霞.数字集成电路老化预测及单粒子效应研究[D].合肥:合肥工业大学,2013.

[3]严鲁明,梁华国,黄正峰.基于时-空冗余的集成电路老化失效防护方法[J].电子测量与仪器学报,2013,(01):38-44.

Failure Prediction and Protection of Digital Circuit Aging

ZHANGLu-ya,LUOLan

(Department ofApplied Technology,Xi'an Communication Institute,Xi'an 710106,China)

With the development ofsemiconductor technology,the performance ofdigital circuit has been greatlyimproved,but the phenomenon of circuit aging has become very serious.In this paper,the phenomenon of circuit aging is predicted,and the corresponding protective measures are put forward.

Digital circuit aging;Filure prediction;Protection

TN79

A

1674-8646(2015)09-0086-02

2015-05-29