一个5-bit 4 GS/s的插值型模数转换器设计

2015-12-05彭勇,路祥,唐鹤

彭 勇,路 祥,唐 鹤

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 引言

高速低分辨率的ADC在硬盘读写、光纤通信和超宽带系统(UWB)中都有广泛的应用。理论上,全并行结构的ADC是高速ADC设计的最佳选择。然而全并行ADC的功耗和面积随分辨率呈指数增长,而且寄生电容和输入电阻大大降低了预放大器阵列的带宽和速度,因此极大地限制了它的应用。为解决这一问题,插值技术被采用[1],以减少其预放大器的数目,同时减小输入寄生电容,节约了功耗和面积,也更具有实用性。另外,为了减少预放大器阵列和比较器的失调电压影响,相应地引入均值技术,在预放大器间插入均值电阻,有效地抑制预放大器的失调电压。因此,在实际的高速ADC设计中,采用插值和均值技术的预放大器阵列是最关键的部分,它的带宽和增益将直接影响整体ADC的性能,包括速度和精度等,所以需要对预放大器阵列进行详细的分析以获得最优的性能[2]。

本文提出一种电阻插值型ADC的设计方法:分析了预放大器阵列的增益和带宽对ADC性能的影响,从而获得最优化的预放大器阵列。设计时采用了分布式采样结构,用CML结构的高速比较器实现采样功能,另外对预放大器阵列边缘进行处理以提高精度。ADC在TSMC 65 nm工艺下设计并仿真,最终达到设计要求。

2 系统框架和电路实现

本文所提供的高速ADC系统架构如图1所示,包含参考电压电阻串、预放大器阵列、高速锁存器和编码电路几个部分。

图 1 ADC系统框架图

预放大器网络由两级预放大器阵列组成,逐级放大输入电压与参考电压的差值,第一级由15个预放大器组成,插值系数为4;第二级由57个预放大器组成,插值系数为1,即采用均值技术。插值技术和均值技术能有效抑制预放大器的失调电压[1]。为使每个预放大器在工作时有相同的状态,需在每级预放大器阵列边缘加一些冗余预放大器(dummy pre-amps),因此本文在第一级两端边缘各加了3个,在第二级两端边缘各加了13个。同时根据文献[1]中的方法,在预放大器的边缘加入等效电阻Req和等效电流源Iterm以模拟无限个预放大器和由插值级均值技术构成的阵列,这样可使每个预放大器的输出端负载相同。其中:

其中R0是预放大器的负载电阻,R1是插值/均值电阻,ISS是预放大器的尾电流。

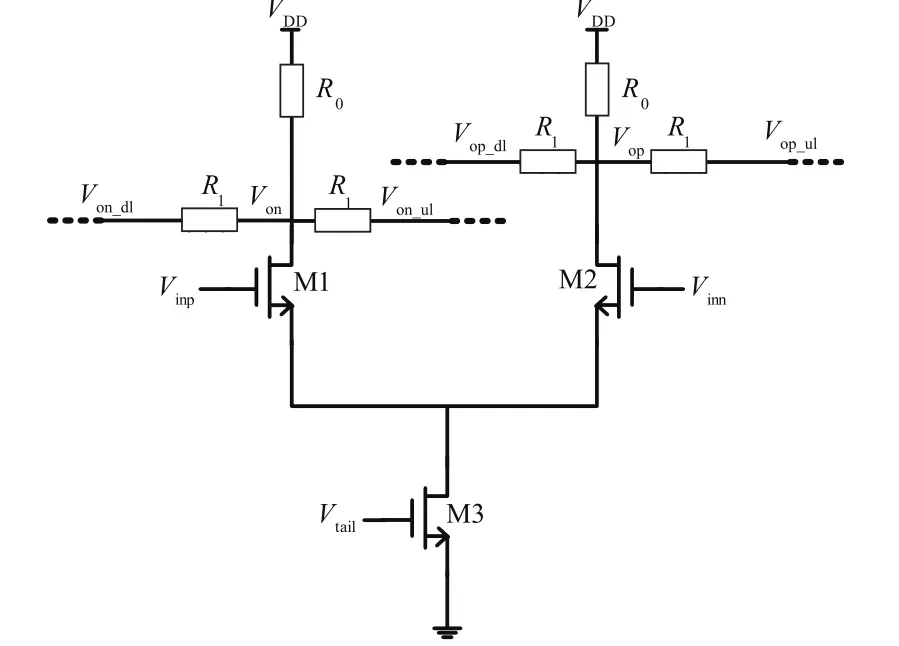

本设计中第一级和第二级所采用的预放大器结构分别如图2和图3所示。由于采用了全差分的输入信号,第一级的预放大器有4个输入,输出端采用电阻做负载,可以稳定输出共模电压。第二级的预放大器有2个输入,结构与第一级预放大器类似。预放大器阵列的增益和带宽直接影响ADC性能,如带宽决定信号响应速度并影响其后锁存器的采样速度,进而影响ADC速度,因此需要对增益和带宽做合理的折中考虑和设计。R0/R1的值越大,插值/均值技术对预放大器的失调电压抑制效果就越好,预放大器的带宽会稍微增大,但同时会减小预放大器的增益,使比较器的比较时间增加[1,3];反之亦然。同时,预放大器阵列还能有效减小比较器的失调电压对输入信号的影响。

图2 第一级预放大器

在高速ADC设计中,采样电路是设计难点,特别是应用在全并行结构中的采样电路。由于预放大器数量很多,导致预放大器阵列的输入寄生电容非常大,反而降低了预放大器阵列的带宽,使得信号的高速采样难以实现,因此有时不得不采用电感以提高采样速度,但这样做会极大地占用芯片面积并且增加功耗。

本文没有采用传统的单独采样电路结构,而是在预放大器阵列后加入一级CML的锁存器以实现分布式采样功能[4],另外又采用了两级CML锁存器作为比较器。CML锁存器的结构如图4所示。其中CK与CKB为两相不交叠时钟。在采样相位时,CK为高电平,输入差分对在工作状态,将输入差分电压放大,相当于对这个时刻的输入差分电压采样。同时,CKB为低电平,后面交叉连接的两个MOS管中没有电流流过,处于截止状态。在保持相位时,CK为低电平,输入差分对管中没有电流流过,处于截止状态,输入差分对管不工作;CKB为高电平,后面交叉连接的管子形成正反馈系统,对采样相位的差分输出值进一步放大,并保持这个差分输出值,输出给下一级的锁存器。整个过程实现了分布式采样的功能。

图3 第二级预放大器

图4 CML锁存器

由于传统的高速锁存比较器的失调电压比较大,所以在本设计中并未采用,而是选择了结构相对简单、失调更小的CML锁存器作为高速比较器,同时加入均值电阻串,减少其失调的影响[4]。同时,后面两级的锁存器也构成了D触发器,使得编码器的输入端能与时钟同步,减小误差。编码电路中的门电路及D触发器都采用了CML结构[5],如图5所示,提高了响应速度,满足高速ADC的速度需求。

3 仿真结果

本文所设计的电路采用TSMC 65 nm工艺,用HSPICE进行仿真验证,电源电压为1.2 V,在4 GHz的采样频率下,在输入频率为200 MHz~1 GHz的情况下,ADC的有效位数(ENOB)在4.7左右变化。整个核心ADC系统的功耗为85 mW。动态参数仿真结果如图6所示。整个ADC的功能仿真结果如图7所示,其中输入信号为一个差分的斜坡信号Vin_diff,CLK为时钟信号,B0~B4为输出数字码,仿真结果显示ADC能正常工作。表1展示了本文所述ADC仿真结果与文献[6]和文献[7]结果的对比,可以看出,本文所述ADC有良好的性能。

图5 CML门电路

表1 仿真结果汇总

图6 ADC动态特性(ENOB)

4 结论

本文提出了一种5-bit 4 GS/s的高速ADC系统的设计,采用了带均值技术的预放大器来抑制高速比较器的失调电压,同时采用分布式采样方案,并采用电流模编码电路。在TSMC 65 nm下进行了仿真验证,结果表明本设计能在CMOS深亚微米工艺下得到高速度和良好的分辨率。

图7 ADC功能仿真结果

[1] Pedro Figueiredo, Joao Vital. Offset Reduction Techniques in High-Speed Analog to Digital Converters[M]. Springer,2009. 67-90.

[2] J Vandenbussche, E Lauwers, et al. Systematic Design of a 200MS/s 8-bit Interpolating A/D converter[C]. DATE,2002, 449-454.

[3] He Tang, Yong Peng,et al. Quantitative Analysis for High Speed Interpolated/Averaging ADC[C]. ASIC, 2013, 1-4.

[4] Samad Sheikhaei.A 43 mW Single-Channel 4GS/s 4-Bit Flash ADC in 0.18 μm CMOS[D]. Vancouver∶ The University of British Columbia, 2008: 33-46.

[5] Wenjia Li, Lu Huang, Xuefei Bai. A Pseudo-2bit 4GSps Flash ADC in 0.18 μm CMOS for an IR-UWB Communication System[C]. ICUWB, 2010, 1-4.

[6] Sunghyun Park,Yorgos Palaskas, Michael P Flynn. A 4 GS/s 4b Flash ADC in 0.18 μm CMOS[C]. ISSCC, 2006.

[7] Ying-Zu Lin,Cheng-Wu Lin, Soon-Jyh Chang. A 5bit 3.2-GS/s Flash ADC with a digital offset calibration scheme[C]. IEEE VLSI, 2010.