TMSR 数字化反应堆保护系统数字信号与逻辑处理功能的FPGA实现探讨

2015-12-01刘珍宝

刘 烨 刘珍宝 后 接

TMSR 数字化反应堆保护系统数字信号与逻辑处理功能的FPGA实现探讨

刘 烨1,2刘珍宝1,3后 接1,2

1(中国科学院上海应用物理研究所 嘉定园区 上海 201800)2(中国科学院核辐射与核能技术重点实验室 上海 201800)3(中国科学院大学 北京 100049)

现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)在反应堆保护系统中得到越来越广泛的应用。中国科学院上海应用物理研究所的钍基熔盐堆(Thorium Molten Salt Reactor, TMSR)核能系统先导项目拟采用FPGA技术开发数字化的反应堆保护系统,本文探讨使用FPGA设计TMSR保护系统的数字信号处理(模数转换芯片驱动、数字滤波、定值比较)以及逻辑处理(逻辑符合)功能模块,同时通过软件仿真和硬件测试,为FPGA功能验证和确认(V&V)打基础。软件仿真和硬件测试结果表明在TMSR保护系统内使用FPGA实现数字信号处理与逻辑处理在技术上是可行的。

现场可编程逻辑门阵列,数字化反应堆保护系统,逻辑处理,模数转换

反应堆保护系统(Reactor Protection System, RPS)是确保反应堆在即将出现或已出现偏离安全允许的工况时,能及时落棒停堆的重要安全保障[1]。在核电中属于1E级设备,安全性和可靠性要求高。

早期的保护系统受限于技术因素主要由模拟电路构成,自身维护和反应堆状态显示比较困难。随着数字技术的发展,基于计算机的数字化反应堆保护系统逐渐取代传统模拟反应堆保护系统,虽然数字化的反应堆保护系统组件简单、维护方便以及显示技术较为成熟,但其使用的数字处理软件存在共因故障以及验证确认(V&V)等困难问题[2]。近年来,随着数字化硬件技术的逐渐成熟,采用可编程器件取代计算机软件执行数字功能的保护系统方案正在出现。

现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)功能强大,能够实现多种数字处理功能,还能够用来设计数字通信电路。目前FPGA在保护系统中的应用越来越多,国核自仪系统工程有限公司与美国洛克希德马丁公司联合开发的NuPAC[3]以及乌克兰RADIY公司的RADIY[4]等平台就是基于FPGA开发的。FPGA具有如下优点[5]:(1) FPGA属于硬件电路,处理结果确定;(2) 内部并行运行,处理速度快;(3) 系统构建简单,维护方便;(4) 安全性高;(5) FPGA成本低,性价比高,开发周期短。

钍基熔盐堆(Thorium Molten Salt Reactor, TMSR)核能系统先导专项旨在发展拥有自主知识产权的整套系统,包含反应堆设计制造、核燃料设计制造,以及仪控系统、保护系统、安全驱动系统等配套设备设施。TMSR拟使用FPGA进行保护系统设计,项目初期有必要先在实验室进行相应的功能验证。本文是对在保护系统中使用FPGA技术进行一定的前期研究工作,主要工作在数字信号处理和逻辑处理的功能实现以及相应的测试,以掌握一定的FPGA设计及测试技术。本文只在其中FPGA信号处理功能上有所探讨,与NuPAC平台的一整套硬件设备相比还有很大差距。

NuPAC平台采用的Actel公司基于FLASH技术的系列FPGA芯片具备很好的稳定性和安全性,且具备一定的耐辐照性能,相对于其他公司基于SRAM的FPGA芯片更适合于保护系统使用。本文所用芯片就是基于Actel公司的此类FPGA芯片进行信号处理功能设计,使用Verilog HDL语言进行编程,使用Icarus Verilog软件进行仿真,使用GtkWave软件观察仿真波形,使用Actel FPGA芯片专属开发集成环境Libero SoC软件进行综合布局布线以及开发板ProASIC3-VQ100 DEV. KIT上FPGA芯片A3P125VQ100的烧写,利用FPGA开发板及AD等芯片和面包板搭建电路进行硬件测试。

1 保护系统结构

保护系统属于1E级设备,需要有高可靠性,系统结构上一般采用冗余设计,由三个或四个执行相同功能的冗余序列组成。每个序列主要由传感器、模拟信号处理、数字信号处理、逻辑处理、保护信号输出、输出驱动机构以及通信机构等组成。各序列处理来自不同传感器的相同的保护信号,当其中有两个或以上序列的保护信号达到停堆条件则产生紧急停堆信号,驱动停堆断路器断路,切断控制棒电机电源,控制棒下落,反应堆停堆。

数字信号处理包括模数转换芯片驱动及数据接收、数字信号滤波、定值比较;逻辑处理包括符合逻辑。这两个部分使用FPGA实现,是本文讨论的重点。四重冗余结构的保护系统的保护变量处理流程如图1所示,图1中各序列处理的保护变量是同一或不同传感器采集到的同一个物理量(压力、温度、中子通量等)。每序列数字信号处理模块接收保护变量经模数转换(Analog to Digital Converter, ADC)芯片转换后的数字量信号,进行数字滤波和定值比较之后产生局部保护信号,该信号输出至本序列和其他三个序列的逻辑处理模块。逻辑处理模块同时接收本序列和其他三个序列的局部保护信号,进行四选二符合逻辑(two-out-of-four logic, 2oo4),输出本序列的停堆保护信号。

图1 四重冗余保护系统变量处理流程图Fig.1 Chart of quadruple RPS variable processing flow.

2 保护系统模块

2.1 AD芯片驱动模块

保护变量一般为物理量,在经传感器采集后为模拟电信号,包括电流、电压、热电偶信号等,需要使用AD芯片将其转换成FPGA能够识别处理的数字信号。为满足可靠性和独立性要求,保护变量信号在输入保护系统前需进行隔离,这部分属于模拟电路范畴,不在本文的讨论范围内。TMSR保护系统要求模数转换芯片的位宽不小于12 bit,采样速率不小于100 kHz,输入信号是0−5 V、0−10 V、4−20mA等。

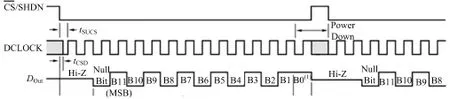

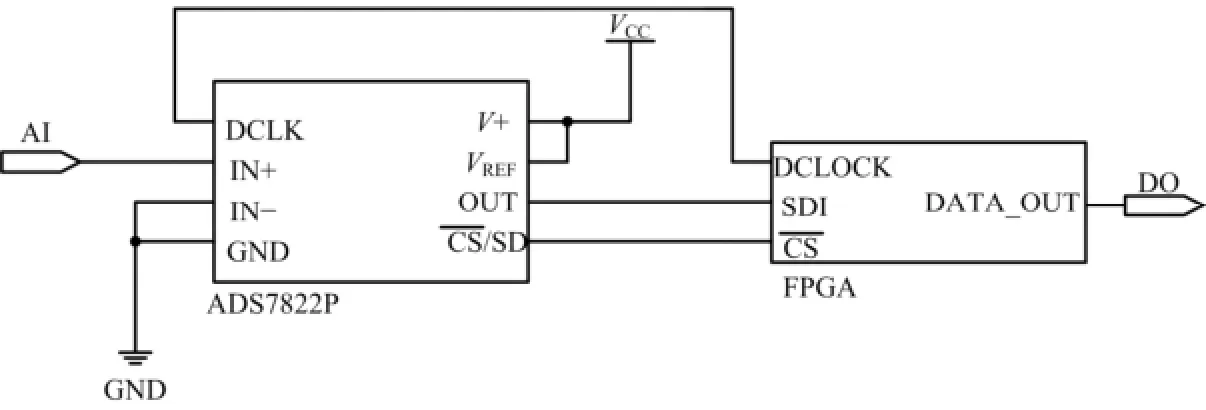

本文选用的AD芯片是TI公司的ADS7822P,可转换0−5 V电压信号,拥有12 bit采样数据位宽,最高200 kHz采样率,有低功耗、节能等特性。该芯片数据符合TMSR对保护系统的性能要求,其正常工作时的时序图如图2所示[6]。

图2 ADS7822P时序图Fig.2 Sequence diagram of ADS7822P.

图2中,CS/SHDN信号置高时处于待机模式,DOut输出高阻态;置低后开始模数转换,并在置低后第3个DCLOCK下降沿开始,每个DCLOCK下降沿DOut输出12 bit采样数据,从最高位开始串行输出,当最后一位数据输出完毕的下一个DCLOCK下降沿/SHDN应立刻置高,否则DOut会继续输出此次的采样数据,造成时间浪费,同时也使得设计复杂化。可以看出ADS7822P的采样周期由/SHDN信号的周期决定。

参考芯片手册,依照其工作模式,进行了ADS7822P芯片驱动模块的FPGA设计,由三个部分组成:工作时钟部分、串并转换部分和数据缓存部分。工作时钟部分产生驱动ADS7822P芯片正常工作的时钟,是图2中的/SHDN信号和DCLOCK信号;串并转换部分,将图2中AD芯片输出的串行数据流DOut转换成并行数据输出至数据缓存模块;数据缓存部分中的数据在下一次采样输出后刷新,保存时限为一个ADS7822P的采样周期。

2.2 数字滤波模块

虽然,在保护信号输入到AD芯片之前经过适当的模拟滤波去除了大部分的噪音信号,但是AD芯片本身亦存在一定的因素使采样结果存在误差,需要对其输出的数字信号进行进一步的数字滤波处理,以防止定值比较模块输出错误信号,使得保护系统发生误动作或拒动作。

本文所设计的数字滤波模块采用移动平均滤波的方式,该方法实现简单,响应速度快。能够滤除平均数为0的噪声,譬如芯片本身的正负输出误差。同时能够减弱均值不为0的噪声,譬如参考电压的抖动造成的采样误差。

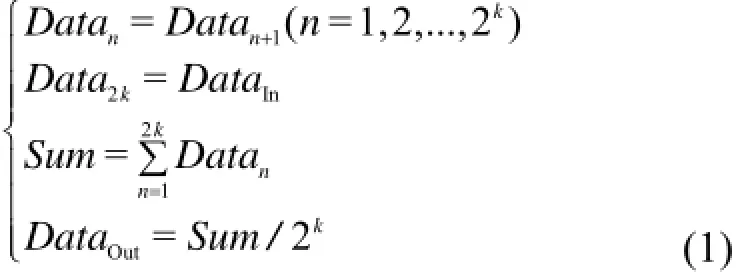

该模块记录2的整数次幂个数据,在每一个数据更新时钟移入一个新数据,移出最先进入的数据,同时进行一次均值计算并输出,该结果即是滤波后的信号。数据更新时钟周期与AD数据刷新周期相同。移位算法如式(1)所示:

式中,k是正整数;Sum是所有缓存数据的和;Datan是第n位数据;Data1是最早进入的数据;DataIn是最新进入的数据;DataOut是均值滤波输出结果。

2.3 定值比较模块

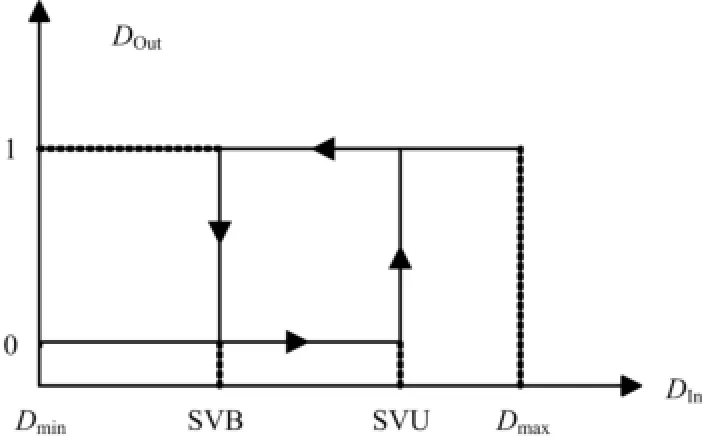

保护系统在保护信号超出安全范围时产生紧急停堆保护信号,是保护系统一个十分重要功能模块,需要高稳定性和高可靠性。紧急停堆信号产生由两部分实现:一是定值比较模块,对比保护信号量值和设定的安全范围值,超限时则输出局部停堆信号;二是符合逻辑模块,判断当n个冗余序列中最少m个序列发出局部紧急停堆信号,则输出全局紧急停堆保护信号。定值比较模块的具体算法如式(2)、(3)所示,相应的图示如图3所示,DOut为“1”表示需要紧急停堆,“0”表示局部安全无需停堆。当输入信号(DIn)量值大于上阈值(Set Value Up, SVU),则输出(DOut)为1;当输入信号量值小于下阈值(Set Value Bottom, SVB)时,输出为0;当输入信号介于上下阈值之间时,输出维持前一状态。这样做的好处在于能够在一定程度上消除输入信号的不稳定性所带来的输出结果的抖动。上下阈值之间的差值根据输入信号的精度进行适当的选择,但上阈值的选择前提是要最大可能地杜绝反应堆事故的发生。

图3 式(2)的图示表示Fig.3 Diagram of function (2).

2.4 符合逻辑模块

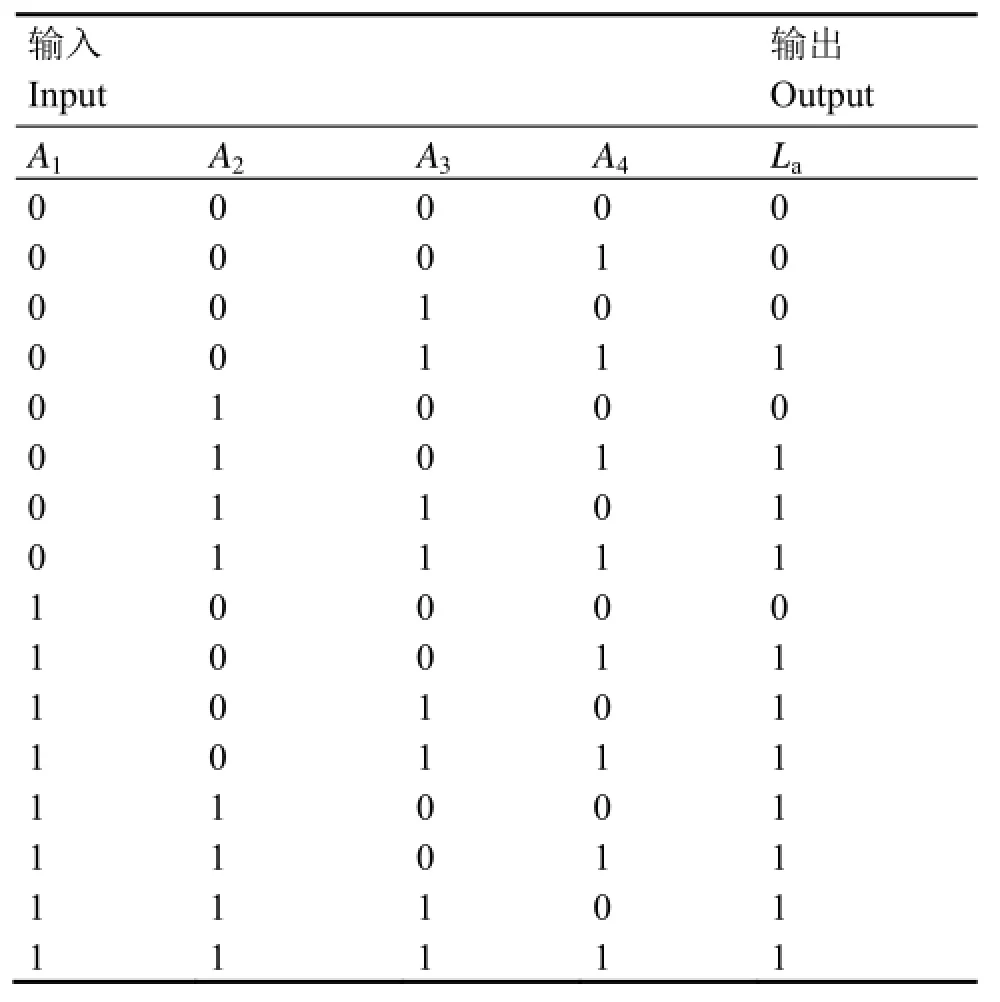

如前所述,每个序列内的符合逻辑模块处理多个保护序列的局部停堆保护信号,当且仅当其中有一定个数或以上为“1”时,输出序列紧急停堆信号(用“1”表示)。该模块也是保护系统中一个十分重要的部分。本文以2oo4为例,进行具体设计说明和测试。根据2oo4算法的定义可以得出其真值如表1所示,表1中A1、A2、A3、A4是4个输入逻辑值表示4个序列的局部保护信号,La是符合逻辑输出值表示紧急停堆状态(高电平“1”表示停堆,低电平“0”表示正常)。

表1 四选二符合逻辑真值表Table 1 Truth table of 2oo4 logic.

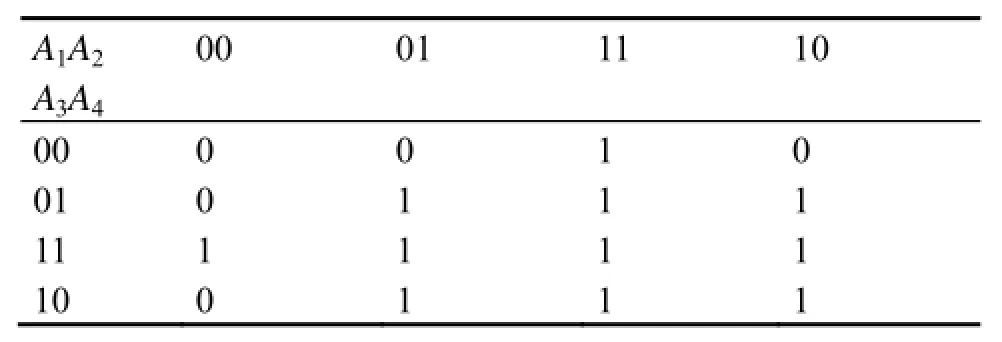

将真值表1写为卡诺图形式,则可得2oo4算法的卡诺图表示,如表2所示。

表2 四选二符合逻辑卡诺图Table 2 Karnaugh map of 2oo4 logic.

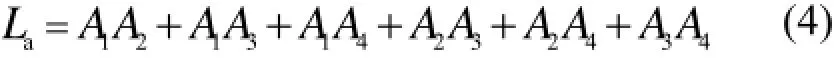

利用表2可得2oo4的最简逻辑公式(4),该模块的FPGA设计依照式(4)进行。

3 软件仿真及硬件测试

3.1 模数转换芯片驱动模块

ADS7822P芯片驱动模块中工作时钟部分的软件仿真波形如图4所示。

图4 ADS7822P芯片驱动模块工作时钟部分仿真波形图Fig.4 Simulation wave of working clock part of ADS7822P driver module.

从图4中可以看出,DCLOCK与CS的时序要求与图2相同。将程序烧入FPGA开发板后的硬件电路测试的示波器波形图如图5所示,从图5中可以看出时序与软件仿真相同,符合ADS7822P驱动要求。图5中SDI输出的是测试时输入AD芯片的2.4908V电压,该值理论上对应的数字量为12'b0111_1111_0010,实际测得的输出数据为12'b0111_1111_0000,该值与理论值误差小于0.099%,这个结果一方面说明了时钟部分正确驱动了ADS7822P芯片,同时也说明了ADS7822P芯片的转换性能很高。

图5 示波器波形图Fig.5 Picture of oscilloscope of working clock part.

串并转换和数据缓存部分采用的是通用设计,这里不进行软件仿真和硬件测试。

3.2 数字滤波模块

为仿真验证数字滤波模块的性能和正确性,设计了一个附带误差范围为−2−+2、阶梯为1的随机噪声的数字信号输入该滤波器进行。由随机性可知,该噪声的平均值为0。仿真结果如图6所示,该模块在完成初始化过程之后输出数据误差在−1以内,表明该滤波器能够很好滤除该均值为0的噪声。测试中式(1)内的参数k=8,即计算平均值的数据个数为256;输入值DataIn=12'd888 (−2, −1, +0, +1, +2)。

图6 滤波器仿真结果Fig.6 Simulation wave of moving average filter.

硬件测试使用ADS7822P芯片的输出作为数据源,ADC芯片驱动模块作为数字滤波模块的前级,测试中使用4个8段数码管进行滤波后的数值显示,电路原理图如图7所示。测试结果表明,模拟输入电压值和滤波后的数字输出值差距在0.001 V,且数值显示相比不使用数字滤波模块时更加稳定。这说明ADC芯片驱动模块和数字滤波模块功能正确,FPGA同样能够实现数字信号处理的任务。

图7 数字滤波电路原理图Fig.7 Circuit schematic of digital filter.

3.3 定值比较模块

定值比较模块的仿真中,SVU设定为12'h99A,SVB设定为12'h98B。设计了一个12比特计数器的输出作为定值比较模块的输入数据(DIn)进行测试。该计数器的工作方式是:初始化后,首先从0开始,每个时钟上升沿加1;然后到达最大值后在每个时钟上升沿减1,直至0;接着再进行加1操作,依此规则循环加减。仿真结果如图8所示。

图8 比较器仿真波形图(a) 输入升至12'h99A时结果从0变成1,(b) 输入降为12'h98B时结果从1变为0Fig.8 Simulation wave of comparator. (a) Result change from 0 to 1 when data in up to 12'h99A, (b) Result change from 1 to 0 when data in down to 12'h98B

从图8(a)可以看出,当输入(Data_from_AD,即DIn)从0上升至SVU (12'h99A)时,比较器结果(Result,即DOut)从“0”变成“1”,而在此之前(包括上升至SVB,12'h99B)维持输出为“0”;从图8(b)可以看出,当输入降为SVB时,比较器结果从“1”变为了“0”,而在降为SVU时则没有变化。这说明,定值比较模块的设计符合式(2)的要求。

硬件测试时由于使用了FPGA开发板上自带的4位拨码开关作为输入DIn,输入数值最大范围是0−15,所以定值比较模块的数据位数被设定为4。这并不影响定值比较模块功能测试,只是在速度上会快于12位宽的,但在高速FPGA面前速度差异并不明显。输入数值的显示使用8段数码管,报警使用LED阵列和蜂鸣器。当输出为“1”时报警,此时LED阵列亮、蜂鸣器发声;反之则不报警,此时LED不亮、蜂鸣器无声。

3.4 符合逻辑模块

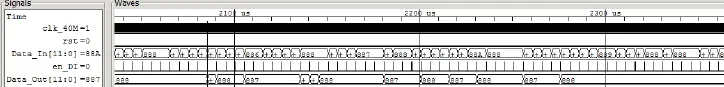

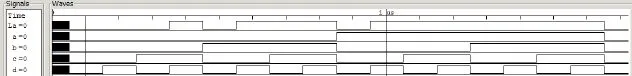

软件仿真中使用4 bit计数器的输出作为逻辑输入,进行真值表遍历验证。仿真波形如图9所示。

测试中,输入数据DIn范围设定为0−9,SVU设定为8,SVB设定为6。数值输入方式为从0升至9然后下降至0,阶梯都为1。

实验结果显示,输入从0上升到6和7时,没有报警;当输入继续上升到8时,开始报警;当从9开始下降至7时,报警没有解除;当下降至6和6以下时,报警解除。该过程符合式(2)、(3)和图3,说明硬件测试结果与理论相符合,进一步说明了FPGA同样能够执行定值比较功能。

从图9可以看出,仿真结果与真值表1完全符合,说明源码设计正确。硬件测试结果也完全符合真值表1,进一步说明了FPGA同样能够实现符合逻辑功能。

图9 符合逻辑仿真波形图Fig.9 Simulation wave of 2oo4 logic.

4 结语

本文所做工作只局限于一部分功能实现和验证,通过Verilog HDL语言设计及实现了AD芯片驱动、移动均值数字滤波、定值比较和2oo4这4个功能,没有涉及如何对FPGA进行全面的验证和确认,且所设计的功能模块比较简单。该设计结构简单,可以作为演示系统进行相关的功能演示,距实际应用还存在差距。AD芯片驱动模块针对特定型号的AD芯片,滤波也是使用移动均值滤波,噪声滤除比较单一,定值比较模块则在上下阈值的选取上要经过严格的理论计算和实际验证后才能确定,逻辑符合模块则符合实际应用。

本项研究积累了FPGA设计经验和关键技术,利用软件仿真和FPGA开发板硬件测试,很好地验证了设计的正确性,对FPGA在TMSR保护系统上的使用提供了重要的参考意义,同时积累了FPGA调试和测试经验,为FPGA编程开发的V&V提供了一定的基础。软件仿真与硬件测试的结果表明,FPGA能够实现计算机软件在反应堆保护系统中执行的数字信号处理和逻辑处理功能。

1 张明葵, 杨自觉, 金华晋, 等. CARR保护系统设计[J].核动力工程, 2006, 27(5): 146−149 ZHANG Mingkui, YANG Zijue, JIN Huajin, et al. Design of CARR protection system[J]. Nuclear Power Engineering, 2006, 27(5): 146−149

2 刘宏春, 王涛涛, 王华金, 等. 岭澳二期核电站数字化反应堆保护系统[J]. 核动力工程, 2008, 29(1): 1−4 LIU Hongchun, WANG Taotao, WANG Huajin, et al. Design of digital reactor protection system of Ling'ao phase II NPP[J]. Nuclear Power Engineering, 2008, 29(1): 1−4

3 曾海, Siedlarczyk I, 毛欢. 基于NuPAC的核电厂反应堆保护系统[J]. 原子能科学技术, 2014, 48(4): 692−697 ZENG Hai, Siedlarczyk I, MAO Huan. Reactor protection system of nuclear power plant based on NuPAC[J]. Atomic Energy Science and Technology, 2014, 48(4): 692−697

4 尹宝娟, 毛从吉, 黄伟杰, 等. 核级保护系统中FPGA实现方案的若干问题探讨[J]. 核电子学与探测技术, 2013, 33(9): 1050−1053 YIN Baojuan, MAO Congji, HUANG Weijie, et al. Discussion on several important issues of protection system based FPGA in NPP[J]. Nuclear Electronics & Detection Technology, 2013, 33(9): 1050−1053

5 张维, 石铭德, 郑文祥, 等. 基于现场可编程门阵列的反应堆数字化保护系统设计[J]. 原子能科学技术, 2001, 35(5): 432−435 ZHANG Wei, SHI Mingde, ZHENG Wenxiang, et al. Design of novel digital reactor protection system based on field programmable gate array[J]. Atomic Energy Science and Technology, 2001, 35(5): 432−435

6 Texas Instruments Incorporated. 12-Bit, 200 kHz, microPower sampling analog-to-digital converter (Rev.C)[EB/OL]. http://www.ti.com/product/ADS7822/ technicaldocuments, 2007-07-27

CLC TL99

Design and implementation of FPGA-based digital and logical signal processing functions of reactor protection system for TMSR

LIU Ye1,2LIU Zhenbao1,3HOU Jie1,2

1(Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Jiading Campus, Shanghai 201800, China) 2(Key Laboratory of Nuclear Radiation and Nuclear Energy Technology, Chinese Academy of Sciences, Shanghai 201800, China) 3(University of Chinese Academy of Sciences, Beijing 100049, China)

Background: Field Programmable Gate Array (FPGA) can be used to overcome the software common cause failures (CCF), thus is a more and more widely applied to design the Digital Reactor Protection System (DRPS). There are many companies such as State Nuclear Power Automation System Engineering Company (SNPAS, China), RPC Radiy (Ukraine), etc., are doing research on FPGA-based DRPS. Thorium Molten Salt Reactor (TMSR) project plans to do the same work now. Purpose: Digital signal process (analog to digital converter driven, digital filter, and quantitative comparison), logic process (two-out-of-four logic, 2oo4) and data communication are some key components in DRPS design. It is important to test whether FPGA is able to realize these key techniques or not. Methods: First of all, the flash-based FPGA made by Actel Company is selected to design for digital signal process and logic process, and coded by Verilog Hardware Description Language (Verilog HDL, Verilog) under Libero SoC program. Then the Icarus Verilog (iVerilog) program is employed for simulation, and finally the signal waveform is watched by GtkWave program. Hardware test is performed by using FPGA development board together with some necessary chips. Results: Experimental results showed that the digital signal process and logic process were realized in the dedicated FPGA and performed well. Analog to Digital Converter (ADC) driven module was stable and executed as fast as the ADC chip could. Digital filter module made the ADC data much more stable. Quantitative comparison module got expected results accurately. The 2oo4 logic module gave the result immediately when the inputs had 2 or more “1”. It is of most importance that all of these modules worked simultaneously. Conclusion: It is practicable to use flash-based FPGA in DRPS of TMSR project technically due to its non-software common cause failure, fast speed, simplification and parallelism.

Field Programmable Gate Array (FPGA), Digital Reactor Protection System (DRPS), Logical process, Analog to Digital Converter (ADC)

TL99

10.11889/j.0253-3219.2015.hjs.38.040404

中国科学院战略性先导科技专项(No.XDA02010300)资助

刘烨,男,1988年出生,2012年于南京大学获工程硕士学位,工程师,从事核反应堆保护系统研究和设计工作

后接,E-mail: houjie@sinap.ac.cn

2014-08-27,

2014-12-23