基于FPGA 的多通道信号采集系统设计

2015-11-28赵兴海丁永红尤文斌李致成朱倩倩

赵兴海,丁永红,尤文斌,李致成,朱倩倩

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

在声呐信号处理系统中,声呐基阵接收到的信号由信号采集模块完成信号的转换与采集,并传送至信号处理模块进行数据处理。近年来,声呐系统对信号处理,特别是信号采集模块提出了更高的要求,采样通道数更多,采样精度更高[2-4]。针对这一要求,本文设计了一种基于FPGA 的高速信号采集处理模块,该模块使用TI 公司24 位高精度模数转换芯片ADS1278,并采用FPGA 作AD 芯片的采样控制,实现了多路差分模拟信号的模数转换与数据采集[1,5]。

可编程逻辑器件FPGA 为Altera 公司的CycloneIV E 系列EP4CE40F23C8N 型号的FPGA。在系统中FPGA 控制16个八进一出的AD 转换芯片,将AD 输出的128 路SPI 信号进行串并转换,需要I/O 口35 个。FPGA 将采集到的数据由千兆以太网传输到上位机。

1 信号采集模块硬件设计

1.1 模拟信号调理模块

这里采用的信号调理电路,即是用运放OPA1632 将输入的电压信号,跟随、分压,到达A/D 芯片的输入电压范围。具体电路如1 所示。

图1 前端信号调理电路

采用运算放大器OPAl632 和RC 构成的低通滤波器对输入信号进行调理,差分运放电源可采用10 μF 和0.1 μF的旁路电容,差分运算放大器采正负15 V 双电源供电,既满足系统要求,又极大降低运算放大器功耗。

运算放大器的放大倍数可以通过两个阻值灵活控制。由于我们采用的模数转换器ADSl278 的量程为-2.5 V~+2.5 V(参考源为2.5 V),而输入的差分电压为-15 V~+15 V。通过调节电阻比值,将输入电压进行1/6 的分压,得到满足A/D 芯片的输入要求。

差分运算放大器一般有VCOM 输入引脚。该引脚是电压输入端,其电压值将决定两个输出差分电压的平均值,即V0+和V0-的平均值为VCOM。该系统设计将ADSl278 的VCOM 引脚输出电压经跟随后,接入OPAl632 的VCOM 输入端。

1.2 模拟信号采集模块

经过调理电路的跟随、分压得到-2.5 V~+2.5 V 的差分模拟信号,满足ADS1278 的输入要求,共128 路。

ADSl278 是德州仪器公司推出的多通道、24 位、工业A/D 转换器。内部集成有多个独立的高阶斩波稳定调制器和FIR 数字滤波器,可实现8 通道同步采样,支持高速、高精度、低功耗、低速4 种工作模式;采样率高达128 KSPS。

ADS1278 的工作模式为MODE[1:0]=00,即高速模式,最高采样率为128 kSPS;数据输出格式为FORMAT[2:0]=000,即其接口协议为SPI 协议,输出模式为TDM,数据流格式是动态的。在TDM(分时复用)数据输出模式下,所有通道数据从单个管脚(DOUT1)成序列移出。通道1 的数据最先移出,到8 通道依次移出。

ADS1278 的输入为8 路差分模拟信号,参考电压为2.5 V,输出为串行的8 路数字信号。要实现同时采集128 路信号,则需要16 片ADS1278,这16 片芯片并行采集,将数据送入FPGA 的I/O 管脚。

具体的一片芯片ADS1278 与FPGA 的接口电路如图2所示。

图2 A/D 采样电路与FPGA 接口电路

2 系统整体设计

AD 信号采集模块中,能够对128 路差分模拟输入信号进行同步采样,采样数据的输出速率通过改变AD 器件的主时钟信号的频率来设定,AD 最大输出频率为105 kHz。为了减少信号连线,设计中16 个AD 控制信号由FPGA 统一发出,反馈信号及数据信号每个AD 与FPGA 直接相连,共使用FPGA 的I/O 端口35 个。

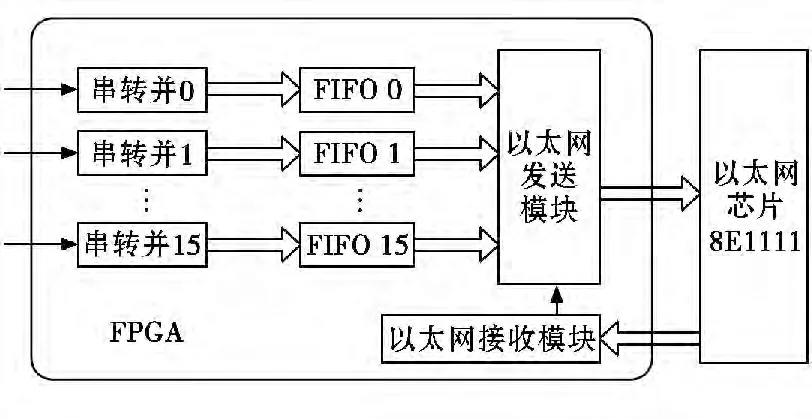

FPGA 与以太网芯片88E1111 采用GMII 接口连接,采用并行数据传输,时钟频率为125 M,其数据传输速度可达1 Gbit/s。通过以太网FPGA 可接受上位机命令,来控制发送模块是否发送数据。模块总体结构如图3 所示。

图3 模块总体结构简图

3 FPGA 程序设计

可编程逻辑器件FPGA 为Altera 公司的CycloneIV E 系列EP4CE40F23C8N 型号的FPGA,其核心工作电压为1.2 V、逻辑单元39 600 个、可自定义I/O 端口多达329 个、记忆单元1 161 216 个、锁相环4 个、全局时钟20 个。其内部功能模块如图4 所示。

FPGA 内部功能模块主要包括时钟模块、串并转换模块、FIFO 模块、以太网收发模块。时钟模块是由FPGA 内部集成的锁相环生成的。串转并是用于将AD 输出的串行数据转换为并行数据,将数据转换为八位并行以便用以太网进行传输,三个字节代表采样数据一个通道数据的采样点。FIFO 模块是用Altera 公司提供的IP 核设计,并利用FPGA内部的存储资源来生成的,主要用于数据的采集端与数据发送端的时钟匹配。本设计中串并转换和以太网发送模块工作时钟的频率与相位均不相同,两个模块之间的数据传输属于跨时钟域的异步传输,如果不加异步FIFO 很容易在传输过程中产生错误。

图4 FPGA 内部功能模块

4 以太网接口设计

88E1111 吉比特以太网收发器是一个物理层器件,用于1000BASE-T、100BASE-TX 和10BASE-T 类型的以太网,它是使用标准数字CMOS 工艺制造,并且包含所有所需的有源电路来实现物理层功能,以便在标准的CAT-5 类非屏蔽双绞线上发送和接收数据。

5 结束语

本设计充分利用了FPGA 并行处理能力强和以太网传输速度快的特点,实现了128 路采样数据向电脑实时传输的功能。经过测试,该信号采集模块在16 个AD 芯片128 通道同步采样,并且采样数据输出频率在100 kHz 的情况下工作稳定,数据传输正确,其采样数据的精度较高。

[1]朱康生,洪赢政,黄斌,等.ADS1278 在高精度数据采集系统中的应用[J].电子设计工程,2009,17(4):24-28.

[2]王南.基于DSP 和FPGA 的多通道信号采集模块设计[J].声学与电子工程,2010,2:28-30.

[3]郭富民.基于FPGA 和多核DSP 的高速图像传输与处理系统的设计[D].武汉:华中科技大学,2010.

[4]邹岩.基于嵌入式平台的语音信号采集系统设计[D].哈尔滨:哈尔滨工程大学,2013.

[5]Texas Instruments Incorporated.ADSl278 Data Sheet[DBI/OL].2007.http;//focus.ti.com/lit/ds/symlinlk/adsl278.pdf.