机载PowerPC系列高性能处理器模块硬件设计

2015-11-24李成文何小亚

杨 涛 李成文 刘 宇 何小亚

(中国航空计算技术研究所,陕西 西安 710065)

机载PowerPC系列高性能处理器模块硬件设计

杨 涛 李成文 刘 宇 何小亚

(中国航空计算技术研究所,陕西 西安 710065)

文章首先介绍了典型的高性能处理器并重点介绍了PowerPC系列的处理器,然后介绍了基于PowerPC系列高性能处理器的数据处理模块设计的技术总方案,最后通过一个具体的硬件模块的设计来详细说明机载PowerPC系列高性能处理器模块的硬件实现。

开发式综合化;可配置性;可测试性

随着计算机技术、通信技术的飞速发展, 向着高技术、高性能的目标发展。航空电子系统发展至今,已经历了分立式结构,集散式结构,集中分布式结构等几个阶段,目前正处于第四个发展阶段即开放式综合化阶段。第三代战斗机后期局部综合和第四代战斗机高度综合化的要求对数据处理能力提出了很高的要求,以传统1750A、80386、80486为核心处理器模块不能适应这种需求。因此,为了满足我国第四代飞机航空电子系统和现役飞机改进改型对高速数据处理能力的迫切需求,提出了高性能数据处理功能模块的研制任务。

1 典型高性能处理器

目前,比较有影响的RISC处理器产品有Compaq公司的Alpha、MIPS公司的MIPS、HP公司的PA-RISC、Sun公司的Sparc和IBM公司的Power PC。 这5种RISC处理器性能都很高,具有各自的优势,但综合考虑到PowerPC处理器在嵌入式系统和军事领域应用情况良好以及PowerPC架构的处理器具有可伸缩性好,方便灵活的特点,而且PowerPC处理器品种很多,既有通用的处理器,又有嵌入式控制器和内核,有众多的厂商支持,应用范围非常广泛,因此高性能处理器模块使用PowerPC系列处理器具有更多的优势。

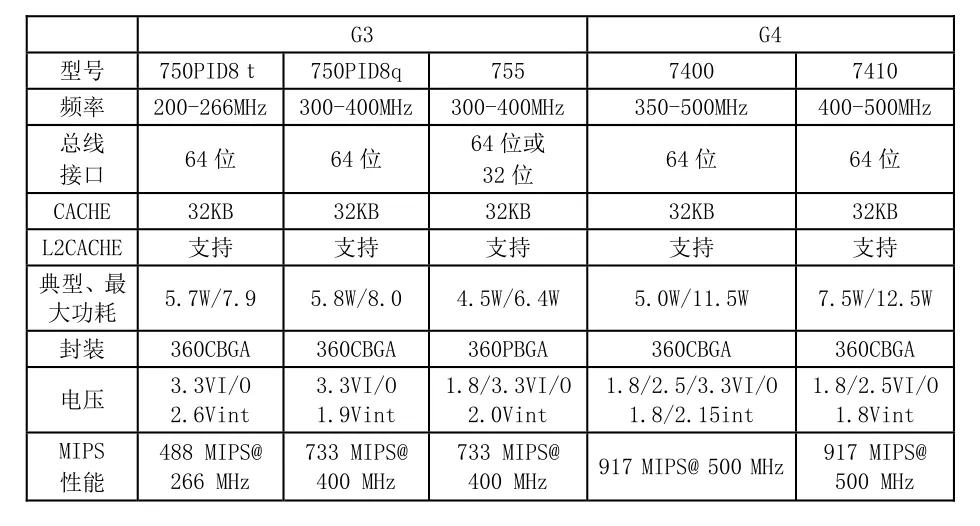

机载环境是一种典型的嵌入式应用环境,新一代机载计算机对于微处理器的处理能力、实时性和测试能力都有极高的要求。PowerPC系列处理器中的8xxx系列、60x系列和7xx系列、74xx系列均为强处理能力的嵌入式处理器。其中 7xx系列、74xx系列是PowerPC系列处理器中的高性能处理器,7xx系列为第三代高性能的处理器,它与第四代高性能的处理器PowerPC 74xx保持代码和引脚兼容,PowerPC G3和G4系列数据处理比较如表 1。因此选择以 PowerPC750、PowerPC755、PowerPC7410为核心来研制新一代机载高性能处理器模块。

国外DY4、THALES、PENTEK、SPECTRUM、RADSTONE为代表的公司较早研制出以PowerPC系列处理器为核心的高速数据处理功能模块,形成了以VME为主的底板总线、结构尺寸为3U、6U的标准PowerPC系列高性能处理器模块,并且已经广泛应用在B-1、F-16D、F/A-18、JSF、AV-8B、GDIS、F22等许多战机以及NASA航天飞机上。

机载PowerPC系列高性能处理器模块主要研究数据处理模块的可配置技术、高速设计技术、模块小型化等等设计技术,目标是研制出一组可配置、可测试、可升级的高性能数据处理系列化模块以及配套的软件和开发工具,为第四代飞机航空电子系统和第三代飞机航空电子系统综合提供功能较强的数据处理系列模块。

表1 PowerPC G3 G4比较

2 技术总方案

PowerPC系列高性能数据处理模块研制目标是为机载电子系统提供高性能的军用计算机以及良好的软件开发环境,因此产品应适应机载环境,提供实时系统所需要的特殊功能。除此之外,产品尽可能通用化,不局限于某个具体的型号,也不局限于某个具体的子系统。

PowerPC系列高性能数据处理模块设计的核心在于机载数据处理机体系结构的研究,软件开发平台的建立以及南桥北桥芯片的使用设计等技术。国外提供的PowerPC北桥芯片只有商用器件,高性能的军用芯片经常被国外控制甚至禁运;军用数据处理和商用的数据处理机要求有差异;嵌入系统设计要求小型化。基于上述原因确立了以下设计原则:

a.设计系列化的数据处理模块;

b.提供高性能的数据处理能力;

c.产品设计应具有通用性,并具备功能扩展能力;

d.提供实时系统所需的特殊功能,如看门狗,超时中断等;

e.开发集成南北桥的逻辑电路;

f.提供多级中断及例外处理能力;

g.提供软件开发环境包括(实时操作系统、BIT、驱动);

h.提供适应机上供电环境的电源。

根据上述设计原则,在大量调研的基础上,笔者确立了以下研究方法和实现方案。

2.1 模块可配置性研究

在以前的实践中,模块化、通用化的最大困难是由于传统的SRU模块的组装密度不够,仅能够安装模块功能所必须的元器件,不能覆盖大多数应用对资源的需求,而且没有扩充余地,导致模块通用化程度的降低,从而给通用模块的推广造成困难。如何使模块的功能最大程度地满足不同应用的要求、对模块进行合理的划分、采用何种接口结构是模块研制的关键所在。

可配置是通过设计技巧,实现模块了容量、性能、功能的可配置性。笔者采用了以下几种方法提高系统的可配置性:

a.采用可编程器件;

b.采用背板结构;

c.采用跳线;

d.采用兼容器件;

e.采用开放式标准。

2.2 模块可测试性研究

PowerPC系列高性能数据处理模块大量采用BGA和表帖封装,组装密度非常高,给模块调试、测试、维修带来很大麻烦。因此在模块设计是必须对模块的可测试性进行研究。模块测试主要手段是软件BIT,因此要考虑BIT 对系统综合的支持、硬件电路的可测试性设计等方面的内容。

可测试性是最后要落实到电路设计上,采用以下设计能有效提高电路测试性:

a.硬件可读状态点;

b.寄存器可回读;

c.特殊的可测试电路;

d.对外部接口设置回绕测试支持;

e.测试电路要求考虑软件层进行故障检测,如超时,看门狗电路等;

f.设置故障隔离,减少故障蔓延;

g.可以设计专门的测试总线,如IEEE 1149.5。

2.3 模块高速电路设计研究

设计高性能处理器模块必须突破了高速电路设计的技术难关,对外频超过100MHz的数字部分进行准确分析和设计。研究以下内容:

a.信号完整性分析和电路设计的关系;

b.关系元器件选型,印制板层叠关系,布局布线等;

c.信号完整性和生产的关系;

d.要求进行信号完整性分析后,指导我们的模块材料选用,误差控制等工作;

e.高速信号的测试问题。

2.4 模块三化研究

计算机系统的通用化、系列化、模块化一直是军用机载计算机系统追求的目标,是降低研制费用和维修费用,提高作战能力的重要技术途径。

我们设计高性能处理器模块要使硬件资源和软件配置通用化,方便系统维护和产品升级的一致性。形成以下几个系列的标准模块:

a.结构尺寸:以3U、6U、1/2ATR、3/4ATR、PMC尺寸的系列模块;

b.底板总线:以LBE总线、VME总线、CPCI总线,PCI总线为接口的标准模块。

3 模块硬件设计实例

3.1 模块组成

PowerPC 系列高性能数据处理模块采用MPC750/755/7410处理器,存储器控制器/PCI桥接器采用Motorola 公司的MPC107。

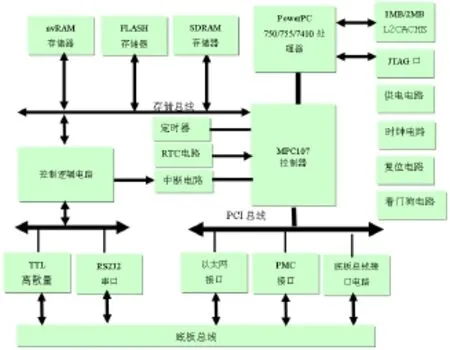

PowerPC系列高性能数据处理模块基本上包括以下功能块:

a.复位电路;

b.时钟电路;

c.供电电路;

d.看门狗电路;

e.中断电路;

f.RTC电路;

g.定时器;

h.处理器PowerPC750/755/7410;

i.L2高速缓存;

j.PCI总线桥及存储器控制器MPC107;

k.存储器系统:SDRAM,USER Flash™,SYSTEM Flash™,NVRAM;

l.离散量I/O;

m.TRACE32接口;

n.以太网接口;

o.串行调试接口;

p.底板总线接口电路。

图1是PowerPC系列高性能数据处理模块结构框图。

图1 PowerPC系列高性能数据处理模块结构框图

3.2 硬件配置

3.2.1 处理器

处理器是采用 MPC755,其最高工作频率为 400MHz。处理器的工作频率可由跳线设置,工程样机中其工作频率设计为300MHz。

考虑数据处理模块处理器的可升级性,设计MPC750/755/7400/7410处理器向上兼容,工作频率范围为200MHz~500MHz。

3.2.2 存储器

数据处理模块上设计有 L2 Cache 、SDRAM存储器、SYSTEM FLASH存储器、USER FLASH存储器和nvSRAM存储器,其配置见表2 。

表2 数据处理模块存储器配置

3.2.3 时钟电路

数据处理模块设计了3.3V 25MHz 、3.3V 33MHz、3.3V 64MHz、5.0V 64MHz四种时钟。

25MHz时钟用于以太网电路。

33MHz输入到MPC107上,由MPC107产生5路33MHz同步时钟供PCI设备使用,MPC107内部实现时钟锁相环电路,经MPC107中的DLL产生4路66MHz同步时钟供SDRAM使用, 另外产生1路66MHz同步时钟供MPC750处理器使用。

64MHz使用 2种电压(3.3V和 5.0V)的时钟 ,5.0V 64MHz时钟固定给VME总线接口芯片UNIVERSEII使用,3.3V 64MHz时钟送FPGA芯片供CCDL电路使用,另外在FPGA芯片中用64MHz时钟8分频得到16MHz时钟,16MHz时钟给串行接口芯片ST16C2552使用。考虑CCDL电路传输速率的变化和高频时钟走线短的需要,因此3.3V 64MHz没有与5.0V 64MHz共用一个时钟。

3.2.4 供电电路

数据处理模块上有 2.0V、2.5V、3.3V和 5.0V四种电压,2.0V为处理器MPC755的内核电压,2.5V为MPC107内核电压,3.3V为处理器和107桥的接口电压,5.0V供PCI和VME总线接口电路使用。2.0V电压工作电流(在3.0A左右)很大,如果由5.0V经DC-DC线性转换电路转换得到,电源损耗很大从而导致发热量大,因此 2.0V电压拟采用开关DC-DC转换电路转换得到。另外考虑到开关DC-DC买不到军品器件,而且首次设计有一定的风险,因此设计中还保留使用DC-DC线性转换电路。2.5V工作电流(0.3A左右)电流小,可由5.0V经DC-DC线性转换电路转换得到。在原理样机中3.3V由电源模块提供,这给数据处理模块单独调试和维护维修带来很大的不方便甚至出现模块加电顺序不当导致模块损坏的现象,另外3.3V的工作电流(0.5A左右)不大。因此在工程样机中数据处理模块的3.3V也由5.0V经DC-DC线性转换电路转换得到。5.0V电压由VME总线(来自电源模块)提供。

3.2.5 供电电路

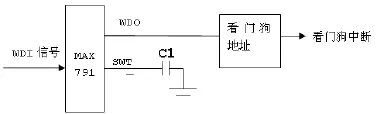

看门狗电路采用MAX791和FPGA实现。当看门狗功计时器溢出后,产生看门狗中断。看门狗中断由GSE和软件看门狗使能位WDOEN来控制。GSE*为高电平时,系统处于空中状态,看门狗中断自动使能;当 GSE*为低电平时,系统处于地面调试维护状态,看门狗中断通过软件使能位WDOEN来控制,WDOEN为‘0’时,使能看门狗,WDOEN为‘0’时,禁止看门狗。看门狗电路产生中断后,送入中断电路,同时也送给通道故障逻辑电路。正常使用时要求用户必须在小于 1秒间隔内产生看门狗触发,使看门狗重新开始计数,以防止产生看门狗中断。看门狗控制电路如图4所示。

看门狗定时周期可以由用户自行配置。定时周期由硬件设置,缺省(SWT通过跨接跳线S1接VCC)为1.6S。在不跨接S1的情况下,改变电容C1的值,可改变看门狗定时周期。定时周期period按公式1计算:

period=2.1 x C1ms(其中 C1的单位为 nf,且C1>4.7nf)--------(1)

图2 看门狗控制电路

看门狗软件使能地址为0x7C000000,数据位为D15;看门狗软件喂狗地址为0x7C000008,数据位为D15。

3.2.6 中断电路

中断电路采用MPC107桥接器芯片和FPGA实现。

中断控制器实现16级外部串行中断。中断优先级软件可以设置,设置范围为0~15,其中15为最高优先级。设置为0时,禁止该级中断。中断资源分配见表3。

表3 中断资源分配表

除了外部中断信号外,POWERPC750还响应一种优先级更高的外部事件,即MCP中断。它由FPGA产生,直接送给处理器的MCP。MCP中断源见表4。

表4 MCP中断分配

3.2.7 MPC107

中断电路采用MPC107桥接器芯片和FPGA实现。

中断控制器实现16级外部串行中断。中断优先级软件可以设置,设置范围为0~15,其中15为最高优先级。设置为0时,禁止该级中断。中断资源分配见表3。

MPC107PCI桥接器/集成存储器控制器提供MPC6XX,MPC7XX,MPC74XX处理器到PCI总线的接口。MPC107提供功能有:一个高性能的存储器控制器,两处理器的支持,两通道DMA控制器,一个中断控制器,一路I²O消息控制器,一路I²C接口,一个时钟锁相环电路。MPC107内部有配置寄存器,配置寄存器基地址为 0XFEC00000。具体的配置寄存器定义及说明参见MPC107用户手册。

MPC107 主要特性如下:

a.存储器接口:32位或 64位数据宽度,频率最高100MHz。支持 SDRAM。支持 8位,32位,64位SYSTEMROM。支持数据校验,读更改写操作。支持ECC;

b.处理器接口:处理器总线时钟可达 100MHz;支持第二个处理器;支持MPC6XX,MPC7XX,MPC74XX处理器;支持存储器一致性;32位或 64位数据宽度,32位地址;

c.PCI接口:兼容PCI2.1规范;32位PCI接口,操作频率可达50MHz;5.0V兼容;可选大端小端操作;提供多达五个PCI设备的仲裁电路;校验支持;

d.其它特性:2通道 DMA控制器;消息管理单元;I2C控制器;可编程中断控制器;集成PCI,SDRAM时钟产生;可编程存储器和PCI总线驱动;

e.测试特性:测试点监视;存储器和 PCI属性信号;JTAG/COP接口。

3.2.8 底板总线接口

数据处理模块使用 PUniverseII接口芯片实现标准的VME64总线主从设备接口,通过VME总线接口,数据处理模块可以访问本通道 VME总线上的各个设备,也可以被本通道VME总线上的其他主设备访问。桥接芯片支持VME64总线进行块传输,同时支持VME总线进行DMA操作。

Universe II 提供标准的PCI总线接口支持32位PCI和64位PCI设计。Universe II连接PCI设备不需要额外的驱动电路和逻辑,所有的PCI信号直接连接。如果Universe II配置为32位PCI接口,则信号AD[32:63]不接,ACK64#信号上拉。

3.2.9 离散量

状态离散量输入包括以下几个信号:

a. GSE*:TTL电平,地面支持使能信号,当GSE*为低电平时,表示系统处于地面开发或维护测试状态;当 GSE*为高电平时,表示系统处于实时工作状态。

b.STATUS0:用于定义模块状态,由软件定义;c.STATUS1:用于定义模块状态,由软件定义;

d.MG0-MG4:槽位标识号,用于确定本模块所在的槽位。

以上离散量状态可以通过FPGA内部离散量状态寄存器查看,离散量状态寄存器地址为 0x7c000000,只读。离散量状态寄存器格式如图3所示。

图3 离散量状态寄存器格式

4 结束语

本文通过一个具体的硬件模块的设计来详细说明机载PowerPC系列高性能处理器模块的硬件实现,关于模块的软件配置及开发环境、信号完整性分析则是另外需要进行专题研究的部分。

[1]梅云华.综合模块化航空电子设备中的嵌入式计算机平台设计[J].计算机与现代化,2013,(12):188-191.

[2]陈海荣.基于双核 PowerPC处理器的高性能计算模块设计[J].计算机测量与控制,2011,(19):2824-2827.

[3]刘冰,孙爱中.基于 PowerPC处理器的单板计算机设计和实现[J].电子科技,2004,(6):163-166.

[4]沈华,汤彦飞,李乔杨.PowerPC处理器的发展历程[J].计算机光盘软件与应用,2013,(6):73-74.

Airborne PowerPC series high-performance processor module hardware design

This paper first introduces the typical high performance processor and introduced PowerPC processor series, and then introduces the data processing module design based on PowerPC series high-performance processor technology total solution, finally through a concrete hardware module design to detailed airborne PowerPC series high-performance processor module of the hardware implementation

Open integration; configurability; testability

V271.4

A

1008-1151(2015)05-0001-04

2015-04-13

杨涛(1981-),男,陕西武功人,中国航空计算技术研究所工程师,硕士,研究方向为机载计算机硬件设计与调试。