基于国家标准的UHF RFID读写器数字基带系统设计

2015-11-10赵伟熊卫华季瑞松

赵伟+熊卫华+季瑞松

摘 要:主要介绍了一种符合国家标准的超高频RFID阅读器的数字基带系统的设计与分析,该基带部分的编解码主要依靠FPGA来实现。文中首先对800/900 MHz频段的射频识别系统空中接口协议的国家标准GB/T 29768-2013作了简要介绍,对系统的整个编解码系统的实现以及整个系统的架构和各个模块作了详细说明,最后给出了该读写器工作时抓取的数据波形。

关键词:读写器;FPGA;国家标准;TPP;FM0

中图分类号:TN929.5 文献标识码:A 文章编号:2095-1302(2015)10-00-03

0 引 言

射频识别技术RFID(Radio Frequency Identification)是一种依靠无线射频的电磁波来传播信息并且可以自动识别的非接触式通信技术。因为其具有非接触性、读取灵敏度高等优势,因此广泛运用于物联网技术领域以及物流、生产、交通等需要实时通信的领域[1]。

本文中主要介绍了一种使用FPGA来实现读写器基带系统的编解码部分功能的设计方案,基于新进颁布的UHF国家标准GB/T29768-2013协议,由FPGA来进行前向链路的TPP编码和后向链路的FM0/miller解码。这种方式可对标签传送的数据实现较快地解码。文中的FPGA选用的是ALTERA公司的EP4CE30F484芯片。本文着重描述了设计中软件部分的核心内容。

1 RFID系统简介

通常来说,常见的RFID系统主要由高频或超高频读写器、有源或无源标签、天线以及与通信末端连接的上位机等组成。读写器与标签之间的通信通过天线进行传递。RFID的区分可根据工作的频段划分为中频、高频、超高频,本文所讨论的RFID系统工作频率为920-925 MHz的超高频RFID。在一个完整的RFID系统中,读写器是一个具有多种功能的不可或缺的部分,因为首先读写器必须能够同时接收和发送数据且具有对其处理的能力,所以,其在与电子标签通信的同时也要向末端传输数据并执行相关的操作指令。一般的读写器系统主要划分为两个部分,即对数字信号进行处理的基带部分以及负责射频前端的射频部分,本文着重介绍的是数字通信的基带部分[2]。

2 UHF RFID 相关协议的介绍

由于超高频RFID技术是一种近年才兴起的无线通信技术,该技术在国际上尚无一种统一的标准协议,目前比较流行的协议主要有ISO18000-6B/C协议、EPC C1G2协议等,其基带系统所使用的编解码技术差别不大,较为成熟。我国为在这一新兴的前沿技术上占据主动权,近年来国家大力发展基于RFID技术的物联网行业,同时颁布了UHF RFID(800/900 MHz)的国家标准协议GB/T 29768-2013。该标准具有识别速度快、可读标签数量多、群读能力强、可存储空间大、包含多种加密方式的保护方式安全性强等众多优点。下文将着重介绍该国标的编解码方式。

2.1 TPP编码介绍

GB/T 29768-2013协议规定读写器向标签发送数据的链路(前向链路)的数据编码方式采用TPP编码。读写器给标签发送数据时,必须以前导码来开始所有的数据通信。前向链路中必须使用如图1所示的由分隔符、校准符一、校准符二组成的前导码通信。其中允许的校准符一和校准符二的长度误差为±1%,而分隔符的允许误差为±5%。

图1 前向链路的前导码

在接收到前导码后,当两个间隔时间的连续上升沿脉冲被标签测定,标签的解码应按照以下方式进行:

(1)当检测到的脉冲的时间间隔小于时间Pivot1,则此时被解码的符号应为00;

(2)当检测到的脉冲的时间间隔小于时间Pivot2但是又不小于时间Pivot1,则此时被解码的符号应为01;

(3)当检测到的脉冲的时间间隔不小于时间Pivot2但是又小于时间Pivot3,则此时被解码的符号应为11;

(4)当检测到的脉冲的时间间隔不小于时间Pivot3时,则此时被解码的符号应为10。

图2所示的编码符号即为TPP编码,2Tc即为符号00的持续时间,3Tc即为符号01的持续时间,同理,4Tc为符号11的持续时间,持续时间5Tc为符号10的持续时间,±1%的长度允差为这四种符号所允许。一个Tc的时间长度可以取为6.25?s或12.5 ?s,该时间长度允许误差为±1%,固定的Tc应该被使用在读写器的一个盘点周期内,本设计中Tc选取为6.25 ?s[3]。

图2 TPP编码符号

2.2 FM0/miller编码介绍

GB/T 29768-2013标准规定读写器对标签发挥的数据译码采用FM0编码或者Miller编码两种形式,两种编码的本质是没有区别的,虽然Miller码的抗干扰能力较强,但是它的编码速度比FM0编码要慢许多。本次设计采用了FM0编码的方式,FM0(Bi-Phase Space)全称是双相间隔码编码,采用一个由高电平到低电平或者由低电平到高电平的电平转换组合来表示数据0,数据1表示为一个单独的高电平或者低电平。数据0和1编码所占的时间周期是一样的。具体编码规则是在半比特周期中任意边沿且在每一比特周期开始时电平都要反向,图3给出了FM0的基本符号图形[4]。

图3 FM0编码符号

3 系统总体设计

本文中读写器的设计采用MCU+FPGA协同工作的方式。其中,FPGA主要用于数字基带部分对数字信号进行相应的解编码处理,MCU采用的是基于ARM Cortex-M3内核的STM32F207芯片,MCU部分主要负责整个系统的逻辑控制功能。FPGA主要包括协议控制及命令产生模块、TPP编码模块、FM0解码模块以及同MCU进行数据通信的SPI模块部分。

整个基带系统的工作过程为:FPGA对读写器需要发送的Query命令数据以及相应的CRC校验位进行TPP编码,完成编码后将TPP码送至前端射频部分。射频部分对该数字编码通过混频器进行载波调制(ASK),调制后的信号经混频器和耦合器再经天线向射频场内进行发射。

读写器的信息被射频场内的电子标签接收到后,标签根据读写器发送来的命令参数,选择对应的编码方式,首先对读写器的信息进行解码,之后对要回复的数据进行编码,经调制之后在空间射频场内传播。

当场内标签反射回的信息经过天线被读写器接收后,该未经解调的信号被转至读写器的接收模块部分。该标签返回的信息首先经过读写器接收模块对其进行解调,信号经过解调后被后级的滤波器以及ADC转换器转化为0和1的数字信号流,然后接收到该数字流FPGA中相应的解码模块会根据MCU发出的控制信号对其进行相应的FM0解码或miller解码。经过解码模块解码后的信号将会被FPGA内部的控制模块和命令模块接收处理判断后产生下一轮的命令数据,该命令数据用于决定读写器是否与标签进行重新交互信息或者读取新的标签[5]。

4 基带系统的FPGA实现

系统中的FPGA主要功能为实现基带的编码与解码功能,FPGA内部分为TPP编码模块与FM0/miller码解码模块。

4.1 TPP编码模块设计

在GB/T 29768-2013标准中,前向链路(发射链路)的数据编码使用TPP编码进行编码。当PC端通过MCU发送命令指令和数据后,MCU将会给FPGA发送控制指令用以启动编码。TPP编码模块接收到该指令后将会返回应答信号,MCU收到返回的应答信号后将需要编码的数据送入TPP模块。当FPGA完成数据编码后,编码模块需对CRC值进行编码。TPP编码输出的每一帧数据都由一个前导码、8位数据位组成,前导码封装成帧头[6]。该TPP编码模块的具体实现方式为:当检测到NRZ码输入为00时,TPP码输出1个Tc时间长度的高电平和1个Tc时间长度的低电平,相当于NRZ码的10;当输入的NRZ码为01时,TPP码输出2个Tc时间长度的高电平和1个Tc时间长度的低电平,此时相当于NRZ码的110。依次得出符号11的TPP码相当于NRZ码的1110,符号10相当于TPP码的11110。

TPP编码模块的处理流程如图4所示[7]。

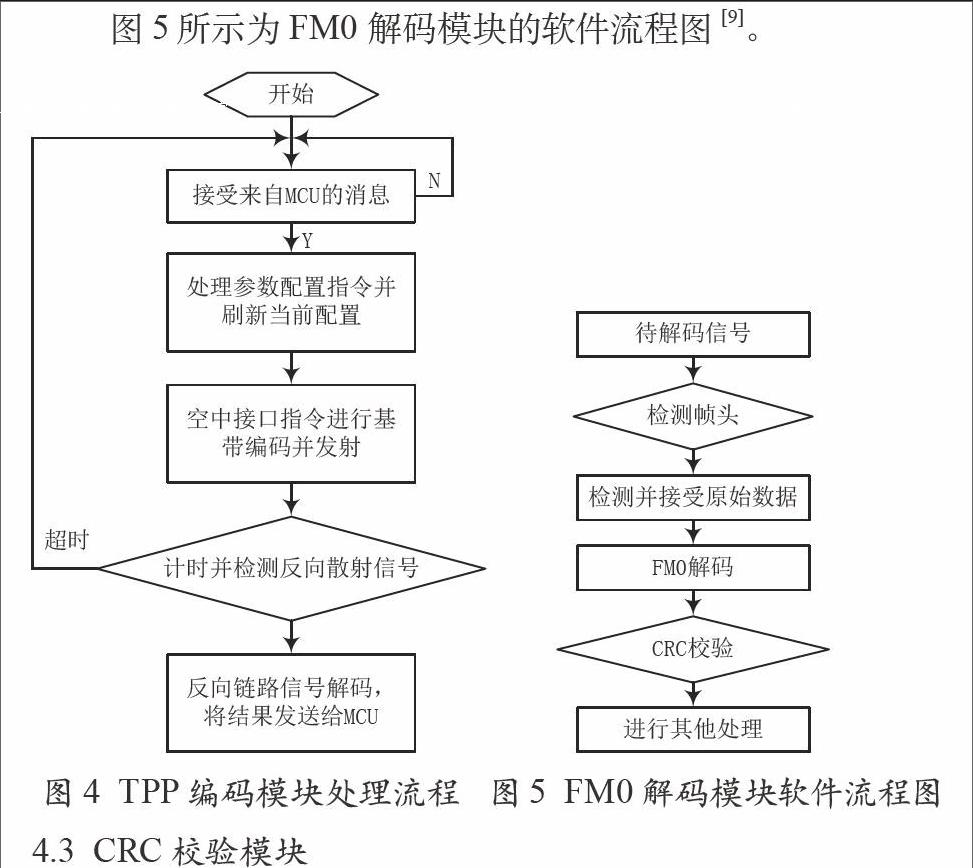

4.2 FM0译码模块设计

根据GB/T 29768-2013标准,标签向读写器返回的信息链路(反向链路)的编码方式采用FM0编码或miller编码。本设计采用FM0编码模式。该编码模块的具体实现方式如下:当模块接收到开始解码命令后,编码模块对模块内进行初始化操作。后对数字化后的标签返回的信号进行检波,检测前导序列以及是否存在帧起始信号(V字符),当前导序列码正确及无帧结束信号后[8],该解码模块对数据段进行FM0解码,对每个码元进行解码主要靠该码元内高低电平的时间长度来判断0或1信号。该模块将解码后的数据实时串并转换并存入缓存区。

图5所示为FM0解码模块的软件流程图[9]。

图4 TPP编码模块处理流程 图5 FM0解码模块软件流程图

4.3 CRC校验模块

CRC校验模块主要用来在基带系统译码时对接收的信号进行完整性校验,使得MCU对FPGA的各个模块进行操作控制,根据GB/T 29768-2013标准规定,x16+x12+x5+1为本设计使用的CRC-16校验码的生成多项式,二进制数FFFFh被预加载进16位寄存器中,此CRC计算是按高位优先原则由高位到低位进行的。CRC-5的生成多项式为X5+X3+1,5位寄存器预加载01001b,按高位优先原则进行CRC计算[10]。

4.4 时钟分频模块

本设计中FPGA的工作时钟频率为50 MHz,FPGA内部各模块所需的数据速率与FPGA工作频率不同,所以该FPGA内部需时钟分频模块来产生各个模块所需时钟频率。在本设计的TPP编码中,1个Tc的时间长度为6.25 ?s,所以TPP模块所需的时钟频率为80 kHz,该时钟频率即由分频模块分频所得。文中解码模块部分FM0所需始频率为160 kHz。所以时钟分频模块需要产生160 kHz和80 kHz两种工作频率[11]。

5 软件仿真

以上各模块均使用Verilog描述语言来实现。图6所示为使用QuartusⅡ软件在读写器读写标签时所抓取的实时波形,从图6中可得出标签在收到读写器发送的命令后返回的信号解码后为110100010100,即为一个RN16信号。

图6 命令发送及标签信息的返回波形

6 结 语

本文介绍了在国家标准空口协议GB/T 29768-2013的框架下,充分利用FPGA的优势即可以快速处理大量数据流的特点,解决了读写器读取标签速率难以提升这个一直无法有效解决的难题,从而实现了UHF RFID读写器中编解码模块的设计。设计经过了软件仿真与实际硬件测试,软件与硬件的测试结果均显示该设计的读写器工作良好,且基带部分编解码的速度、读写器的性能均得到显著提升。

参考文献

[1]董敏.超高频RFID读写器数字基带技术研究[D].成都:成都理工大学,2012.

[2]陈佳雷.基于FPGA的UHF RFID读写器数字基带部分的研究与设计[D].南京:南京邮电大学,2012.

[3] GB/T 29768—2013信息技术射频识别800/900 MHz空中接口协议[S].中国国家标准管理委员会,2015-05-01.

[4]冯守虎.UHF RFID阅读器的数字基带技术研究[D].南京:南京邮电大学,2011.

[5]于志宏,张红雨.UHF RFID读写器编解码模块的FPGA实现[J].单片机与嵌入式系统应用,2012,12(10):12-15.

[6]陈杨.基于FPGA的UHF读写器设计[D].成都:电子科技大学,2012.

[7]陈小军.基于FPGA的超高频RFID网络读写器设计[D].成都:电子科技大学,2013.

[8]于志宏.基于EPC C1G2协议的UHF RFID基带系统及验证平台的设计与实现[D].成都:电子科技大学,2013.

[9]林宇.基于AS3992的UHF RFID读写模块的研究与开发[D].上海:华东理工大学,2012.

[10]许静.UHF RFID读写器数字基带系统的设计及其防冲突算法研究[D].长沙:湖南大学,2011.

[11]阳璞琼.超高频RFID系统编解码与校验问题的研究[D].长沙:湖南大学,2009.