基于SoPC的伺服控制器的方案研究

2015-10-26代俊锋穆欣

代俊锋+穆欣

摘 要:传统伺服控制器中常用的运算芯片是TI公司的28系列芯片,属于ASIC芯片,厂家已为用户提供了一些常用且固定的外设模块,用户不能随意增删或修改其功能。但随着越来越多的专用伺服系统的出现,这些固定的外设资源已经不能适应伺服开发厂商的需要。由此提出了基于SoPC的伺服控制器,使用FPGA芯片来定制所需的CPU软核和需要的外设,将电流环调节器实现硬件化、并且使ADC和SVPWM等模块实现可定制化,由此满足开发需要。其除了具有SoPC技术本身的优点之外,还实现了传统伺服控制构架无法实现的功能和性能,例如,利用硬件实现MT法速度采样及电流采样均值滤波处理。经验证该设计方案可行且在功能和性能上优于传统伺服控制器构架。

关键词: SoPC; FPGA; NIOS Ⅱ; 伺服控制器

中图分类号: TN701?34 文献标识码: A 文章编号: 1004?373X(2015)20?0150?04

Scheme research of SoPC?based servo controller

DAI Junfeng1, MU Xin2

(1. Beijing Shoke Catch Electriccal Technology Co., Ltd., Beijing 102200, China; 2. Beijing University of Technology, Beijing 100124, China)

Abstract: The common operation chip in traditional servo controller is TI 28 series chip in traditional servo controller, which belongs to ASIC chip. The common and fixed peripheral modules are provided by manufacturers for the users, and but its functions cant be added, and deleted, or modified by users optionally. With the increasing appearance of special purpose servo systems, these fixed peripheral resources are unable to meet the requirements demands of the servo development firmmanufacturerss. Therefore, a SOPC?based servo controller is presented, in which. FPGA is used to customize the needed CPU soft core and peripherals, the current loop regulator is achieved by hardware conversion, and the customization of ADC and SVPWM modules are reached to, which meet the needs of development. The proposed controller has the advantages of SOPC itself, and can realize the function and performance that the traditional servo control framework cant be implemented. The verification results prove that the design scheme is feasible, and better than the framework of traditional servo controller in the aspects of function and performance.

Keywords: SOPC; FPGA; NIOS Ⅱ; servo controller

0 引 言

目前SoPC技术已经被广泛应用到了许多场合,其开发周期短、设计灵活、直接面向用户等优点是其迅速发展的原因。FPGA是实现SoPC技术的一种方式[1]。本文相对于传统的伺服,采用Altera的FPGA,提出了一种基于SoPC技术的伺服控制器设计和开发方案。并利用DSP Builder,Eclipse等工具,实现了对此方案的验证工作,在此过程中设计和实现了具有自主知识产权的IP 核,其中包括:电流环PI调节算法的IP核、SVPWM IP核、SPI接口电流采样IP核、MT法测速IP核等,由此可更有效地保护自主知识产权。

1 方案设计

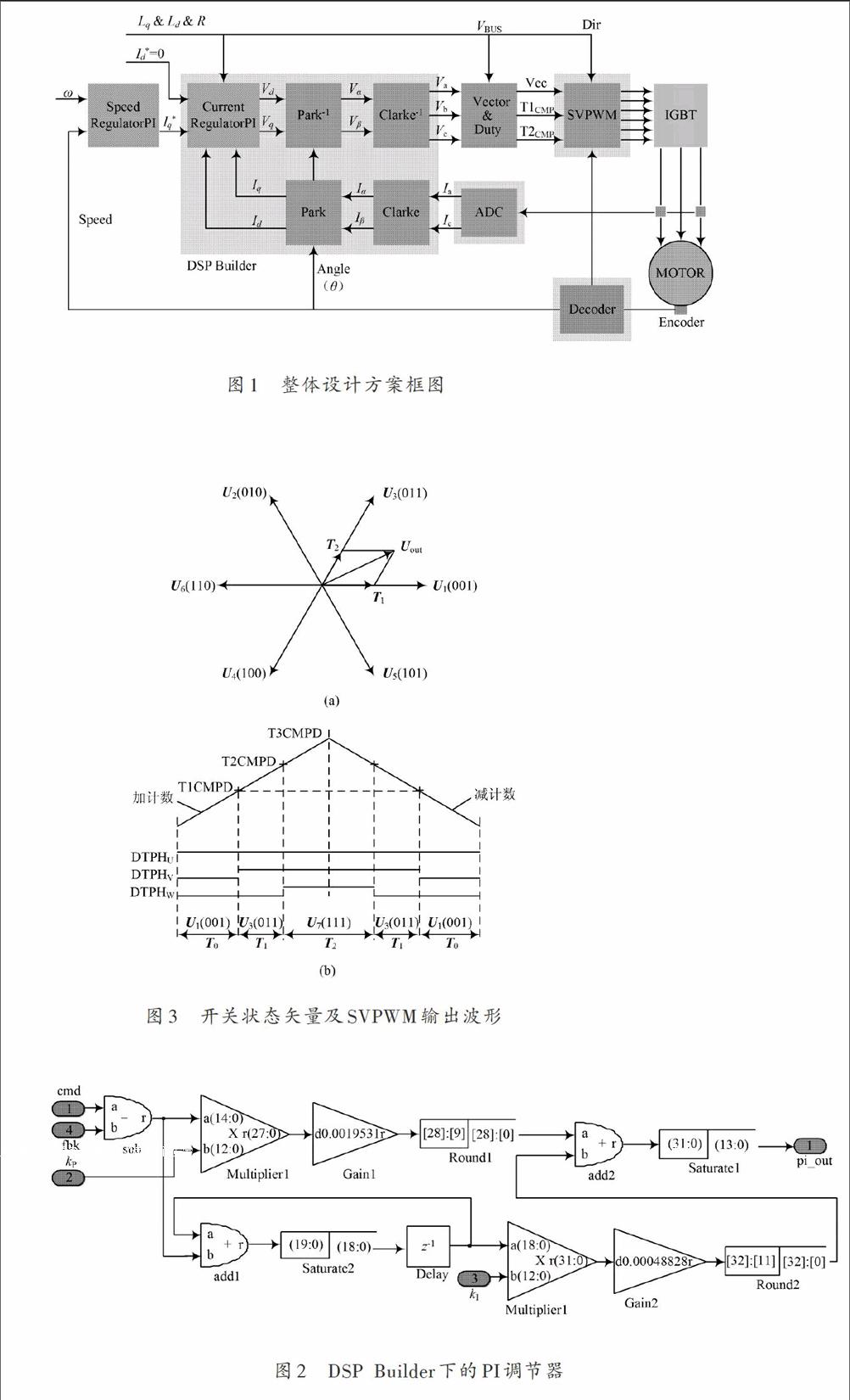

整体设计方案的示意图如图1所示,其中ω为速度指令,经过速度调节器处理后生成电流指令Iq并被送入电流调节器,然后经过Park?1和Clarke?1变换实现直交和[23]变换,结果送入SVPWM模块生成PWM波,并由此控制IGBT桥臂的开关动作,以实现对电机三相电流的控制。

在反馈部分,电流采样由ADC模块实现,并经由Clarke和Park变换后,结果送入电流环调节模块中,电机编码器的信号经Decoder模块接收后转变为位置信息和速度信息,然后被送入调节和转换模块。在整个环节中,除速度调节部分由软件实现外,其他部分全部由DSP Builder及Verilog硬件描述语言等工具以硬件的方式实现,由此可有效增加电流环频率和降低CPU负担[2]。endprint

图1 整体设计方案框图

1.1 电流环调节

这里采用PI(比例、积分)调节器作为电流环调节器,比例控制是一种最简单的控制方式,其控制器的输出与输入误差信号成比例关系,当仅有比例控制时系统输出存在稳态误差。在积分控制中,控制器的输出与输入误差信号的积分成正比关系。对一个自动控制系统,如果在进入稳态后存在稳态误差,则称这个控制系统是有差系统[3]。为了消除稳态误差,在控制器中必须引入“积分项”。如果系统存在稳态误差,则随着时间的增加,积分项会增大,即便是误差很小,积分项也会随时间的增大而加大,它推动控制器的输出增大使稳态误差进一步减小,直到等于零。因此,比例积分(PI)控制器,可以使系统在进入稳态后无稳态误差。在这里以DSP Builder为工具,设计实现PI调节器,其程序框图如图2所示,其输入包括:指令cmd、反馈fbk、比例增益kP、积分增益kI,输出为pi_out。由此搭建的程序经过DSP Builder编译后生成VHDL文件,之后集成到Quartus Ⅱ工程中实现调节功能。

图2 DSP Builder下的PI调节器

1.2 SVPWM模块

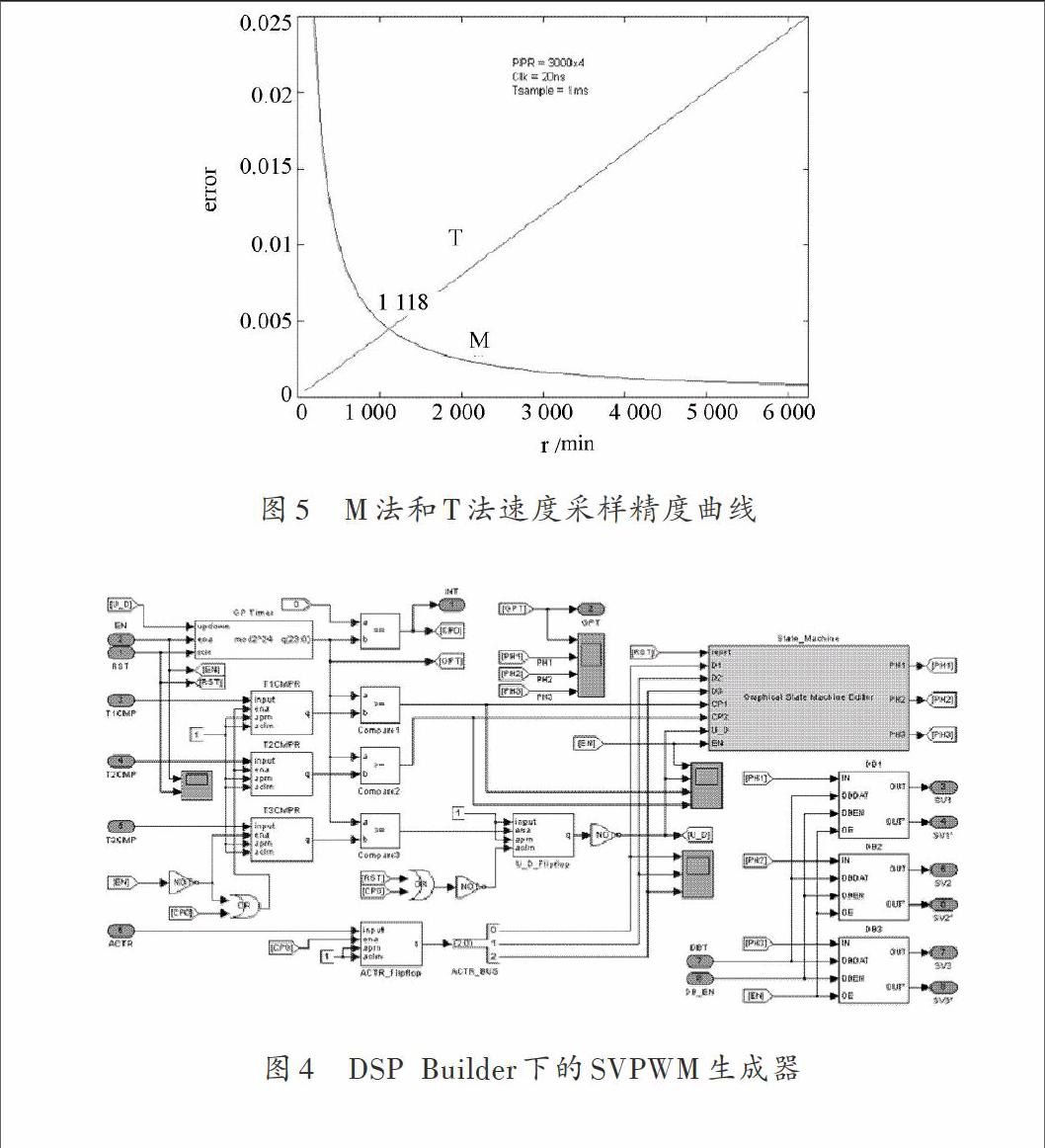

如图3所示采用包含死区功能的5段空间矢量合成方式,共有8种安全的矢量状态,其中U0(000),U7(111)这两种开关状态在电机驱动中都不会产生有效的电流,因此称其为零矢量。另外6种矢量状态分别是U1(001),U3(011),U2(010),U6(110),U4(100),U5(101),它们将360°的电压空间分为60°一个扇区的6个扇区,利用这6个基本有效矢量和2个零矢量,可以合成360°内的任何矢量[4]。

利用DSP Builder绘制的逻辑图如图4所示,其中有一个24 b的计数器和3个比较器,将当前计数器及比较器的状态作为输入送入状态机中获得PH1,PH2,PH3三项逻辑值,然后经过死区处理分出SV1,SV1*,SV2,SV2*,SV3,SV3*六路PWM信号波形。本设计的特点是可根据使用需要,通过T3CMP寄存器修改和调整PWM周期;如果需要由5段式PWM改为7段式PWM,或者由中心对齐式改为边缘对齐式,都是比较容易做到的。

图3 开关状态矢量及SVPWM输出波形

1.3 电流采样

由于选用的Altera的FPGA中没有模拟电路,无法直接实现电流采样,因此需要外加电流采样电路;选用AD公司的AD7478和AD7476采样芯片,利用SPI接口实现电流采样数据的读取。选用最高的20 MHz的SPI传输时钟,采样频率为1 MHz,另外已经确定了电流环的调节周期为10 kHz。因此可知,为了更有效和真实地将相电流读入调节器中,可以在一个电流环调节周期中进行不间断的100次采样,然后将其累加并求出均值,由此可以最大限度地减少因采样时间点选取的不同而导致的电流采样值的失真。

这一方案需要在较短的时间内(0.1 ms)完成较大的工作量(100次加法运算和1次除法运算),如果是传统伺服控制器构架(例如F2812),靠软件运算来完成,将会耗费大量CPU运算资源而导致其无法有效完成电流环调节工作。而基于SoPC的伺服控制器是利用FPGA的逻辑,由硬件直接实现这一功能,不占用CPU资源,可靠且高效地完成这一工作。

图4 DSP Builder下的SVPWM生成器

1.4 编码器信息处理

编码器信息处理包括两部分内容:一方面是位置信息的采集;另一方面是速度信息的采集。这里选用增量式编码器,输出A,B,Z三组差分方波信号,顺时针旋转时A超前B 90°,逆时针旋转时B超前A 90°,编码器每旋转1圈则在固定的位置产生1个方波信号Z。利用硬件描述语言Verilog编程,实现对A,B信号4倍频后的计数工作,并且根据A,B的相互超前关系得出转动方向,由此实现位置信息的采集。同样编写Verilog程序,实现M法和T法的速度采集工作,其中M法为计数法,在一个固定周期(1 ms)内对A,B四倍频后的信号进行计数,由计数结果和固定周期计算出速度值。T法为对A或B信号的周期执行计时工作,然后由单位脉冲的周期值计算出速度。这两种方法各有优劣:M法在电机转速较高的时候,采集速度的精度比较高,电机转速较低时,采集速度的精度比较低;而T法则正相反,在电机转速较高的时候,采集速度的精度比较低,电机转速较低的时候,采集速度的精度比较高[5]。

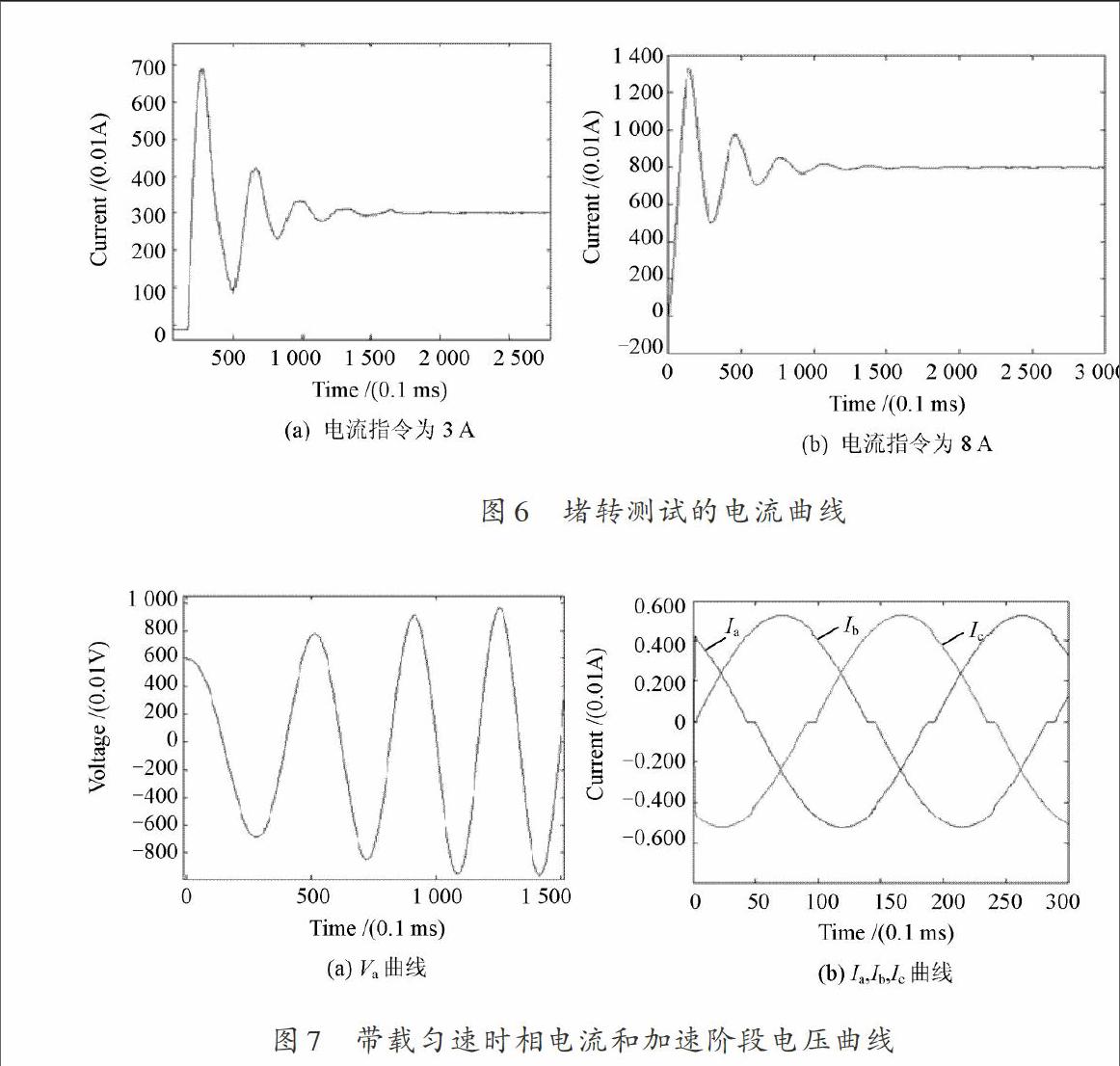

因此可将这两种方法结合起来,即为MT法。当速度比较高的时候采用M法获得的速度值;当速度比较低的时候则采用T法获得的速度值。确定切换点可以依据采样时钟、计数周期等信息计算获得。图5是在每转脉冲数为12 000 p/r,采样时钟20 ns,计数周期1 ms的情况下,计算出的M法和T法速度采样随转速变化时的精度曲线,其相交点在1 118 r/min处,将此处设为MT法的切换点。由此可知,采用MT法速度采样后,最大误差出现在切换点处且小于0.5%。

1.5 定制CPU软核

采用Altera的NIOS Ⅱ作为CPU,NIOS Ⅱ是一个用户可配置的32位RISC嵌入式处理器,它是SoPC的核心,处理器以软核形式实现,具有高度的灵活性和可配置性[6]。另外其支持使用专用指令,专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个NIOS Ⅱ处理器创建多达256个专用指令[7],这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和NIOS Ⅱ本身指令相同,能够从多达2个源寄存器取值,可选择将结果写回目标寄存器。同时,NIOS Ⅱ系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。因此,设计者可以根据系统需求的变化更改CPU,选择满足性能和成本的最佳方案,而不会影响已有的软件投入[8]。

图5 M法和T法速度采样精度曲线

定制的NIOS Ⅱ软核需要包含的组件是:SDRAM Controller,Timer,JTAG_UART,System ID,Parallel I/O等。另外需要在定制指令中添加浮点数值硬件乘法器和浮点数值硬件除法器,由此保证软件中的浮点运算可以在较少的指令周期内完成,提高运算器效率和降低CPU负担[9]。

2 验证过程

经过努力,已按照该方案制造出首台样机,其电流环带宽、电流精度、速度精度等指标都已达到要求。而且在此基础上FPGA的逻辑资源和引脚资源依然有较大的冗余空间,足够实现现场总线、绝对式编码器接口等更多功能。选择的测试电机为,凯奇公司的型号为140NYS?L的永磁同步电机,其主要参数为,额定转速3 000 r/p,额定功率4 kW,额定电流8 A等。主要进行两项测试,堵转测试和带载测试,测试结果如下所述。

2.1 堵转测试

这里列出了在电流指令为3 A和8 A两种情况下的堵转测试,直轴电流反馈Iq_fbk如图6所示。其中横轴为时间,单位是0.1 ms;纵轴为电流,单位是0.01 A,这里的超调幅度及震荡的时间,可以通过调节模块中的比例增益和积分增益两项参数来调整。由图可知,在堵转条件下电流可以较快的进入稳定状态,并且不存在稳态误差,且电流精度控制在5%以内,满足伺服控制器要求。

2.2 带载测试

图7(a)是电机加速过程中调节器输出的Va值绘制的曲线,图7(b)是带载匀速过程中采集的Ia,Ib,Ic三相电流的曲线。经过与传统伺服系统在相同测试条件下获得曲线进行比较,在平滑度、真实度等方面都有较大提高。

图6 堵转测试的电流曲线

图7 带载匀速时相电流和加速阶段电压曲线

3 结 语

由此得出结论,本文提出的基于SoPC的伺服控制器设计方案可行,且相对于传统的ASIC方案拥有更好的灵活性和适应性,在许多功能和性能方面都有所超越,例如电流采样精度,电流环调节效率等。另一方面,在研发过程中自主开发的SVPWM,PI调节器等核心功能模块,都以IP核的形式有效保存下来,因此更能有效保护自主知识产权,所以本方案具有较好的应用前景。

参考文献

[1] 赵希梅,郭庆鼎.交流伺服控制系统的发展现状及其研究热点[J].伺服控制,2010(1):15?16.

[2] Altera. DSP builder standard blockset user guide, section I [R]. US San Jose: 2011.

[3] 于吉帅.永磁直线伺服系统电流环优化设计[D].沈阳:沈阳工业大学,2013.

[4] 范心明.基于SIMULINK的SVPWM仿真[J].电气传统

自动化,2009(3):19?21.

[5] 舒志兵.交流伺服运动控制系统[M].北京:高等教育出版社,2006.

[6] 李兰英.NIOS Ⅱ嵌入式软核SoPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[7] Altera. Quartus Ⅱ handbook version 11.1 volume 4: SoPC builder [R]. US San JosE, 2011.

[8] 蔡伟纲.NIOS Ⅱ软件构架解析[M].西安:西安电子科技大学出版社,2007.

[9] 朱伟伟,彭建朝,代俊锋.一种双处理器间通信方案 的研究与设计[J].计算机技术与发展,2013(9):234?237.