高效率音频功率放大器设计

2015-10-20陈轩杨哲刘川

陈轩 杨哲 刘川

【摘 要】效率是功率放大器重要指标,在理想情况下,D类功放的效率为100%,B类功放的效率为78.5%,A类功放的效率才50%,在小型便携式音响设备如汽车功放、笔记本电脑音频系统和专业超大功率功放场合,仍感效率偏低不能令人满意。所以,效率极高的D类功放,因其符合绿色革命的潮流正受着各方面的重视。本文叙述了高效率音频功率放大器设计要求及方法。FPGA是实现高效率音频功率放大器功率测量的方法,设计方法新颖,具有实用性。

【关键词】高效率音频功率放大器 FPGA 设计

1设计要求

设计并制作一个高效率音频功率放大器及其参数的测量、显示装置。功率放大器的电源电压为+5V(电路其他部分的电源电压不限),负载为8Ω电阻。

1.1功率放大器

(1) 3dB通频带为300Hz~3400Hz,输出正弦信号无明显失真。(2)最大不失真输出功率≥1W。(3)输入阻抗>10kΩ,电压放大倍数1~20连续可调。(4)低频噪声电压(20kHz以下)≤10mv,在电压放大倍数为10,输入端对地交流短路时测量。(5)在输出功率500mW时测量的功率放大器效率(输出功率/放大器总功耗)≥50%。

(2)设计并制作一个放大倍数为1的信号变换电路,将功率放大器双端输出的信号转换为单端输出,经RC滤波供外接测试仪表用,高效率音频功率放大器框图如图1.1所示。 图1.1中,高效率功率放大器组成框图可参见本题第4项“说明”。

图1.1 高效率音频功率放大器框图

(3)设计并制作一个测量放大器输出功率的装置,要求具有3位数字显示,精度优于5%。

(4)说明:采用开关方式实现低频功率放大(即D类放大)是提高效率的主要途径之一, D类放大器即高效率功率放大器组成框图如图1.2。本设计中要求采用D类放大方式,不允许使用D类功率放大集成电路;效率计算中的放大器总功耗是指功率放大器部分的总电流乘以供电电压(+5V),不包括第2、3项涉及的电路部分功耗。制作时要注意便于效率测试;在整个测试过程中,要求输出波形无明显失真。

图1.2 高效率功率放大器组成框图

1.2 D类放大器的工作原理

一般的脉宽调制D类功率放大的原理框图如图1.3所示。D类功率放大的波形图如图1.4所示。

图1.3 D类功率放大的原理框图

图1.4 D类功率放大的波形图

1.3高效率音频功率放大器硬件电路

1.3.1脉宽调制器

(1)三角波发生器。三角波发生器采用宽频带、低漂移、满幅运放TLV2464及高速精密电压比较器LM311来实现,电路如图1.5所示。运放TLV2464的满幅放大既保证能产生线性良好的三角波,而且可以保证低电压供电下输出较大幅度。

载波频率的选定既考虑抽样定理,又考虑电路实现。选择载波频率为150kHz,使用四阶LC滤波器,输出端对载波频率衰减大于60dB。

三角波发生器频率为150kHz,C为750pF。100kΩ电位器用于调节三角波发生器频率。(2)前置放大器。前置放大器如图1.6所示。用于音频信号放大,使功放电压放大倍数1~20倍可调,也保证比较器的比较精度。

(3)比较器。比较器如图1.7所示。输入音频信号和三角波输出PWM波形。

图1.5 三角波发生器

1.6 前置放大器

1.7 比较器

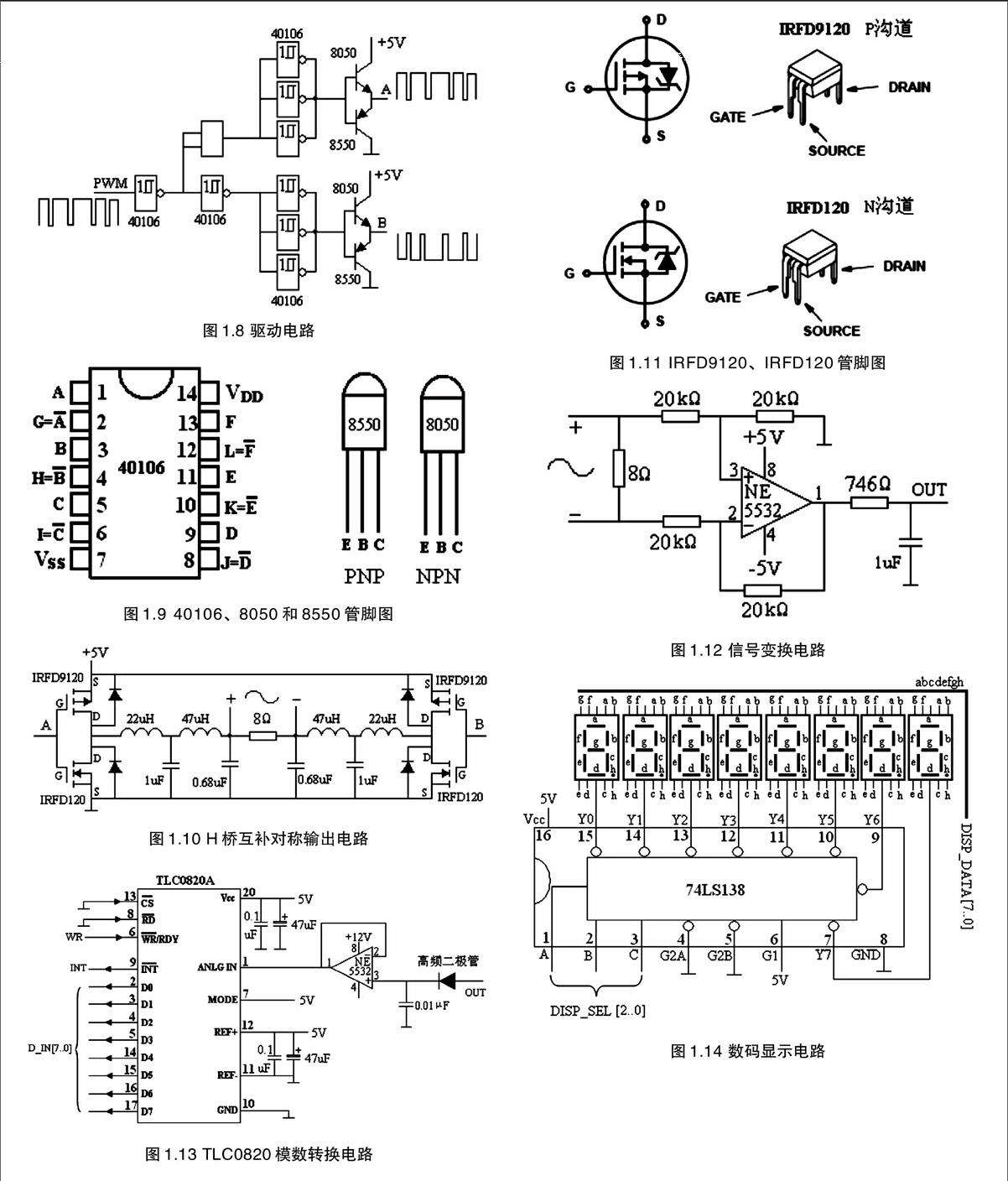

1.3.2驱动电路

驱动电路如图1.8所示。将PWM信号整形变换成互补对称的输出驱动信号。40106施密特触发器并联以获得较大的电流,送给由晶体三极管组成的互补对称射极跟随输出的电路。三极管选用8050和8550。40106供电电压VDD是3~15V,输入电压0~VDD。8050和8550是NPN、PNP对管,VCEO=25V,IC=1.5A。管脚图如图1.9所示。

图1.8 驱动电路

图1.9 40106、8050和8550管脚图

1.3.3 H桥互补对称输出电路

H桥互补对称输出电路如图1.10所示。IRFD9120、IRFD120是P沟道、N沟道MOS对管,VD=100V,ID=1.3A,导通电阻小、开关速度快、满足1W输出功率要求。管脚图如图1.11所示。两个四阶低通滤波器。

图1.10 H桥互补对称输出电路

图1.11 IRFD9120、IRFD120管脚图

1.3.4 信号变换电路

信号变换电路如图1.12所示。信号变换电路放大倍数为1,将功放的双端输出变为单端输出,经RC滤波供外接测试仪表用。

图1.12 信号变换电路

1.3.5 TLC0820模数转换电路

TLC0820模数转换电路如图1.13所示。图1.12信号变换电路的输出OUT接到图1.13经二极管检波电路TLC0820将模拟量变为数字量,TLC0820的数字量对应输出OUT的幅值。将TLC0820的数字量给高效率音频功率放大器的FPGA控制的总模块图1.15。数码显示电路如图1.14所示。图1.14用于显示高效率音频功率放大器的输出功率。

图1.13 TLC0820模数转换电路

图1.14 数码显示电路

1.4高效率音频功率放大器软件电路设计

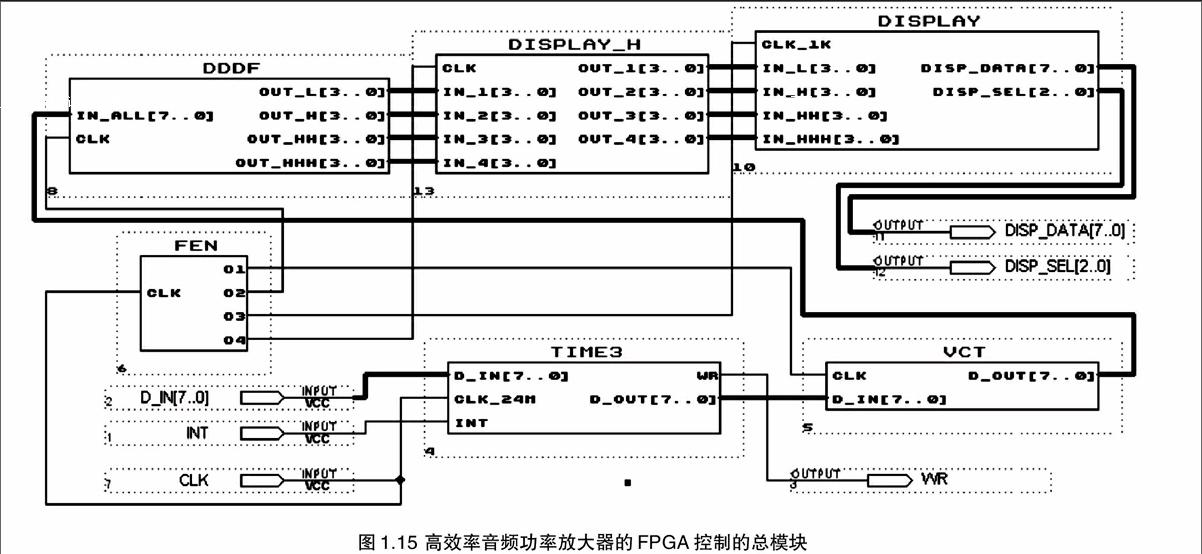

高效率音频功率放大器的FPGA控制的总模块如图1.15所示。输入CLK接24MHz时钟,D_IN[7..0]、INT接TLC0820。输出WR接TLC0820,DISP_DATA[7..0]、DISP_SEL[2..0]接数码显示电路。

图1.15 高效率音频功率放大器的FPGA控制的总模块

分频器FEN模块,将CLK24MHZ时钟分频为600Hz、40kHz、1kHz、60Hz经O1、O2、O3、O4输出。

TIME3模块,用于控制图1.13 TLC0820模数转换电路数据的写读。

VCT模块,测试输入信号的最大值。

DDDF模块,将VCT模块输出的二进制数转换四位二—十进制数结果输出。

DISPLAY_H模块,使数据传送速度变慢,数码管显示稳定。CLK是60Hz时钟,经分频变为CLK2=3Hz,用此时钟传送数据。

DISPLAY模块,用于数码管显示。

2结语

高效率音频功率放大器硬件电路设计和软件电路设计可以实现高效率音频功率放大器的设计要求。

基金项目:2015大创项目资助。指导教师,王振红。