EnDat2.2通讯协议接口的设计

2015-09-12廖彩霞

廖彩霞,赖 欢,董 佳

(重庆望江工业有限公司,重庆 400071)

具有精度高、体积小、抗干扰性好、数字化接口、传输可靠性高以及绝对定位等优点的绝对式编码器目前被广泛应用于工业和军事等诸多领域。它通过循环二进制码(格雷码)、自然二进制码或者PRC码对码盘上的物理刻线进行光电转换,然后将连接轴转动的角度量转换为对应的电脉冲序列,并以数字量的形式输出。其数据输出有并行和串行两种接口,其中串行方式又分为同步串行接口(SSI)和异步串行接口。SSI接口和在SSI基础上发展起来的EnDat和BISS接口等在光电编码器上得到了广泛的应用。EnDat接口是德国海德汉(HEIDENHAIN)公司设计的数字式、全双工同步串行的数据传输协议,具有连线简单、精度高、传输速率高和抗干扰能力强等优点,是编码器和光栅尺等数据传输的通用接口。

1 EnDat2.2 接口协议

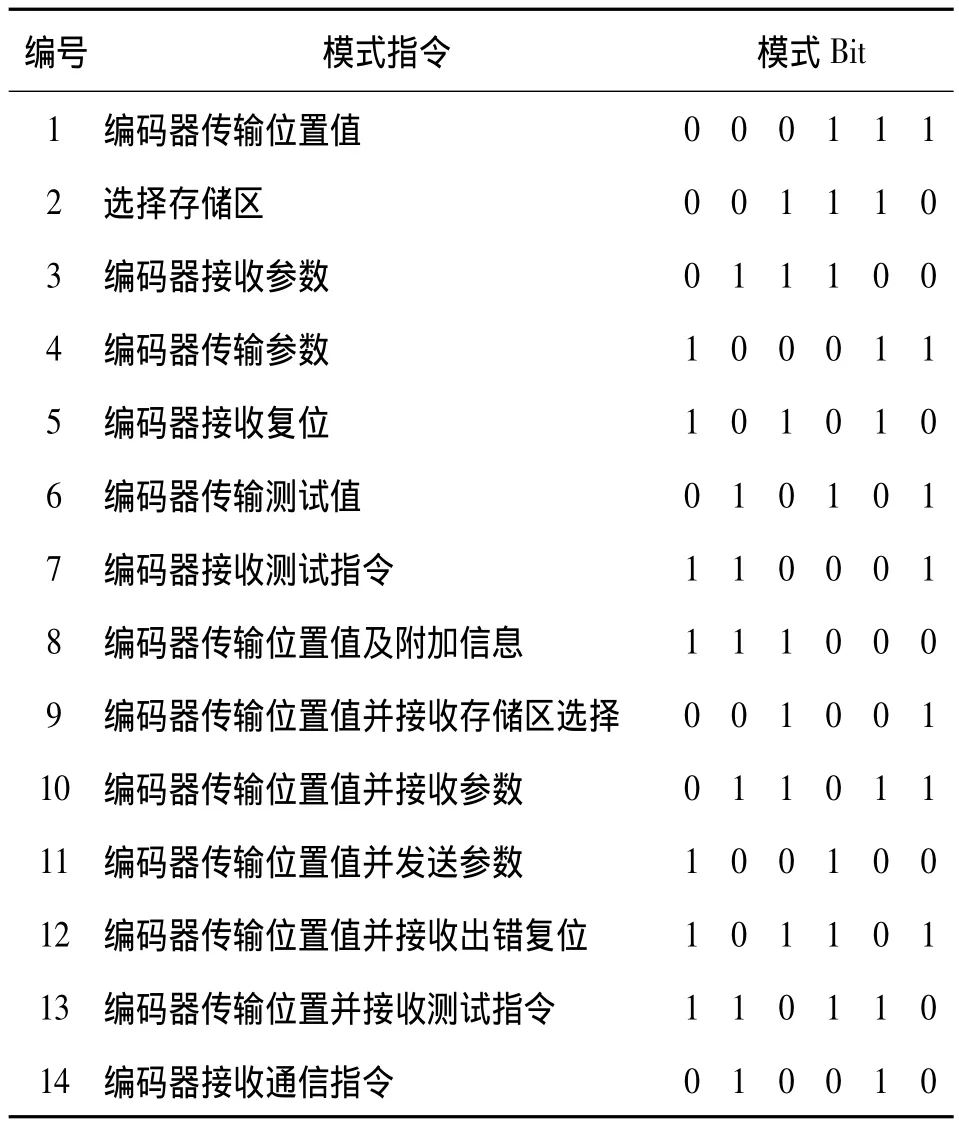

EnDat2.2数字接口传输的数据类型分为位置值和附加信息或参数,所传输的信息类型由模式指令选择,模式指令决定被发送信息的内容,每个模式指令包括3位,每位均采用冗余或反向发送,从而保证数据传输的准确性。当编码器检测到一个错误的模式传输,它即发送一个错误的信息。EnDat2.2接口协议共有14种模式指令,模式指令及含义如图1所示。

本文以编码器传输位置值为例,编码器传输位置值的模式指令为“000111”,如表1所示。数据包发送与数据传输同步,传输周期从时钟的第1个下降沿开始,编码器保存测量值并计算位置值,2个时钟周期后,后续通讯转换接口发送模式指令。当编码器切换成传输状态后(即10个时钟周期后),后续通讯转换接口开始监测数据端的上升沿,第1个上升沿为数据传输起始位S。编码器发送位置值后,从起始位开始向后续通讯转换接口传输数据。后续错误位(F1和F2)是检测类信号,用于监测故障。编码器从最低有效位(LSB)开始发送绝对位置值,位置值的数据发送以循环冗余校验(CRC)结束,在数据结尾处,必须将时钟信号置为高电平,10 ~30 μs或者1.25 ~3.75 μs后(系统时钟大于 1MHz 时)数据线返回低电平。然后,时钟信号启动另一次数据发送。

图1 模式指令及含义

表1 传输位置值的时序

2 接口硬件设计

该接口由CPLD和RS485差分信号接收器、发送器和外部晶振组成。CPLD采用Altera公司的MAXⅡ系列,用于实现EnDat2.2协议解释和DSP之间的并行通信接口等功能,完成译码及位置数据采集的任务。DSP采用TMS320X2812,数据总线宽度为16位,DSP的数据线D0~D15连接CPLD的IO0~IO15,DSP地址线 A0~A3连接 CPLD的 IO16~IO19,DSP外部片选/XZCS0AND1连接CPLD的IO26。由于编码器数据传输信号为差分信号,因此CPLD和编码器之间通过两块差分驱动芯片MAX485_1和MAX485_2来连接。其中,MAX485_1用于发送模式指令和接收编码器数据,为双向传输。MAX485_2用于发送同步时钟信号到编码器,为单向传输。同时,该接口还具有数据纠错处理功能,完全能代替厂家的专用接收芯片,降低产品成本。接口硬件设计如图2所示。

图2 通讯接口硬件电路

3 接口软件设计

3.1 位置采样原理

为了达到数据同步采样的目的,CPLD与编码器采用同一时钟信号,在编码器允许的时钟频率范围内,CPLD向编码器发送采样时钟信号,编码器以此信号为工作时钟信号,并依据数据传输协议在固定的时序上向CPLD传输位置数据。同样,CPLD在固定的时序上接收编码器发送的位置数据,从而完成一次数据采集。

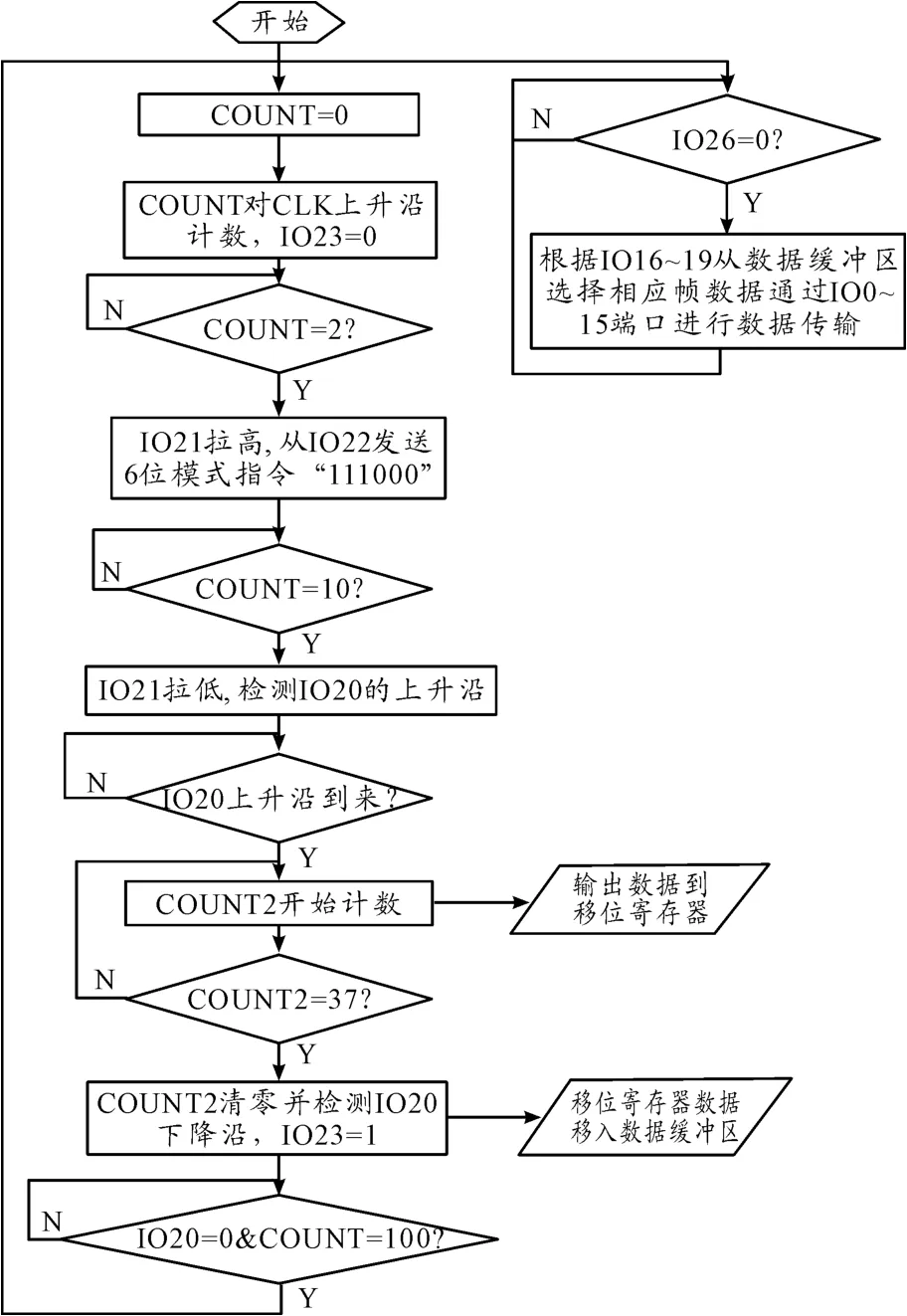

3.2 程序流程图

该接口的程序流程如图3所示。

3.3 模块组成

程序由时钟发生模块、计数模块、与编码器间的发送/接收模块、与DSP间的发送/接收模块、数据缓冲模块和发送/接收使能模块6个部分组成。时钟发生模块产生周期为1 μs(1 MHz)的方波信号CLK,计数模块对CLK时钟信号计数,以判断数据传输进程。

CLK与计数模块的计数结果产生同步时钟信号,表1所示“给编码器的时钟频率”,此信号作为与编码器间通讯同步时钟,与编码器间的发送/接收模块完成与编码器间的数据交互,与DSP间的发送/接收模块完成与DSP的数据通讯,按照DSP读取命令将存储在数据缓冲区中的位置数据通过计数模块控制MAX485_1和MAX485_2的发送/接收使能,确保与编码器间的正确数据传输。

图3 主程序流程

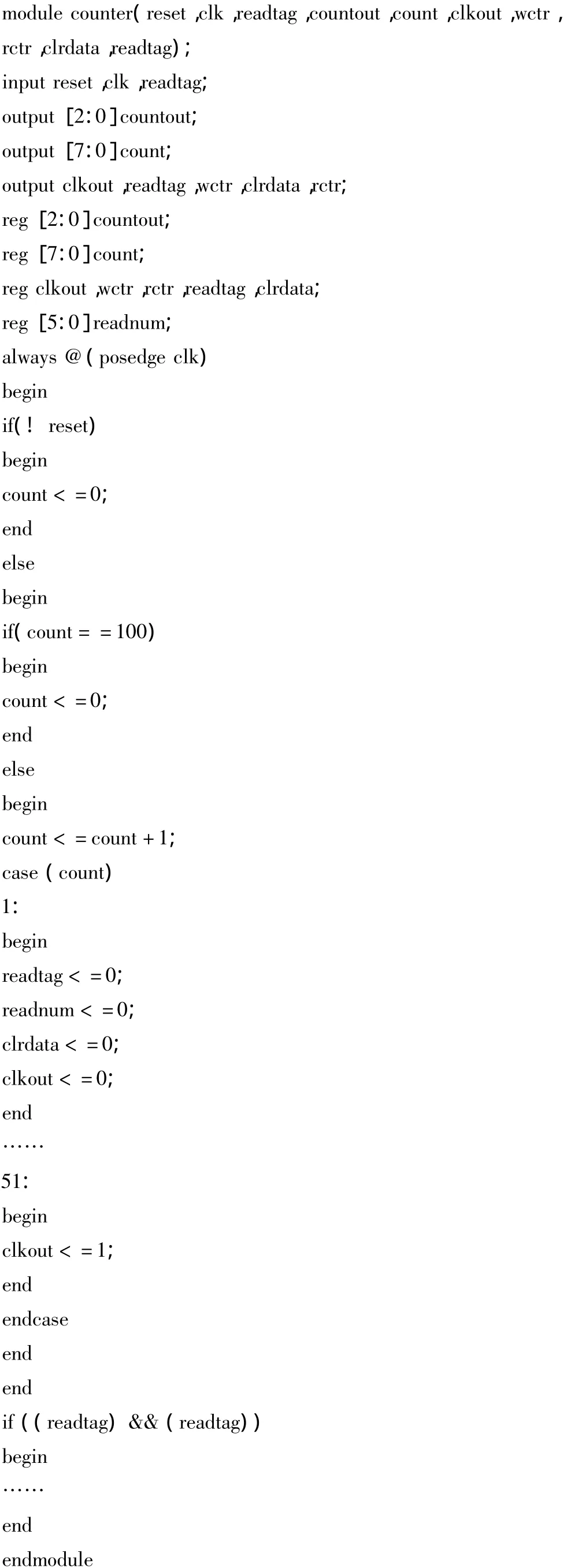

3.3.1 计数模块

按照表1中EnDat2.2数据协议格式,分析时钟信号和数据信号的特点,产生适合所选编码器的时钟信号和接收数据所需的信号,同步脉冲发生部分以硅振荡器产生的稳固时钟源为时钟信号基准。CPLD对发送给编码器的时钟进行计数,在clk的每个时钟上升沿计数模块的计数变量count加l,变量count的初始值为0。由于编码器是在时钟下降沿读取数据,为了让编码器读取到稳定状态的数据,通讯接口需要提前半个周期(时钟上升沿)将数据发送到与编码器的数据端口。因此,当计数模块检测到count的值为2时,与编码器间的发送/接收使能模块使IO21信号电平拉高,使MAX485_1处于数据发送模式,此时,发送模块开始从数据发送端口IO22发送6位模式指令“000111”。当检测到count的值为8时,6位模式指令已发送完毕。当检测到count的值为10时,将与编码器间的发送/接收使能模块使IO21信号电平拉低,使MAX485_1处于数据接收模式。此时,开始检测数据接收端口IO20的上升沿。当第一个上升沿到来时,启动接收数据计数器count并加1,并将接收到的数据逐位移送到数据缓冲模块的移位寄存器。当count计数到37时(1位S,1位F1,1位F2,29位D,5位CRC),将移位寄存器中的数据一次性移入数据缓冲区,并将计数器count清零,同时时钟发生模块将与编码器的同步时钟信号设置为高电平。此时开始检测数据接收端口IO20的下降沿,当检测到下降沿到来时,便可启动新的数据传输。计数模块程序代码如下:

3.3.2 数据缓冲模块

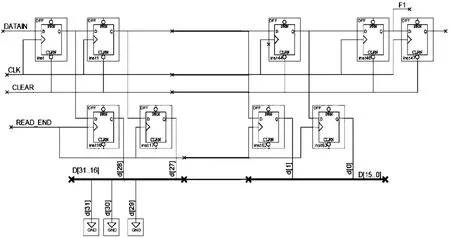

如图5所示,数据缓冲模块建立一个数据双向读写通道,由移位寄存器和数据缓冲区两部分组成,编码器接收到的串行数据存放到移位寄存器中,完成后同时移入数据缓冲区,供DSP读取。该模块将编码器采集到的数据进行移位处理,输入信号DATAIN是编码器回传的串行数据信号,CLK、READ_END和CLEAR表示同步脉冲发生块产生的移位、锁存和清零信号。D[31..16]、D[15..0]为移位处理后发送到DSP的数据,F1是错误位,S为起始位,DSP收到F1错误标志即放弃读取当前位置值。

图4 数据缓冲模块

3.3.3 程序仿真

将各个模块连接在一起后组成顶层模块,对其进行仿真,仿真波形如图5所示。其中Clk_in为模拟振荡器产生的输入波形,Clk_G为发送给编码器的同步脉冲时钟信号,DI_G为发给编码器的模式指令,从仿真的输出信号G_BUFFER[31..0]波形图看,符合Endat接口信号标准,该接口设计达到了预期效果。

图5 顶层模块功能仿真波形

3.3.4 测试结果

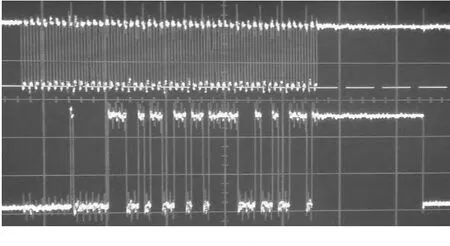

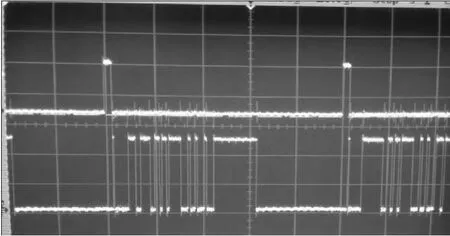

对编码器进行上电测试。CPLD发送模式指令“000111”和同步脉冲到编码器,示波器测出的实际波形如图6~8所示,编码器出来的位置数据正确,接口工作正常,满足设计要求。

图6 时钟和模式指令之间的时序波形

图7 时钟与数据之间的时序关系

图8 模式指令与数据之间的时序关系

4 结束语

本文设计了一种基于CPLD的EnDat2.2通讯协议接口,实现了串并转换及译码逻辑等功能。该接口还具有数据纠错处理功能,经过仿真和测试,该通讯接口取得了预期效果,完全满足DSP和编码器之间的数据通讯要求,基本能替代厂家的专用接收芯片,降低了产品的经济成本,该接口设计已经广泛应用于各种高精度转台伺服系统。

[1]林灶生.Verilog FPGA芯片设计[M].北京:北京航空航天大学出版社,2006.

[2]周志炜.基于FPGA的多路光电编码器数据采集系统[D].哈尔滨:哈尔滨工业大学,2006.

[3]黄正瑾.CPLD系统设计技术入门与应用[M].北京:电子工业出版社,2002.

[4]赵曙光,预万有,杨颂华.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2000.

[5]贺敬凯.Verilog HDL数字设计实训教程[M].西安:西安电子科技大学出版社,2012.

[6]夏宇闻.Verilog数字系统设计教程[M].3版.北京:北京航空航天大学出版社,2013.

[7]程云长.可编程逻辑器件与VHDL语言[M].北京:科学出版社,2005.

[8]EDA先锋工作室,王诚,蔡海宁.Altera FPGA/CPLD设计:基础篇[M].北京:人民邮电出版社,2011.

[9]郑亚民,董晓舟.可编程逻辑器件开发软件Quartus2[M].北京:国防工业出版社,2006.

[10]马彧.CPLD/FPGA可编程逻辑器件实用教程[M].北京:机械工业出版社,2006.