SRAM 中器件参数的设计方法

2015-09-05李红征赵文彬

徐 政,李红征,赵文彬

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引 言

专用集成电路在特定领域长期使用的要求与半导体制造技术快速更新换代之间产生了冲突:在产品仍有使用需求的时候,制造厂已经淘汰了过时工艺,不再提供该产品的生产服务,产品供应商需要寻找能够提供生产服务的其他制造厂。

参数匹配是产品转线的难点。产品供应商能够从原制造厂得到流片的PCM参数,但是PCM参数只包含了基线工艺信息,对于某些产品而言并不充分,例如集成了SRAM的电路。

SRAM通常是电路设计者根据制造厂提供的compiler自动生成,设计者关注的只是SRAM的功耗、速度等性能,对器件参数并不关注,在SPICE模型中也找不到SRAM的器件参数,因此无法提供SRAM的器件参数值;不同制造厂的SRAM 可能由不同IP供应商提供,bitcell尺寸有差别,为了节省面积,bitcell大量使用设计规则中的最小尺寸,而小尺寸器件的参数对工艺波动敏感,因此每个制造厂都使用特殊的工艺条件和工艺控制来满足器件参数要求。为此,产品转线时必须对SRAM中的器件提出明确的参数要求,否则无法确定工艺流程。

为了解决这个问题,本文从分析SRAM的工作过程着手,研究了器件参数对SRAM稳定性和功耗的影响,对于给定尺寸的SRAM,计算出最佳参数目标值。

2 SRAM工作原理

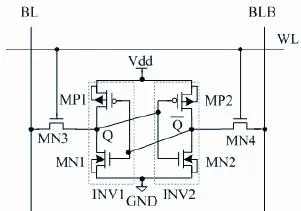

图1 单端口六管SRAM

2.1 数据写入 [2]

向存储单元写入“1”的过程是:(1)当WL字线为低电平,置BL位线为“1”电平,BLB为“0”电平;(2)置WL字线为高电平,此时传输管MN3、MN4导通;(3)存储单元的存储节点NQ通过MN4向BLB放电,达到“0”电平,MN1截止,MP1导通;(4)BL位线通过MN3,VDD通过MP1,对存储节点Q充电至“1”电平,MN2导通,MP2截止;(5)置WL字线为低电平,MN3、MN4关闭,此时存储单元的结点Q处于“1”电平状态,NQ处于“0”电平状态。这样就完成了向存储单元写入“1”的全过程。

2.2 数据读出

从存储单元读出“1”的过程是:(1)预充BL和BLB位线到“1”电平,此时WL字线处于低电平;(2)使WL字线为高电平,传输管MN3和MN4导通;(3)BLB通过MN4和MN2(单元存“1”时,MN2一直处于导通状态)迅速放电至“0”电平,MN1仍然截止;(4)VDD通过MP1和MN3对BL充电,使BL保持在“1”电平,MN2仍然导通;(5)去掉字线WL上的高电平。

由于单元管的尺寸很小,位线通过单元管放电的速度很慢,为了提高读出速度,只要在位线上建立起一定的电压差(70 mV~100 mV)就可以了,而不必等到一边位线下降到低电平[3]。通过列译码器控制的列开关,把选中的单元位线读出的微小信号差送到公共数据线,再通过公共数据线送到灵敏放大器,把微小的信号差放大为合格的高低电平,最后通过缓冲器转换成单端信号输出。

2.3 稳定性分析

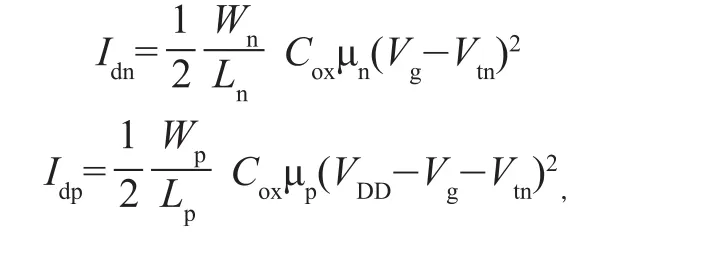

2.3.1 翻转电压

在反相器的翻转电压点,有Idn=Idp,在饱和区,

得出翻转电压

(W/L)pd/(W/L)pg越大,驱动管比传输管驱动能力越强,则驱动管的等效电阻越小,假设Vtrip不变,读稳定裕度增加,存储单元中的内容在读过程中不易被破坏。

(W/L)pu/(W/L)pg越小,负载管比传输管驱动能力越弱,则负载管的等效电阻越大,写稳定裕度增加,外部数据越容易写入到存储单元。

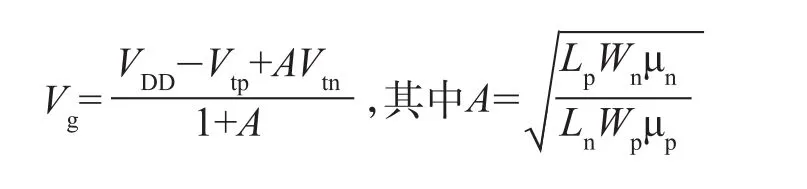

2.3.2 静态噪声容限SNM[4]和功耗

由于阈值电压和电源电压的持续降低,SRAM存储器的静态噪声容限SNM(static noise margin)和写入余量WM(write margin)大为减小,这主要是由于晶体管参数分散性的加大以及电源电压的降低。尤其因随机掺杂扰动引起的SRAM窄沟晶体管阈值电压的波动对SRAM工作的稳定性有极大的影响。由于对面积的严格要求,SRAM使用比逻辑器件更严格的设计规则,当电源电压VDD、阈值电压VT、温度和STI应力等扰动变大时,SRAM单元就会很容易失去它的状态。

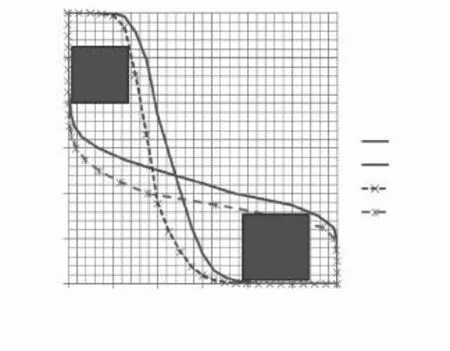

图2 SRAM单元的静态稳定性和功耗示意图

图2为图1的SRAM单元稳定性和功耗示意图。图中INV1表示Vout对于激励Vin的响应,INV2表示Vin对于激励Vout的响应,SNM由在曲线INV1和INV2之间能画出的最大正方形表示。大的正方形表示大的SNM。只有在存储的“0”电平为0、“1”电平为VDD的条件下才有最小功耗,在翻转电压处有最大功耗。

2.3.3 读失效分析

(1)读扰动。读操作时,位线的“1”电平对存储“0”的节点充电,“0”电位抬高导致反相器翻转造成失效。要想提高读稳定性,就要保证在字线关闭之前,Q节点最高电压小于反相器翻转电压,这两个电压差叫做读裕度(read margin);

(3)工艺引起的局部随机参数变化。反相器PLPN的强度影响它的翻转电压。驱动管阈值升高,负载管阈值降低,翻转电压就有可能低于读扰动电压导致读失效。不同晶体管驱动强度失配造成读失效,这种失效是由局部随机参数变化引起,并非全局参数变化引起。

(4)减小读失效对器件的要求。驱动管PD要通过增加W/L提高驱动能力,增加阈值提高翻转电压;负载管PU要抬高阈值;门管PG要降低阈值和W/L。核心是增加驱动管PD驱动能力和阈值。

2.3.4 写失效分析

(1)写扰动。假设新数据写入之前Q节点电压为“1”,要对Q节点写入“0”,写入周期BL对Q节点放电,使得它的电压逐渐下降,如果在字线关闭之前,Q的电压高于反相器的翻转电压,则新数据写入失败。由此可知,要想提高写稳定性,就要保证在字线关闭之前,节点放电后的电压远小于反相器翻转电压。这个电压差叫做写裕度(write margin)。

(2)传输管PG驱动能力不足。负载管比传输管驱动能力越弱,写稳定裕度增加,外部数据越容易写入到存储单元。

(3)工艺引起的局部随机参数变化。工艺参数变化造成晶体管驱动强度变化,有可能增加写时间。例如,负载管阈值减小,传输管阈值增加,写时间增加,写数据失效。而且,增大传输管尺寸,缩小负载管尺寸,会增加读失效概率。所以必须在读失效和写失效概率之间做优化。同样,造成晶体管之间的失配是由于die内随机参数变化引起。

(4)减小写失效对器件的要求。在满足速度要求的条件下,降低负载管比传输管的驱动能力。

3 SRAM中的器件参数设计

以0.13 μm工艺节点使用的单端口SRAM(SP)和双端口SRAM(DP)的bitcell为例,从foundry的器件拟合曲线中找出PU、PD、PG的驱动电流和泄露电流,计算bitcell的翻转电压、读扰动、写扰动、功耗,比较SRAM 在 5个工艺角(TT、FF、SS、SF、FS)的特性。

3.1 两种 bitcell稳定性比较

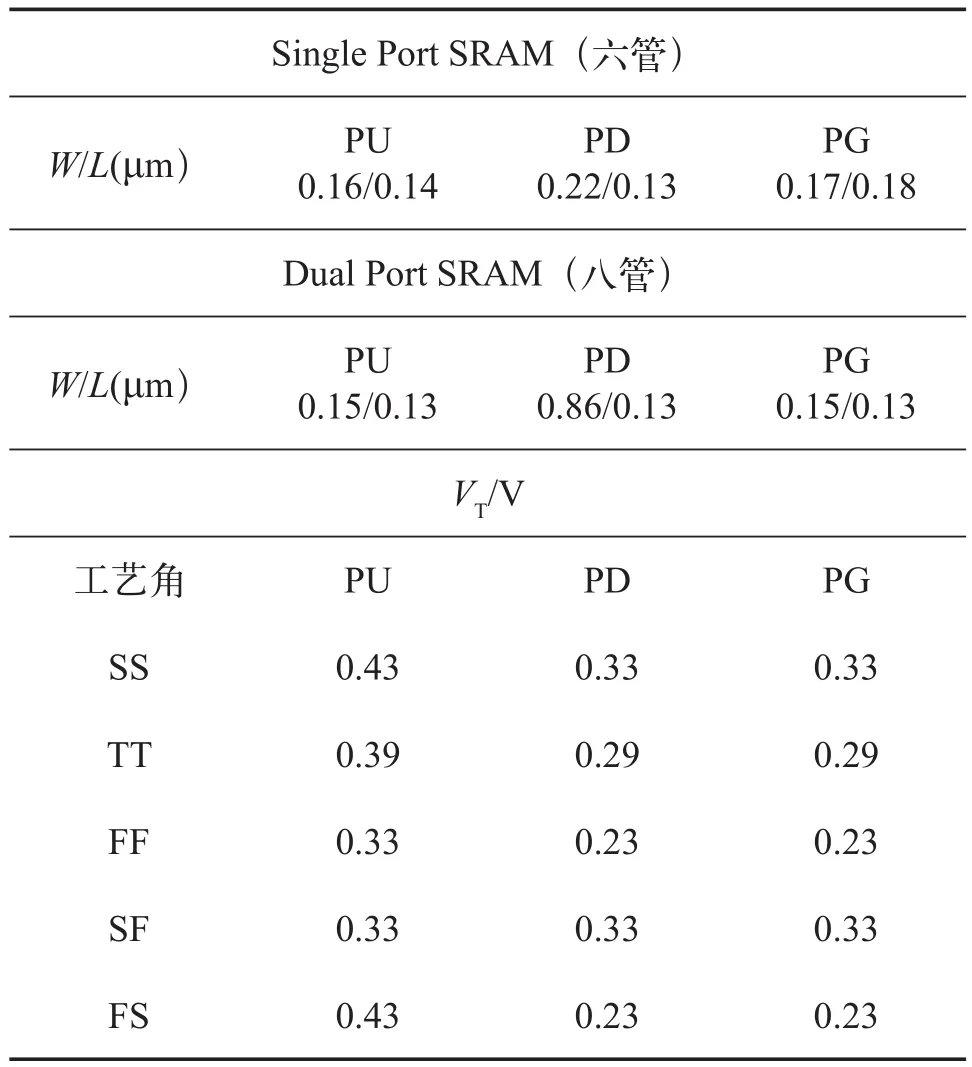

表1给出了foundry提供的0.13 μm工艺两种bitcell的尺寸和参数工艺角。

表1 两种bitcell的结构尺寸和工艺角参数

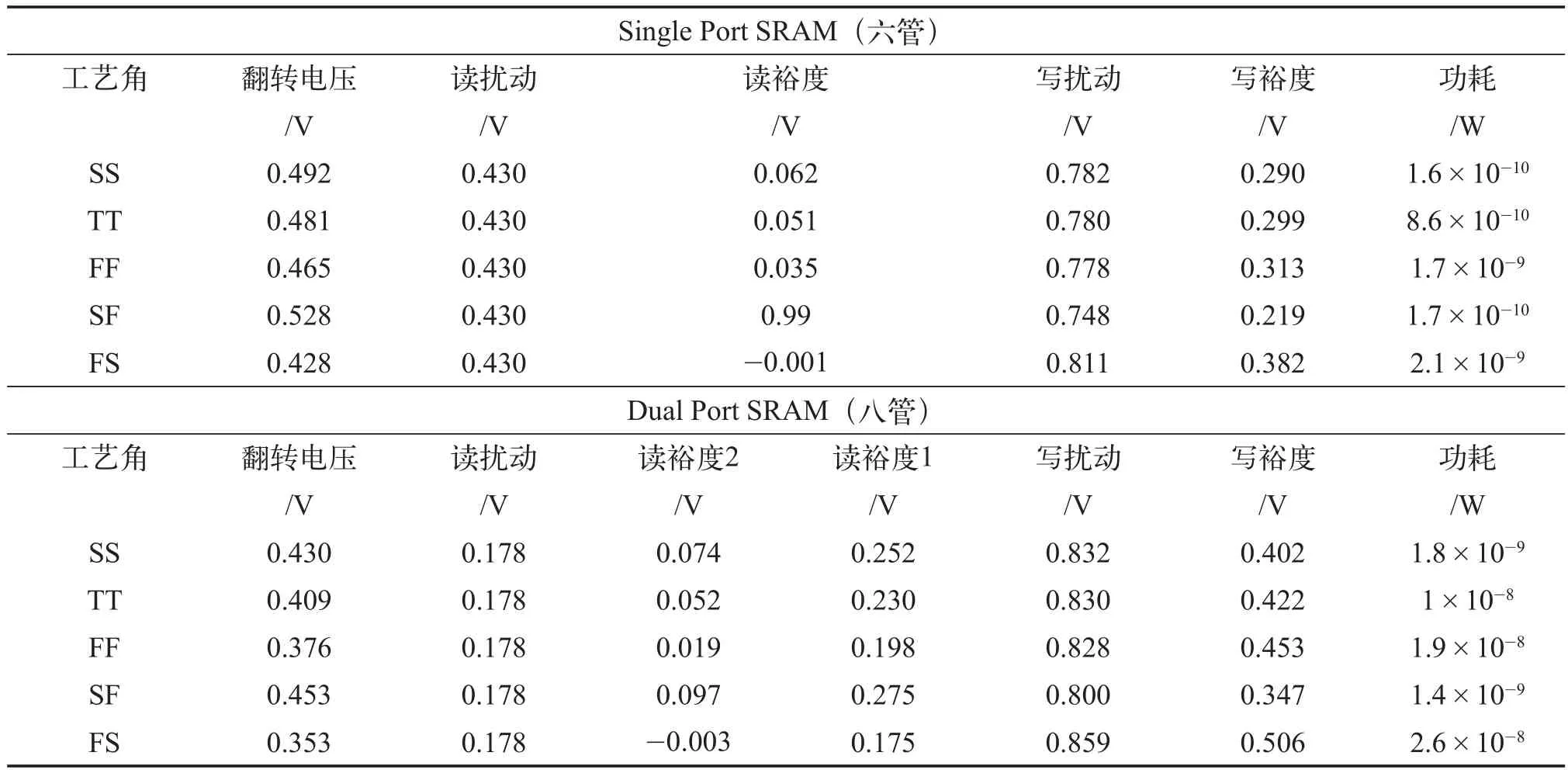

表2 两种bitcell的稳定性和功耗

表2说明:

读扰动:读操作引起的单元存储电平变化;

写扰动:写操作引起的单元存储电平变化;

读裕度1:1个端口读取数据的读裕度;

读裕度2:2个端口同时读取数据的读裕度。

表2给出了根据foundry的器件参数计算出的bitcell特性。

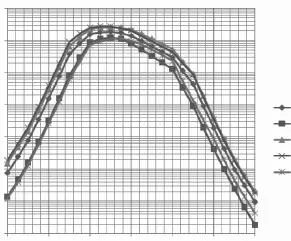

图3 SP与DP的静态稳定性比较

图3给出了根据foundry的器件参数计算出的SP与DP的静态稳定性比较。

3.2 功耗比较

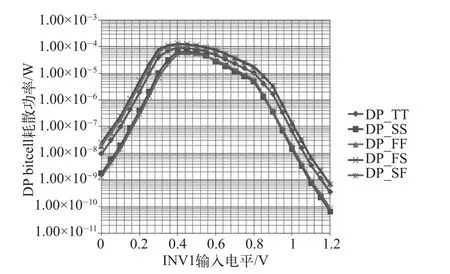

图4、图5给出了根据5个工艺角的器件参数计算出的SP SRAM和DP SRAM 的bitcell功耗。

图4 SP bitcell 5个工艺角的功耗

图5 DP bitcell 5个工艺角的功耗

3.3 结论

(1)翻转电压由PU、PD的阈值和宽长比决定,驱动管/负载管的驱动能力越强,翻转电压越低;读扰动由PD、PG的阈值和宽长比决定,驱动管/传输管的驱动能力越强,读扰动越小,读裕度越大;写扰动由PU、PG的阈值和宽长比决定,传输管/负载管的驱动能力越强,写扰动越大,写裕度越大。

(2)对于给定尺寸的bitcell,确定器件参数的次序为:根据功耗要求确定驱动管阈值→根据翻转电压确定负载管阈值→根据读写裕度确定传输管阈值。

(3)SRAM的漏电主要由负载管和传输管(两个都是NMOS)产生,这是由于窄沟效应使N管阈值降低,亚阈值漏电增加。降低SRAM漏电的方法是对N管增加一次沟道注入,通过抬高阈值来降低亚阈值漏电。

(4)0.13 μm工艺节点SP SRAM和DP SRAM中的最优工艺条件是SF工艺角,对应的器件参数为:PU、PD、PG的阈值都为0.33 V。

[1]肖宏. 半导体技术导论(第二版)[M]. 北京:电子工业出版社,2013. 7.

[2]闫石主编. 数字电子技术基础(第四版)[M]. 北京:高等教育出版社,1998. 377-379.

[3]周润德译. 纳米CMOS集成电路——从基本原理到专用芯片实现[M]. 北京:电子工业出版社,2011. 149.

[4]周润德译. 纳米CMOS集成电路——从基本原理到专用芯片实现[M]. 北京:电子工业出版社,2011. 151-152.