基于FPGA与LabVIEW的DDS任意信号发生器设计*

2015-08-18梁赫西谢虎城湖北师范学院教育信息与技术学院湖北黄石4500武汉大学电子信息学院湖北武汉40074武汉华中数控有限公司湖北武汉40000

梁赫西,周 密,谢虎城(.湖北师范学院 教育信息与技术学院,湖北 黄石 4500;.武汉大学 电子信息学院,湖北 武汉 40074;.武汉华中数控有限公司,湖北 武汉 40000)

基于FPGA与LabVIEW的DDS任意信号发生器设计*

梁赫西1,周密2,谢虎城3

(1.湖北师范学院 教育信息与技术学院,湖北黄石 435002;2.武汉大学电子信息学院,湖北武汉430074;3.武汉华中数控有限公司,湖北武汉430000)

实现了一种基于FPGA与LabVIEW平台的任意波形发生器。通过FPGA搭建硬件平台,与LabVIEW上位机软件实现串口通信,实时调整FPGA内部波形数据,可实现正弦波、方波、锯齿波、三角波、高斯白噪声、叠加正弦波、自定义公式等常规波形,同时也可以手动绘制任意波形,充分发挥了软件的灵活性。通过参数的设定,可方便地设计各种复杂波形。本设计在 EP4CE15F17C8芯片上实现,与LabVIEW上位机软件协同工作,经测试系统具有良好的稳定性、灵活性。

DDS;FPGA;LabVIEW

0 引言

直接数字频率合成[1](Direct Digital Frequency Synthesis)是一种先进的波形合成技术,目前市面上有不少的 DDS专用芯片,但由于大部分设计固化在芯片中,在某些场合此类专用芯片具有一定的局限性[2-3]。为了提高DDS设计的灵活性,本文设计了一种基于FPGA与LabVIEW平台的DDS任意信号发生器。由于FPGA的可编程特性以及软件平台的人机交互,使得设计的灵活性得到了大幅度提高。

同时由于FPGA具有丰富的寄存器、LUT资源,因此设计所需的数字逻辑可在FPGA内部实现,从而使得设计尽量集成到单芯片上,减小了路径的延时,提高了系统的工作频率,增大了信号发生器的分辨率[4-5]。

1 DDS设计原理

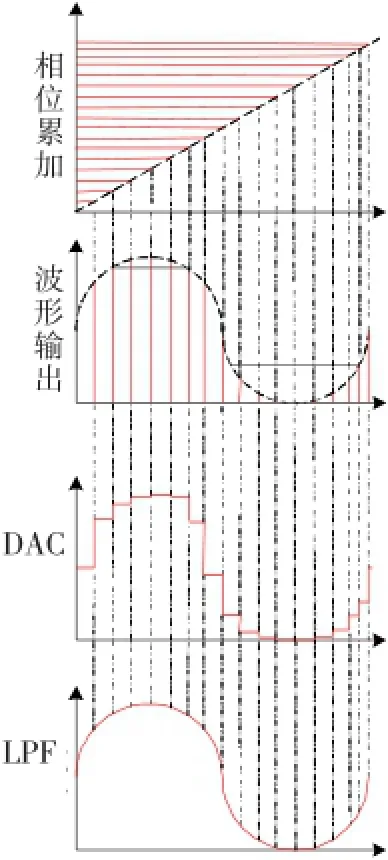

本文DDS设计方案如图1所示。信号发生器采用相位累加的方法,通过频率控制字K的累加实现相位A的控制,由于波形相位与幅值的一一对应关系,通过查表的方式可以准确输出对应波形幅值,从而产生初步的波形信号。由于数字波形信号为一脉冲序列,需通过DA进行模数转换以及LPF的平滑,方可得到理想的输出波形信号。其波形变化流程如图2所示。

图1 DDS设计原理图

图2 波形变化流程图

由波形输出特点可知,输出波形的频率fo与相位累加器的累加地址输出数M(M=2N)、频率累加字K以及输入频率fc存在特定关系。通过分析可知,M与 fo成反比,K与fo成正比,fc与fo成正比。故可以推知输出波形的频率fo的计算公式如下:

由式(1)可知,fo的输出范围若需扩大,需增大 fc、增大 K或者减小N,而一般fc为定值,且N需要足够大来保证最小分辨率,因此在这里需要做一个平衡,本设计选择N为32,时钟频率fc为100 MHz,因此本设计的最小频率分辨率为 0.023 2 MHz。但在实际设计中,这里N采用32 bit位宽,会给设计的存储空间带来非常大的考验,需要存储的数据量多达 4 GB,因此为了在保证最小分辨率的同时,减小系统的数据存储量,本文采取的方式是仅取用 32 bit位宽的高10位进行寻址,这样使得内部存储资源能够得到大幅度的缩减,但与此同时造成的相位截断带来了频谱上的杂散分量。为了消除相位截断带来的频谱杂散分量的影响,本设计在相位累加器后加入了一个伪随机序列生成器,采用伪随机序列生成器来打破相位截断的周期性,这样便可以最大程度地提高输出波形的质量。

2 任意信号发生器整体架构

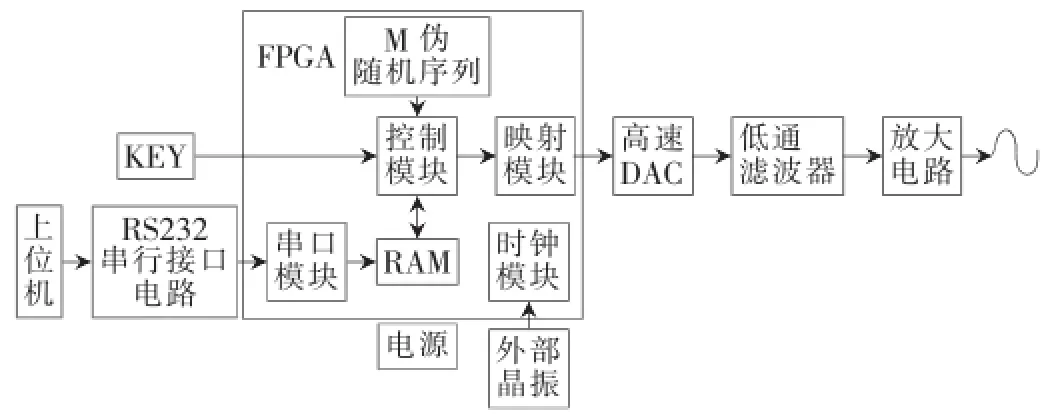

DDS硬件构架如图 3所示。硬件部分由 FPGA及其外围电路组成,主要实现单一波形的输出,同时提供与上位机的通信接口;其处理核心采用ALTERACYCLONE IV系列 FPGA作为硬件平台[6-7],主要实现功能为:接收上位机串口波形数据并实时将数据更新到双口RAM。DDS控制模块实时采集按键值,以调节频率控制字K,频率控制字K通过DDS控制模块进行累加,并在双口RAM中寻址得到波形幅值,并将该波形幅度值输出到波形幅度映射模块,此模块可选择对波形信号进行进一步的放大、缩小等操作。输出到外部的波形数据流经高速DA数模转换,将数字信号转换为模拟信号,此模拟信号为一阶梯信号,需通过低通滤波器对信号进行平滑,最后通过放大模块,对信号幅度进行还原即可得到理想的输出波形信号。

图3 任意信号发生器整体架构

2.1FPGA逻辑设计

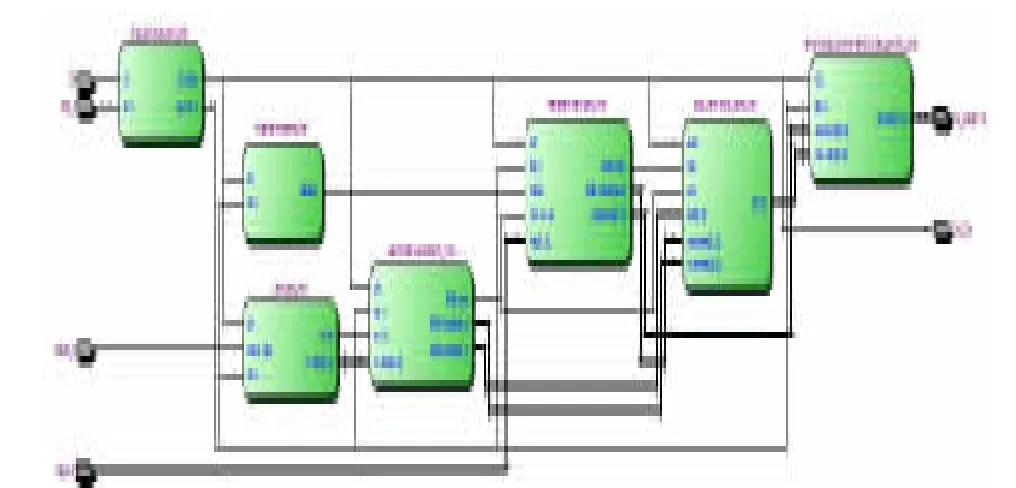

FPGA硬件设计部分主要包括系统复位模块、串口接收模块、RAM接口模块、按键控制模块、M伪随机序列发生模块、RAM存储模块、幅度控制模块。其整体FPGA设计RTL级视图如图4所示。

图4 FPGA整体设计RTL级视图

系统复位模块采用异步复位同步释放的方法,将外部异步时钟同步到系统中,用于PLL锁相环的复位操作,同时将外部复位信号与PLL输出稳定锁定信号进行与运算,输出结果再次进行异步复位同步释放操作,使得输出信号可以稳定地对系统全局进行复位,从而很好地保证了系统的稳定性。

串口接收模块主要由波特率发生器模块和串口接收器模块两部分组成。本设计波特率预置为9 600 Baud,系统时钟为 100 MHz。串口接收模块负责接收上位机的串口数据流,并将串行数据流转换为并行数据。

RAM接口模块主要完成将串口接收模块接收的1 024 B数据写入到双口 RAM中。写入完毕后,将写信号置0释放,便于后续读操作。写入地址与读写地址均采用内部累加器自动累加寻址。同时设定写操作优先级高于读操作。

按键检测模块主要完成外部按键信号的检测,从而改变输出波形的频率、相位以及幅度。为了增大频率分辨率,减小数据存储容量,将32位的相位累加器截取其高10位进行寻址,给输出波形带来了杂散分量,即相位截断误差。而相位截断误差主要是由于输出波形为一周期性的阶梯波,因此可通过一个M伪随机序列来打破这种周期性,抑制相位截断所带来的误差。本设计将抖动注入在相位累加器之后。

M伪随机序列发生模块的生成式为:1+x+x4+x5+x12,通过一个线性反馈移位寄存器可以方便地实现该伪随机序列。如图5所示,该M伪随机序列发生模块在全局时钟的控制下即可产生出0、1的M伪随机序列,通过数据线 dataout将随机序列值传递到按键控制模块的相位累加器,以达到抑制相位截断带来的误差。

图5 M伪随机序列发生模块原理图

RAM存储模块由 8×1 024 bit的双口 RAM组成,可完整存储一个周期的波形数据,波形幅度为127。

2.2LabVIEW上位机设计

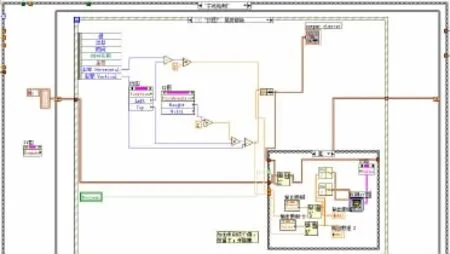

本设计使用LabVIEW 8.6开发了一个任意波形发生器的上位机软件,在该软件操作界面上可以选择输出波形的种类和参数,也可以手动绘制任意波形,其软件界面如图6所示。

图6 任意信号发生器软件界面

任意信号发生器软件界面由 LabVIEW的前面板和后面板构成,在前面板中主要由一些组件构成,如按键组件、文本输入组件、显示组件等。前面板的显示部分在手动绘制模式下为波形绘制区域,绘制过程中该组件右下角可提示鼠标所在坐标以及指示灯提示。在正弦波、方波、锯齿波、三角波、高斯白噪声、叠加正弦波、自定义公式等常规波形模式下,该显示组件仅发挥显示功能。面板下方有一些文本输入组件,这些组件可以用来调节波形的频率、幅度、相位以及占空比等波形相关参数,方便灵活地设计各种波形信号,这里波形频率与最终输出频率有关,所以默认设计为1。前面板右下方为串口通信组件,可以设定 COM口、波特率、终止位数、数据位数、流控制、奇偶校验以及发送间隔时长等相关参数。同时在设计中也对软件的采样点数进行了设置,由于本设计采用1 024 B存储空间,故这里默认设置为1 024,实际使用中也可根据实际情况进行设置。

在设计前面板的同时,也需要对其后面板进行设计,前面板仅作为一个友好的用户操作平台,其操作的所有对象的数据需要在后面板上对其进行分析处理,将处理后的结果再返回到前面板显示,因此后面板的设计尤为重要。

由前面板的设计可知,本设计的DDS任意信号发生器可以实现正弦波、方波、锯齿波、三角波、高斯白噪声、叠加正弦波、自定义公式以及任意波形绘制。在后面板设计中这些常规波形LabVIEW都提供了专门的图形化模块,可以直接调用产生相应的波形。这里为了能够将这些波形以及手动绘制波形完全兼容地显示到XY图组件上,采用公式波形组件创建了一个线性递增的采样计数,便于统一管理所有的波形数据。

在手动绘制波形部分,主要通过事件结构完成鼠标绘制图形的功能,并通过各个模块的属性节点来传递各个模块属性值,使得图形化编程更加易于控制。在鼠标的位置计算上通过显示模块XY图的属性节点传递,得到XY图组件坐标位置的左上方坐标点,以及XY图组件的实际长度及宽度。得到了这些数据,便可以将XY图组件坐标原点方便地调节到XY图组件的左侧居中位置,形成一个抽象上的X轴。而Y轴则根据波形幅值的范围,以X轴为分界点一分为二,即形成一个抽象的坐标系。这样便可以方便地将XY图组件中的波形数据转换为实际的波形数据,便于串口通信组件的发送;同时也利于在手动绘制模式时,鼠标实际位置的计算。通过鼠标经过的路径实时地将坐标显示出来,即可完成鼠标波形绘制的功能。手动设计原理如图7所示。

图7 手动绘制模式设计图

在串口通信部分采用LabVIEW集成的串口通信模块。根据其设计流程,依次将 VISA组件中的 VISA串口配置模块、VISA串口启动模块、VISA串口写模块以及VISA串口关闭模块加入到后面板,联通各模块并将输入数据按照输入格式进行数据类型转换,使通信畅通,即实现波形数据在上位机与FPGA之间的通信。

3 仿真与测试

为验证优化设计,在FPGA仿真阶段对本设计进行了功能仿真。仿真软件采用 Mentor公司的 Modlesim,通过书写测试激励文件,结合Quartus II的设计网表文件,共同载入Modelsim仿真环境进行仿真,得到了图 8所示的仿真时序图,从仿真结果可以看出,经 FPGA处理输出的波形信号质量高,符合设计要求。经测试,本DDS任意信号发生器的常规波形频率范围为 0.03 Hz~40 MHz,任意波形频率范围为0.03 Hz~20 MHz,其频率分辨率为 0.03 Hz,幅值分辨率为 8 bit,幅度范围为-3 V~+3 V,相较于参考文献[1],在波形输出频率上提升了10%,在频率分辨率上提升了 40%。由于相位杂散的影响,在锯齿波的最高频率处出现了小幅度的间隔,在方波的高低电平处存在一定的纹波,但波动控制在极小幅度范围之内,能够满足一般工业应用。在幅值量化上,由于采用有限位宽的数字信号进行模拟量的量化,因此不可避免地会产生极小的量化误差,但通过低通滤波器的处理,能够理想地还原出原始信号,符合预期的设计目标。

图8 仿真测试图

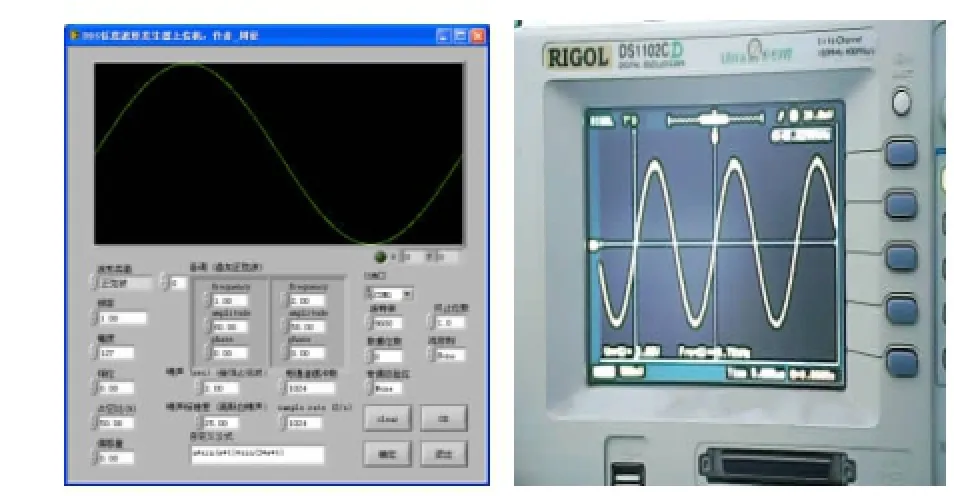

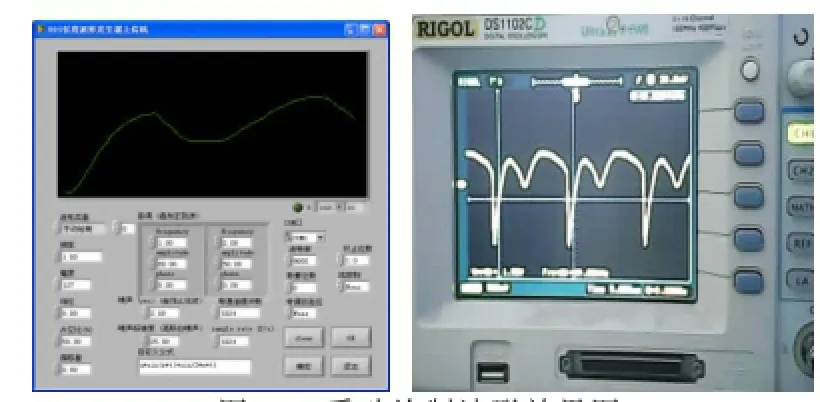

设计采用RIGOL的DS1002C双通道示波器测试仪器进行了板级测试,其具有良好的波形存储功能,采样率高达25 GS/s,带宽为100 MHz。其效果如图9、图10所示。

图9 正弦波效果图

4 结论

本文通过在FPGA平台上实现DDS任意信号发生器的硬件平台,采用LabVIEW设计上位机软件与FPGA硬件平台进行通信,实时更新波形数据,拓展了 DDS任意信号发生器的波形种类,增强了其灵活性。

图10 手动绘制波形效果图

本设计实现了采用相位截断的方法提高设计的频率分辨率,同时又通过M伪随机序列注入抖动,消除相位截断误差,提高了信号发生器的性能。经仿真验证,证实了本设计的可行性与稳定性。

[1]万志江.基于 FPGA的DDS IP核的研究与设计[J].微电子学与计算机,2013(8):98-102.

[2]刘伟,钟子发,叶春逢.基于FPGA+DDS的信号源设计与实现[J].微型机与应用,2010,29(9):18-20,24.

[3]梁赫西,陈佑红,郑朝霞.基于FPGA的可配置FFT_IFFT处理器的设计与实现[J].电子技术应用,2012,38(3):57-59.

[4]哈立原.基于FPGA的直接数字式频率合成器设计[J].内蒙古大学学报,2013,44(4):409-413.

[5]LARSON D C.High speed direct digital synthesis techniques and application[J].IEEE,1998:209-212.

[6]AlteraCorporation.CycloneIIdevicehandbook[EB/OL]. www.altera.com.2005.

[7]Analog Devices.AD9740 10-Bit,210 MSPS TxDAC D/A Converter[EB/OL].(2005-01-03).[2014-09-01].www.analog.com.

DDS arbitrary signal generator based on FPGA and LabVIEW

Liang Hexi1,Zhou Mi2,Xie Hucheng3

(1.Educational Information and Technology,Hubei Normal University,Huangshi 435002,China;2.Electronic Information School,Wuhan University,Wuhan 430074,China;3.Wuhan Huazhong Numerical Control Co.,LTD.,Wuhan 430000,China)

This paper implements a platform based on FPGA and LabVIEW arbitrary waveform generator.By FPGA it built hardware platform,achievred serial communication with LabVIEW PC software,adjusted the FPGA waveform data in real time,and enabled sine,square,sawtooth,triangle,Gaussianwhitenoise,superimposedsine,customformulasandotherconventional waveform.You can also manually draw arbitrary waveform,fully exploiting the flexibility of the software.By setting the parameters,the design can be more convenient for all waveforms.The design of the EP4CE15F17C8 chip works with LabVIEW PC software,the system has been tested and has good stability and flexibility.

DDS;FPGA;LabVIE

TN92

A

1674-7720(2015)02-0025-04

2012国家大学生创新创业训练计划项目(201210513022)

(2014-09-19)

梁赫西(1982-),男,硕士,讲师,主要研究方向:FPGA数字系统设计。

周密(1992-),女,硕士研究生,主要研究方向:集成电路设计。

谢虎城(1992-),男,工程师,主要研究方向:数字集成电路设计。