一种开源软核OR1200的系统级描述方法研究※

2015-08-14吴琼飞张志强朱勇

吴琼飞,张志强,朱勇

(1.华中农业大学楚天学院,信息工程学院,武汉430205;2.武汉纺织大学)

吴琼飞(讲师)、张志强(助教)、朱勇(教授),研究方向为嵌入式系统及应用。

引 言

专用指令集处理器(ASIP)是一种具有处理器结构的芯片,它具有可定制性,为某个或某一类型应用而专门设计,能够高效地解决嵌入式系统设计中的实际问题,已在现今的片上系统(SoC)中得到了广泛的应用。但在系统定制ASIP处理器时往往受到芯片面积、上市时间(TTM)和功耗等非功能性的约束[1,4-5],设计者必须要找到一款合适的处理器体系结构,所以在设计的初期要针对特定应用进行设计空间搜索(DSE),利用ADL对目标结构进行描述并用硬件描述语言(HDL)来进行硬件实现。传统设计方法是直接使用 HDL语言来进行硬件设计[6,9],从而导致设计周期相当漫长。本文探讨了一种基于SystemC体系结构描述语言的系统级设计方法,对一款开源软核OpenRISC1200(以下简称OR1200)进行系统级建模,并在此基础上实现系统级的综合,由ADL描述通过相应机制映射成RTL级的HDL描述,加快处理器的设计速度。

1 OR1200软核剖析

1.1 OR1200CPU基本结构

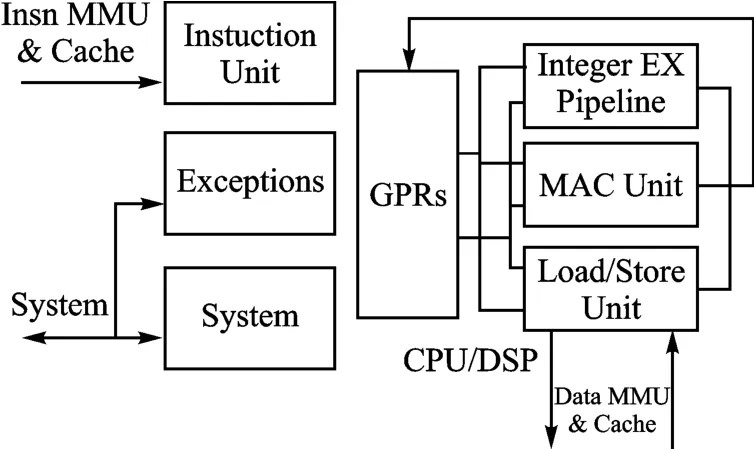

OR1200是OpenRISC系列RISC处理器内核的一员,它是一种32位标量RISC体系结构[14],具有哈佛结构,带有5级整数流水线。其执行特征包括虚拟内存支持和基本DSP功能,外部数据总线和地址总线接口符合Wishbone总线标准。OR1200CPU/DSP基本框图如图1所示。

图1 OR1200CPU/DSP基本框图

1.2 OR1200CPU 5级流水结构分析

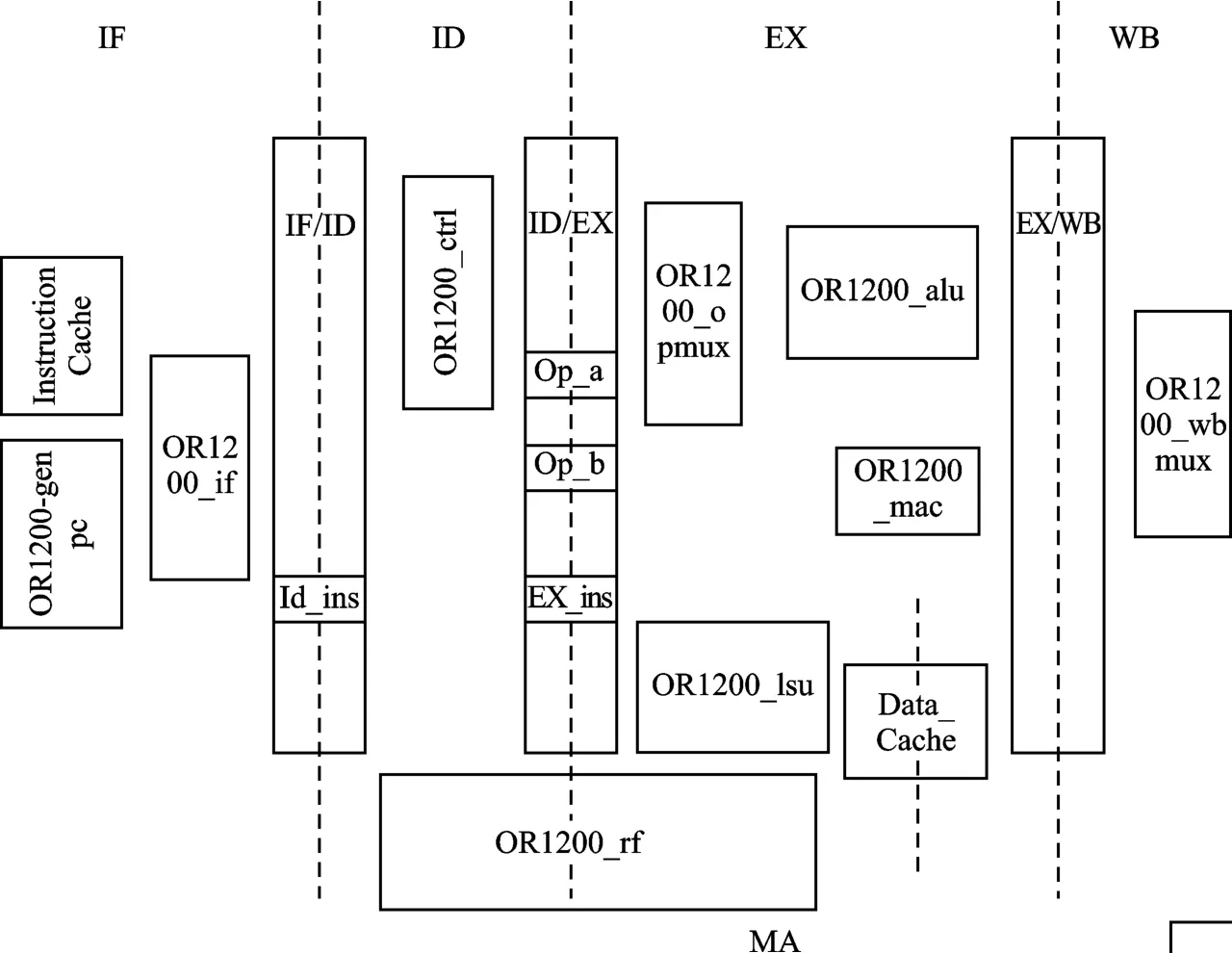

OR1200 5级流水是指IF取指、ID译码、EX执行、MA存储、WB回写,这里将CPU分解成若干个模块,每一级都对应相应的模块,5级流水的OR1200CPU内部模块如图2所示。

各级流水的功能分别如下:

图2 5级流水的OR1200CPU内部模块

①IF(Instruction Fetch)取指级,按照PC的地址从存储器中取出指令,PC指向下一条指令,取出的指令被送到下一条流水级ID。为了保证运算能按时进行,在这个时钟周期需要提前提取操作数RA和RB寄存器的内容,寄存器的地址rf_addra/b和读信号rf_rda/b在本流水线级未被冻结时给出。

②ID(Instruction Decode)指令译码级,指令被ctrl模块解码成控制信号,所得到的这些信号被送到EX执行级和其他流水级。指令在EX执行级时需要用到来自rf(寄存器堆)的2个操作数,这2个操作数在ID级被送到算术逻辑运算单元ALU的a、b两个端口,同时译码级还要把译码后得到的运算操作信号OP传递给ALU。对于跳转指令分为非条件跳转和条件跳转。如果译码器ctrl识别到非条件跳转,会马上通知IF级;如果识别到的是条件跳转,就会根据标志位判断跳转的结果,从而决定是否立即通知IF。另外,如果译码器识别到指令HALT,则会停止流水线。

③EX(Excution)执行级,它主要通过ALU实现算术和逻辑运算。

④ MA(Memory Access)存储器访问级,它使用Load/Store指令从存储器装载数据到寄存器堆或从寄存器堆存储数据到存储器,或者只是将EX级的运算结果送到下一级WB回写级中。

⑤ WB(Write Back)回写级,主要是把数据写回到寄存器堆rf中。

2 系统级描述方法研究

2.1 系统级设计方法

嵌入式系统的设计[8,10]是一个由高抽象级到低抽象级的逐层实现过程,每一层都会涉及到描述、验证以及到下一层的转换(综合)问题。系统级包含硬件和软件等多种实现,与RTL级相比处于更高的抽象层次,它能实现对微处理器、专用集成电路、可编程逻辑和存储器等的高层次抽象。

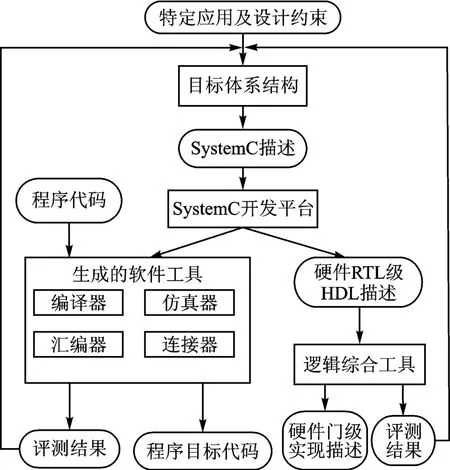

针对传统设计方法的不足,本文提出了一种基于系统级描述语言SystemC的设计方法,基于SystemC的ASIP设计流程如图3所示。

图3 基于SystemC的ASIP设计流程

首先针对一组特定应用以及设计约束分析得到初始目标体系结构[7,13],然后对目标体系结构进行SystemC描述,通过SystemC开发平台自动生成相应的软件工具(包括编译器、仿真器、连接器等)以及硬件RTL级HDL描述,之后分别从软件和硬件两个方面进行评测,看是否符合设计约束要求。如果不符合设计约束要求,设计人员对目标体系结构的SystemC描述进行相应的修改,最后通过开发平台完成软件工具和硬件描述的生成并对其进行评测,直到满足设计约束要求为止。

2.2 体系结构描述语言SystemC

SystemC作为一种硬件描述语言,是由OSCI(Open SystemC Initiative)组织制定和维护的、开放源代码的、基于C++类库的系统级建模平台。它既是一种软硬件协同设计语言,又是一种新的系统级建模语言,可以用来设计硬件模型和提供硬件模拟平台。

在SystemC中,用来进行设计描述的基本SystemC类是SC_MODULE,它类似VHDL的实体ENTITY或者Verilog的模块MODULE。在SC_MODULE中可以定义输入引脚、输出引脚、内部信号等资源,同时也可以实例化另外一个SystemC MODULE,对于设计的行为可以使用方法SC_METHOD或者SC_THREAD进行描述。SC_METHOD或SC_THREAD在SC_MODULE内的构造函数中进行声明,并且可以指定相应的敏感信号列表SENSITIVE,随着敏感列表上输入信号的变化从而产生相应的方法。SystemC能在内核的基础上建立信号、FIFO等,它结合了高级语言和硬件描述语言这两者的特点[2-3],系统抽象能力强,并能对硬件设计中的信号同步、时间延迟、状态转换等物理信息进行描述,所以SystemC可以很好地应用于ASIP系统级设计中。

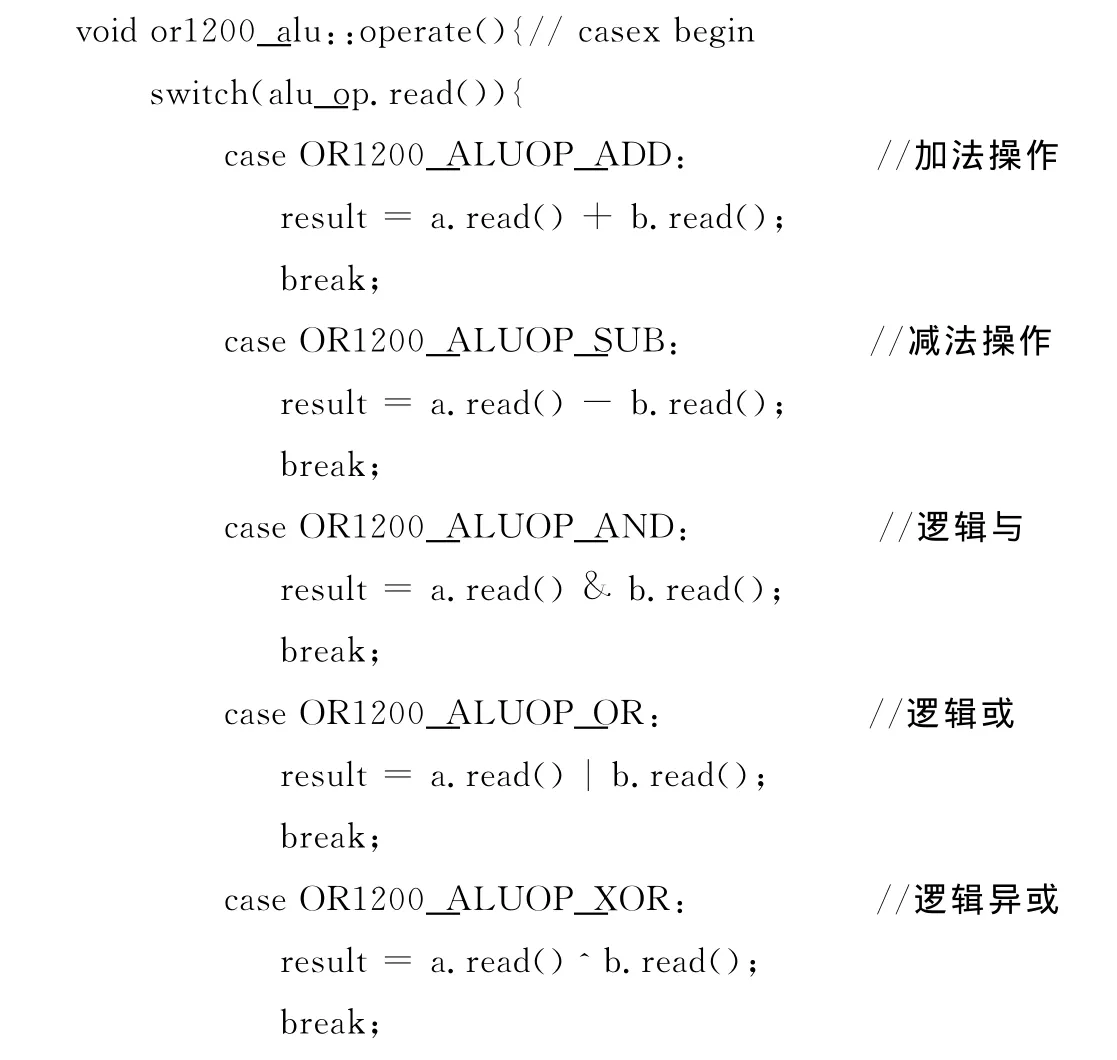

2.3 OR1200CPU系统级SystemC描述

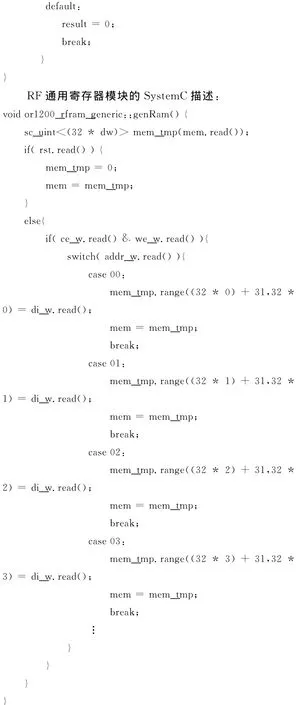

在系统级对ASIP处理器进行设计,ADL是整个设计的核心。利用SystemC在系统级对OR1200CPU内部模块进行描述,并通过一款可集成开发软件Agility Compiler实现SystemC的综合,加快了硬件设计的实现。在实现的过程中,目前只用到了if(取指令)、getpc(程序计数器)、ctrl(控制译码器)、rf(通用寄存器文件)、opmux(操作数多路复用器)、alu(算术逻辑单元)、lsu(load/store单元)和wbmux(写回)这8个模块。下面的例子是使用SystemC对OR1200CPU部分模块进行系统级描述的部分代码实现:

3 系统验证

采用一种将新的高效测试方式与传统的系统测试方式相结合的手段,利用嵌入式逻辑分析仪进行验证,设计人员将它连同目标文件一起下载到目标器件的芯片中(这里是EP2C70F896),以此来获得目标器件芯片内部信号节点处的相应信息,同时硬件系统还能正常工作,这就是QuartusII中SignalTapII的目的。在实际检测过程中,SignalTapII[14]将采集到的样本信号临时存入到目标器件的RAM中,然后通过目标器件的JTAG口将采样信息传入到计算机中显示,最后进行分析。SignalTapII能够对被测试系统模块内部的信号节点进行采样,并且它是由多时钟驱动的,能通过设置相应的参数来显示前后触发捕捉信号节点信息的比例,便于对数据进行分析。当然在验证系统之前,要设计好指令Testbench,本文根据OpenRISC ORBIS32指令集用汇编语言设计了3类指令Testbench:无冲突的指令Testbench、有冲突的指令Testbench和有跳转的指令Testbench。为了测试利用SystemC设计后的OR1200CPU是否能正常工作,事先设计好测试指令的相应编码mif文件,利用Altera Quartus II自带的SignalTap II工具仿真验证,系统验证结果略——编者注。

结 语

本文设计实现了一种对ASIP进行系统级高层综合的方法,以一款开源软核OR1200为实例,ADL体系结构描述语言SystemC为核心,通过Agility Compiler编译器实现系统级综合。实践证明,这种基于体系结构描述语言SystemC的系统级设计方法是可行的。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1]杨君.专用指令集处理器(ASIP)体系结构设计研究[D].合肥:中国科学技术大学,2006.

[2]申鑫.基于SystemC的RTL级综合的研究[D].西安:西安电子科技大学,2012.

[3]鲁芳,柏娜.基于SystemC和Verilog软硬件协同验证[J].现代电子技术,2008(4):1-3.

[4]杨君,李曦,王志刚,等.专用指令集处理器(ASIP)系统级设计研究[J].系统工程与电子技术,2006,28(10).

[5]李曦,龚育昌.基于Petri网的ASIP体系结构形式化建模方法研究[J].小型微型计算机系统,2006,27(9).

[6]苏鹤年,李曦,王志刚,等.基于语言的ASIP系统级综合方法研究[J].微型机与应用,2005(9).

[7]余洁.专用指令集处理器可靠性评估技术研究[D].合肥:中国科学技术大学,2007.

[8]王志刚.xpMODEL:A Novel Model for ASIP Architecture[D].合肥:中国科学技术大学,2006.

[9]Yong Zhu.The Specification of the Embedded System of Realtime IR,DCABES 2007(ISTP),2007.

[10]Yong Zhu.The ASIP Design Specification Based on ADL,DCABES2009(ISTP).

[11]Fanucci L,Cassiano M,Saponara S.ASIP Design and Synthesis for Non Linear Filtering in Image Processing,Design[J].Automation and Test in Europe,2006(12):1-6.

[12]Morgan P,Taylor R.ASIP Instruction Encoding for Energy and Area Reduction,Design Automation Conference,2007[C].California:[unknown],2007.

[13]Dan Wu,Zhiying Wang,Kui Dai,et al.A Novel Compiling Approach for Sub-Word Parallelism Exploitation in Media-Processing Algorithm,5th International Symposium on Parallel Computing in Electrical Engineering(PARELEC 2006,IEEE Computer Society),2006[C].Bialystok:[unknown],2006.

[14]Altera Corporation.Quartus II Handbook,volume 5,2007.