基于FPGA的图像边缘检测算法设计

2015-08-09王静

王 静

(安康学院电子与信息工程系,陕西 安康 725000)

在数字图像处理以及对物体的识别、计算机视觉、生物医学、人工智能、遥感、气象预测学等诸多领域中,图像的特征提取有着很重要的作用。边缘是物体一个不变的特性,同时人的视觉系统对边缘也是最敏感的,因此边缘检测是图像处理的重要内容,它已经成为众多学者研究的重点和热点之一。

1 边缘检测

图像边缘检测与提取的技术研究一直贯穿于图像处理与分析的始终,边缘检测指“在一幅有一个或多个物体图像的画面中寻找其三维边界,如阴影、纹理、边沿等”通常通过图像中某些确定点的灰度值、色度等来分辨出物体的边界。从狭义上也可以说,边缘检测“主要是图像灰度变化的度量、检测和定位”[1]。

2 数字图像边缘检测技术的基本实现步骤

2.1 滤波。边缘检测算法主要是基于图像灰度的一阶导数和二阶导数,但导数的计算同样对噪声很敏感,因此必须使用滤波器来改善与噪声有关的边缘检测方法的性能。

2.2 增强。增强边缘的基础是确定图像中各点邻域强度的变化值。

2.3 检测。在图像中有许多梯度幅值比较大的像素点,而这些点并不一定都是想要的图像边缘,所以应该用某种可靠的方法来确定哪些点是边缘点。最简单可靠的边缘检测就是根据图像幅度阈值来判断。

2.4 定位。确定边缘所在的像素,也可以在亚像素分辨率上来估计边缘位置,边缘的方向也是可以被估计出来的。

3 硬件加速器

硬件加速器是指利用硬件模块来代替软件算法。硬件在执行各种操作时要比软件快得多,其优势尤其表现在对大量数据进行计算和传输方面。

4 图像边缘检测的Sobel算法硬件加速器实现

4.1 原理和步骤

4.1.1 Sobel 边缘检测法的机理。Sobel 边缘检测法的机理是计算x 和y 方向亮度信号的导数值并且寻找导数中的最大值和最小值。这些区域也就是亮度变化最剧烈的区域[2]。

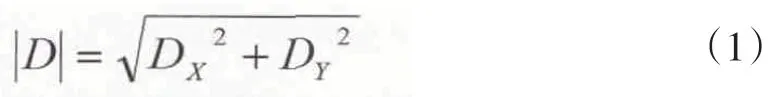

Sobel 检测法通过叫作卷积的过程来估计每个像素点在每个方向上的导数值。分别用于计算x 和y 方向导数值的Sobel卷积表Gx和Gy点和离它最近的8个像素点每个乘以一个系数后相加。先把每个像素值分别乘以卷积表中对应的各系数,再把相乘得到的9个数相加就可以得到x方向和y方向的偏导数值Dx和Dy。然后,利用这两个偏导数值计算中心像素点的导数。计算公式如下:

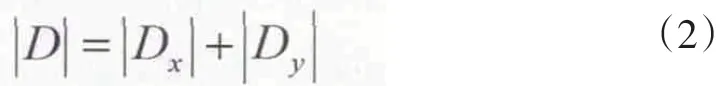

由于只想得到导数幅值的最大值和最小值,对上式作如下简化:

这样近似能够满足计算要求。并且,与计算平方和开平方相比,计算绝对值所用的硬件资源少得多。

它需要重复地计算图像中每个像素位置导数的幅值。最简单的方法就是把图像中边缘像素点的导数数值|D|都设置为0[3-4]。

4.1.2 计算Sobel卷积比特数

计算Sobel 卷积中表示每个像素点中间值和最终值所需要的比特数,

求出每个Dx和Dy的值需要把各自的9个部分积相加。

4.1.3 确定能够满足计算性能的并行结构方案

按照要求同时对尽可能多的像素进行并行计算。从原始图像的顶部像素开始,通过独立并行操作得到中间结果,最后求出底部的导数像素。然后可以并行地把两组各6个部分积加起来,再并行地计算两个绝对值,把它们加起来最后得到(原始图像某个像素的)导数像素值[5]。

4.1.4 确定加速器的结构

原始图像的像素,一旦被读取,就可以用来计算该像素的后一列、本列和前一列中3个像素的导数,这样可以进一步减少所占的内存带宽。

4.2 边缘检测加速器具体实现结构

从原始图像中读取三行,每行4个相邻的像素,把这些像素值存储在加速器的寄存器中以待处理。

计算流水线按照每4个像素值一组的形式产生给定行的导数像素值。加速器从内存中的上一行、本行、下一行各读取4个像素点到右上角的3个32位寄存器中。在接下来的4个时钟周期里,像素值依次左移,每次移一个像素值,到乘法器阵列中。阵列中的每个单元包括一个像素值寄存器和一个或两个乘法电路。乘法电路用于把像素值寄存器中存储的像素值乘以一个常量系数。

在每个时钟周期,硬件电路阵列提供了求一个导数像素值所需要的部分积,部分积加起来后存储到Dx和Dy寄存器中。同样,在每个时钟周期,计算出前一个像素值的Dx和Dy的绝对值,加起来后存储到|D|寄存器中。|D|寄存器中的导数像素值左移到结果行寄存器中。当寄存器中4个结果像素值都准备好后,随即被写入到内存中。进入稳态后,在处理一行的过程中,加速器在移入新的像素值到乘法法器阵列,Dx,Dy和|D|寄存器之前,需要把导数像素值从结果寄存器先写到内存中。再读入3组各4个像素点,像素值按时钟节拍移入计算流水线,当结果寄存器填满4个像素值后,再次写到内存,然后不断重复这个过程。

当到达一行的结尾,需要排出流水线中的数据。因为一行里像素点的个数是4 的整数倍(640=160×4),每次都可以读到包含4个像素值的完整组。当把一行里最后4个像素读入读寄存器,经过4个计算周期后,结果寄存器被移入4个新的结果值,同时读寄存器中的像素值被全部移入流水线中。然后结果寄存器被写入内存。由于整行像素已经被读完,不执行读操作。此时,流水线中还有数据,再执行4个计算周期排出流水线中的数据。

[1]夏宇闻.Verilog数字系统设计教程[M].北京:北京航天航空大学出版社,2003.

[2]黄智伟,王彦.FPGA系统设计与实现[M].北京:电子工业出版社,2005.

[3]姚远,李辰.FPGA 应用开发入门与典型实例(修订版)[M].北京:人民邮电出版社,2010.

[4]徐志军.大规模可编程逻辑器件及其应用[M].成都:电子科技大学出版社,2000.

[5]吴厚航.深入浅出玩转FPGA[M].北京:北京航天航空大学出版社,2010.