电磁频谱监测中的宽带实时信号采集系统设计

2015-08-07丁宏毅柳其许

丁宏毅,柳其许

(中国卫星导航定位应用管理中心,北京100088)

电磁频谱监测中的宽带实时信号采集系统设计

丁宏毅,柳其许

(中国卫星导航定位应用管理中心,北京100088)

介绍了一套宽带实时信号采集系统,系统由信号调理单元、时钟调理单元、模数转换单元、FPGA、高速缓存单元、PCIE接口以及电源组成。通过采用超高速ADC、优化传输方式、优化数据存储架构,系统实现了超高速实时宽频带信号数据的采集、传输与记录。系统软件针对数据采集中的高速数据传输方式进行优化设计,通过利用双通道技术,系统的总数据吞吐量能够达到5GB/s。测试结果表明,系统在2GHz带宽内达到了较高的动态指标,能够满足高速频谱信号的记录需求。

实时信号;数据采集;超高速;宽带;频谱记录;数据传输

1 引 言

现代战场环境中的电磁信号十分密集,信号类型复杂多样,战场电磁环境对战争准备和各种军事斗争活动,尤其对战场感知、指挥控制、作战行动、武器效能、战场建设等方面,影响广泛而深刻。电磁频谱监测能够对战场上无线电发射的基本参数进行测量,对信号进行监听,对发射目标进行识别确定,对频段利用率和频道占用度进行统计,对信号使用情况进行分析,以保障己方的电子设备发挥其最大的作战效能,同时获取敌方电子设备辐射的相关信息[1]。

在电磁频谱监测应用系统中,由于计算机的实时计算能力有限,大量频谱数据不能够完成实时分析与处理,这种情况下需要对频谱信号进行采集和记录,再进行事后分析。为了达到较高的分析带宽,记录的信号数据速率可能达到GB/s量级,传统设备很难保证这种情况下数据的实时采集、传输与存储。

为了保证宽带频谱信号能够完整并高速地记录下来,文中评估介绍了一套宽带实时信号采集系统。通过采用超高速ADC、优化传输方式、优化数据存储架构,本系统实现了超高速实时宽频带信号数据的采集、传输与记录。

2 系统架构

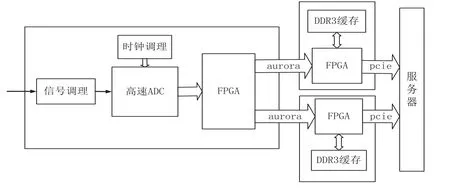

系统由信号调理单元、时钟调理单元、模数转换单元、FPGA、高速缓存单元、PCIE接口以及电源组成,如图1所示。其中信号调理单元完成信号的匹配接收、增益控制;模数转换单元(ADC)由内部时钟或者外部时钟驱动,最高采样速率5Gsps,采样精度10bit;高速缓存单元采用DDR3,缓存深度2GB;采集单元通过主控服务器将采样数据存储至固态存储阵列以便后续的信号处理和分析。

图1 系统架构

3 子电路设计

3.1 信号调理单元

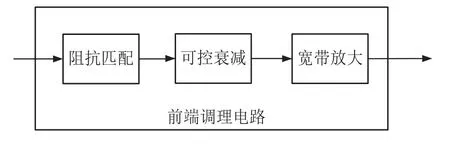

模拟信号调理单元主要完成输入模拟信号的端接匹配、放大、衰减、滤波,如图2所示。信号调理单元由阻抗匹配模块,数控衰减器以及低噪声运算放大器组成。低噪声运算放大器采用Hittite公司的HMC460LC5,这是一款GaAs工艺的低噪声运算放大器,支持直流到20GHz带宽。HMC460LC5能够提供14dB的增益,其噪声系数只有2.5dB。数控衰减器采用Hittite公司的HMC424ALP3E,这是一款DC到13GHz的数控衰减器,能够提供0.5dB步进的可调衰减,最大衰减值31.5dB[2]。

图2 调理电路

3.2 模数转换单元

为实现宽带频谱信号的采集,系统中采用E2V公司的EV10AQ190采样率5GS/s ADC,EV10AQ190支持的最高采样率为5Gsps,支持四通道1.25GS/s,双通道2.5GS/s,单通道5GS/s三种采样模式,采样位数10bit。其-3dB输入带宽可达3.2GHz,1.2GHz输入频率下动态无杂散范围54dBc。芯片具有500mVpp模拟输入幅度,采用LVDS输出总线与FPGA通讯。每通道功耗为1.4W。EV10AQ190内部有四个独立的1.25GS/s ADC,具有移相功能的时钟缓冲器,模拟多路开关以及采样保持电路。在四通道交错采样模式下,1.25GHz时钟及其延时90°/180°/270°共四路时钟,分别提供给四个并行的模数转换内核。此时ADC相当于1路5GS/s采样,可以对2.5GHz以下的带宽实现全覆盖采样[3]。

3.3 高速调相时钟发生单元

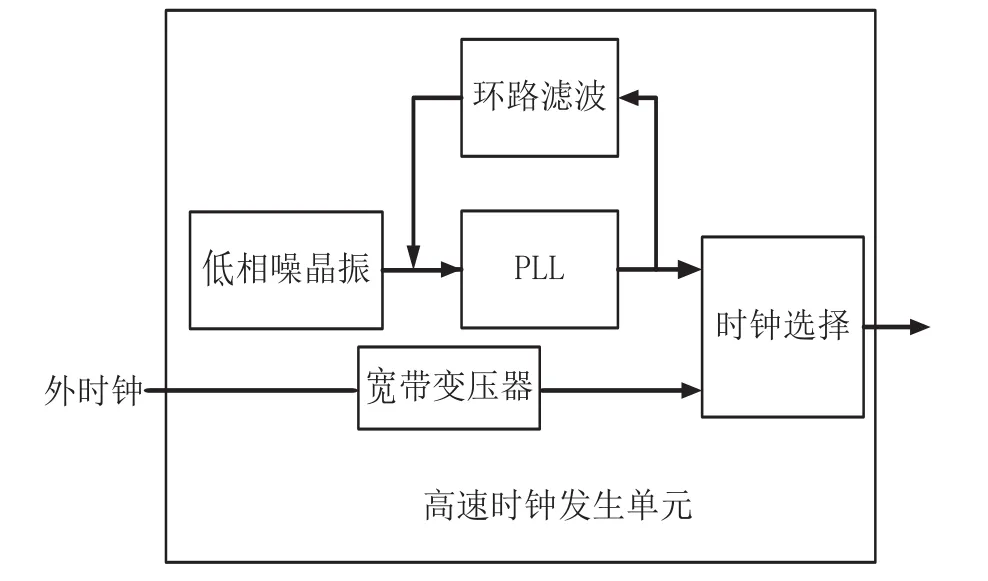

高速ADC对于采样时钟的要求十分严格,时钟抖动将会制约ADC信噪比的提高。在器件选择上尤其要关注芯片引入的抖动(jitter),所以在器件选取和电路设计上,必须严格控制器件抖动,以保证整个时钟路径引入的总抖动尽可能小。对于ADC所需的2.5GHz高速时钟,只有使用锁相环才能保证高频时钟的稳定性,故用锁相环芯片产生内部采样时钟,锁相环用于锁定采样时钟频率,而时钟选择芯片用于设置ADC内外时钟之间的切换。电路结构如图3所示。其中锁相环(PLL)采用Hittite公司的HMC1034,这是一款高频时钟发生芯片,内部集成有低噪声锁相环,其频率范围能够涵盖125-3000MHz,附加的抖动低于78fs,相位噪声低至-165dBc/Hz[4]。

3.4 高速传输单元

高速传输单元由两块基于FPGA的高速传输卡组成,其中每块FPGA与ADC后端的FPGA通过光纤相连,其通讯协议采用AURORA协议。Aurora8B/10B是一个面向高速串行通信的可扩展轻量级链路层协议,该协议规范是开放型规范,可用于Xilinx芯片器件中。Aurora可以以低成本、高数据速率、可扩展、灵活的方式构建串行数据通道。系统中的FPGA选用XILINX公司的KINTEX-7系列FPGA,具有较高性能和较低功耗。KINTEX-7系列FPGA还支持PCIE2.08X收发器,适合在系统中用于实现基于PCIE协议的高速传输。传输单元还集成有DDR3内存颗粒,用于数据高速缓存。

图3 时钟电路

4 系统软件设计

系统软件针对应用需求而设计,主要功能是负责把ADC采集的数据传输到存储阵列中。软件通过DMA方式,首先把数据从采集卡传输到上位机主内存,上位机软件再把内存数据转存到固态存储单元中。系统软件针对数据采集中的高速数据传输方式进行优化设计,在PCIE 2.0协议上能够实现2GB/s的数据传输速率,通过利用双通道技术,系统的总数据吞吐量能够达到5GB/s。

上位机软件负责与驱动程序交互,设计统一应用程序访问接口和用户程序界面,监视采集卡的状态和通信链路状态。为保证稳定的数据传输速率,本系统程序采用多线程方式设计,支持不同通道乒乓操作。应用程序通过DMA方式把数据传到客户机的主存当中,同时把主存中的数据通过DMA方式传输到存储卡。为了保证传输速率,存储过程为主线程,采集过程开辟新线程,实现多线程操作,提升系统的数据存储速率。此外,上位机软件可以配置DMA控制/状态寄存器控制DMA操作。DMA控制/状态寄存器映射于PCIExpress Memory BAR0空间,客户端软件通过Memory Write和Read周期访问寄存器。上位机软件通过初始化DMA控制寄存器发起DMA传输,而通过状态寄存器,以中断方式通知Root Complex DMA传输完成[2]。

4.1 多线程高速传输技术

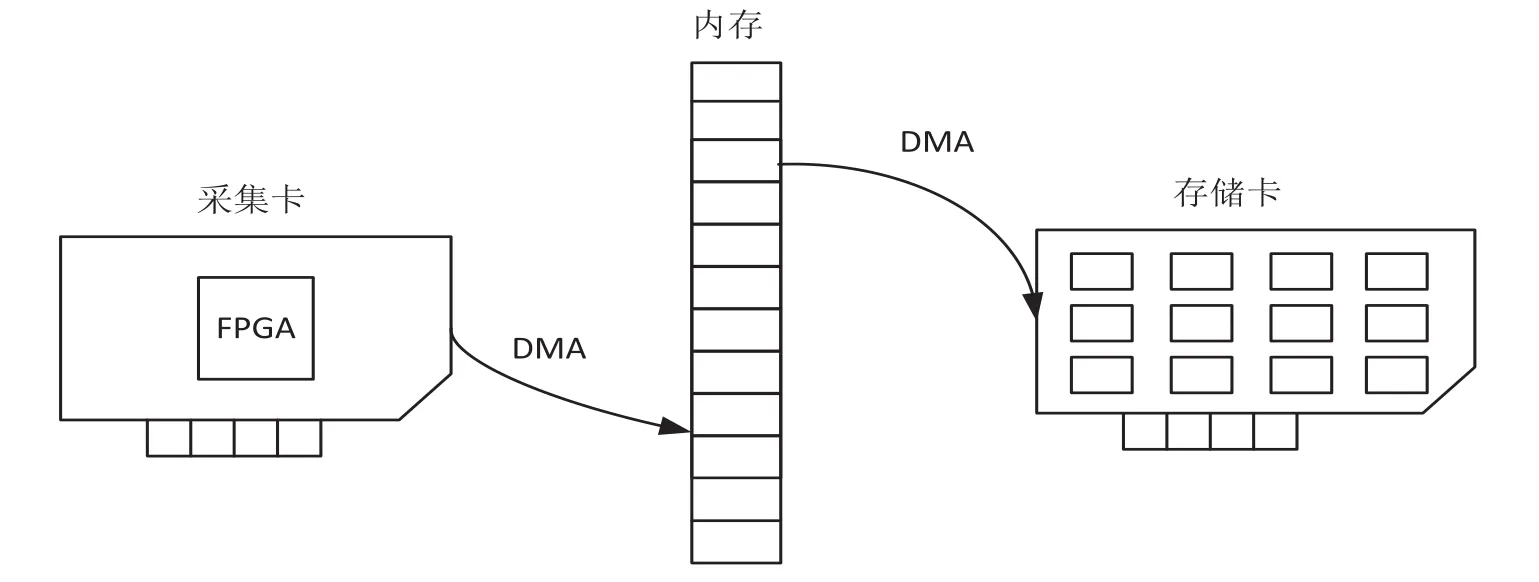

从软件上来讲,该系统由驱动程序、上位机控制程序、存储设备接口程序组成。数据从采集卡流入,进入内存,然后数据再从内存进入存储设备。然而,当数据写入内存时,不能同时读出该内存空间的数据。从而使内存成为了互斥资源,制约了数据传输效率。用户通过虚拟内存对内存空间进行管理,实际上的物理内存空间可能是分散并且不连续的。现在的高速采集卡都支持Scatter-Gather技术,由于需要不断的在不同内存空间中切换,DMA的效率不高。针对以上问题,运用一种超大缓存流水线DMA传输与存储技术,其基本架构如图4所示。

图4 超大缓存流水线传输与存储技术

在该方案中,数据通过DMA方式从采集卡传输到内存,内存中的数据再通过DMA方式存入存储卡。由于采集卡的数据是实时输出的,如果传输速度稍慢,就会导致数据累积,从而出现丢数[6]。高性能存储卡或存储阵列一般都基于闪存,其存储速度也具有一定的波动性。为了保证数据能够完整的存下来,设计了如图4中的超大缓存方案。首先,该缓存空间很大,通常是GB这个级别;其次,该空间是在初始化卡的时候,由驱动程序负责申请,该空间在物理上是连续的,能够保证DMA传输的性能。把该空间分割成许多存储节点,形成一个环结构。采集卡的数据从环尾写入,数据再从环头读出,写和读都分别有独立的线程操作。在写入数据过程中,只要环中间还有剩余空间,就会持续写入。负责读出的线程只要发现环中还有数据,就会持续读出并存入存储卡中。两个线程都是基于DMA进行数据传输,它们实际占用的CPU计算资源很少,线程切换不存在冲突。

该方法具有以下优点:第一,写入与读出分离,两个线程独立,减少了线程切换开销;第二,大缓存能够有效缓冲数据,克服存储卡速度不稳定因素;第三,能够实时监测数据传输状态,若缓存空间占用比例太大,达到百分之百,说明存储速度慢,可能丢数;第四,由于物理空间连续,能够保证最高的DMA传输效能。

4.2 驱动程序开发

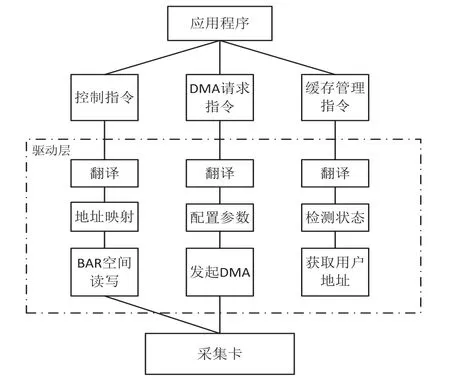

驱动程序负责上位机与采集卡之间的指令传送、DMA传输控制、缓存空间的管理,它是保证整个传输系统性能的关键[7],其基本架构如图5所示。

控制指令主要用来监测采集卡状态、配置卡工作模式,如卡的工作状态、温度信息、卡上的内存空间使用情况、卡的采集模式等。应用程序发送指令,然后经过驱动程序翻译,转变为BAR空间的寄存器读写操作,最后反馈相应的信息给应用程序[5]。DMA操作时由应用程序发起,经过驱动程序转变成DMA请求,驱动程序配置相应参数,其中包括设置DMA大小,DMA的地址,数据传输方式等。当DMA请求完成后,采集卡会给驱动程序发送中断请求,接收到中断请求后完成整个DMA操作,通知上位机应用程序。缓存管理的工作主要是监测缓存状态,实现数据存储队列,保证不出现数据丢失的情况。驱动程序申请连续的物理空间,把物理空间划分成一连串存储节点,构成数据存储队列。新数据从队列首进入,旧数据从队列尾读出。当队列快满时,向应用程序发出警报,调整数据传输策略,进行数据存储。

图5 驱动程序架构

5 系统测试

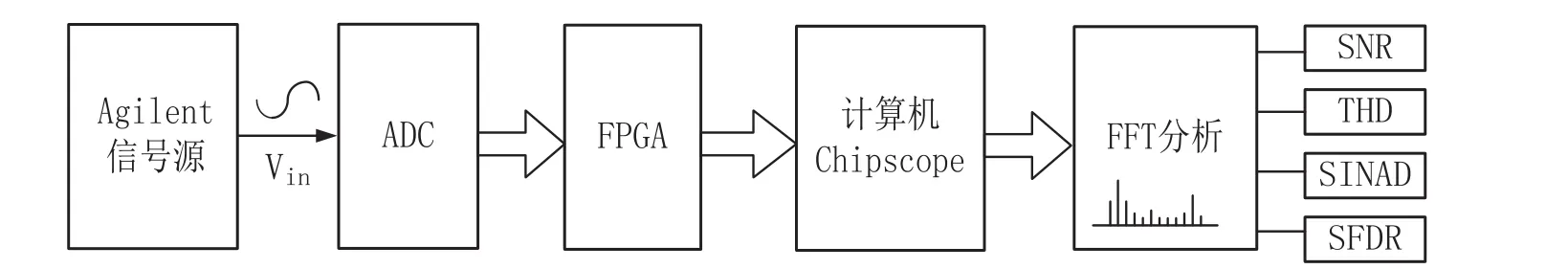

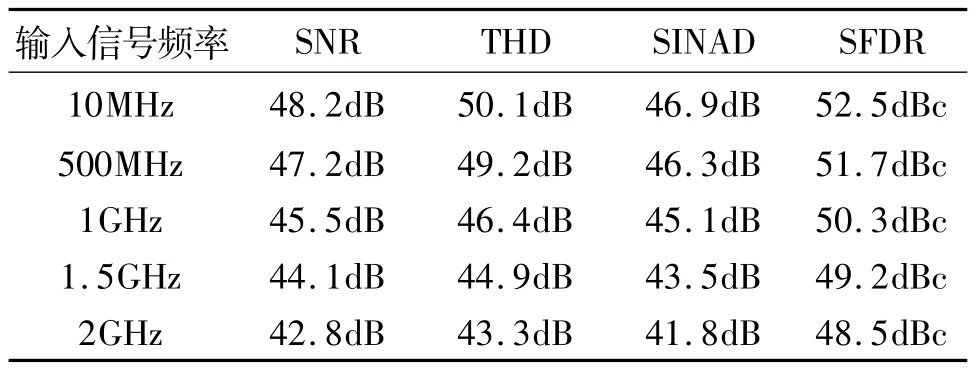

为验证系统性能,采用了多种手段对系统性能进行测试。为测试系统的动态参数,搭建如图6所示的测试系统。测试系统中使用高精度射频信号源产生一个单频正弦电压信号(0dB,10MHz到2GHz),经过ADC电路采集到FPGA,FPGA将存储下来的数字化波形通过Chipscope进行观测,采集结果送到计算机进行FFT变换,最后根据前述公式计算出SNR,THD,SINAD,SFDR等指标。表1列出了系统的主要测试指标和实测结果。

图6 测试系统

表1 系统主要指标和实测结果

从表1可以看出,系统在2GHz带宽内达到了较高的动态指标,能够满足高速频谱信号的记录需求。

6 结束语

为了保证在电磁频谱监测应用系统中保证宽带频谱信号能够完整并高速地记录下来,系统设计通过采用超高速ADC、优化传输方式、优化数据存储架构等手段实现了超高速实时宽频带信号数据采集、传输与记录。系统测试结果表明,在2GHz带宽下,系统达到了较高的动态性能(SNR>40dB,SFDR>48dB),能够有效满足宽带频谱监测的需要,具有很高的实用价值。

[1] 梁百川.战场电磁频谱监测与管理[J].航天电子对抗,2008(4):38-41.

Liang Baichuan.TMonitoring and management of battlefield electromagnetic spectrum[J].AEROSPACE ELECTRONICWARFARE,2008(4).38-41.

[2] HMC460LC5 data sheet.Hittite Microwave[J/OL].2014,http://www.hittite.com/content/documents/data_sheet/hmc460lc5.pdf.

[3] EV10AQ190 data sheet.e2v technologies[J/OL].2013 http://www.e2v.com/products/ev10aq190a-quad-10-bit-1-25-2-5-5-gsps-adc/.

[4] HMC1034 data sheet.Hittite Microwave[J/OL].2014,http://www.hittite.com/content/documents/data_sheet/HMC1034.pdf.

[5] 刘波,库锡树,孙兆林.基于PCIE总线协议的数据采集设备驱动程序实现[J].工业控制计算机,2007,20(7):28-29.

Liu bo,Ku xishu,Sunzhaolin.Driver Develop of Data Gathering Device Based on PCIE[J].INDUSTRIAL CONTROL COMPUTER,2007,20(7):28-29.

[6] 李晃,巩峰,陈彦化.基于PCIE驱动程序的数据传输卡DMA传输[J].电子科技,2014(1):117-120.

LIHuang,GONG Feng,CHEN Yanhua.Data Transmission Card Based on the PCIE Driver[J].Electronic Science and Technology,2014(1):117-120.

[7] 李木国,黄影,刘于之.基于PCIe总线的高速数据采集卡设计与实现[J].测控技术,2013(7):19-22.

Limuguo,Huang ying,Liuyuzhi.Design and Implementation of a High-Speed Data Acquisition Card Based on PCIe Bus[J].Measurement&Control Technology,2013(7):19-22.

[8] 易伟,徐欣,孙兆林.基于WDF的PXIe接口驱动程序开发[J].微处理机,2011(4):86-88,92.

YIWei,XU Xin,SUN Zhao-lin.Development of Driver for PXle Port based on WDF[J].Microprocessors,2011(4):86-88,92.

Design on a High speed Real-time W ide Band Spectrum Signal Acquisition System

Ding Hongyi,Liu Qixu

(China National Administrations of Gnss and Applications,Beijing 100088,China)

This paper introduces a novel wide-band real time signal acquisition system which is consist of signal conditioning unit,clock generating unit,ADC unit,FPGA,high speed buffering unit,PCIE interface and powermodules.Bymeans of ultra-high speed ADC,optimized transferring strategy,and optimized data storage architecture,the system realizes high speed wideband signal recording,transferring and storage.The software of system applies dual-channel technology which achieves 5GB/s data throughput.The test results show that the system achieves the satisfied dynamic performance in 2GHz bandwidth and meets the requirements of high speed spectrum signal recording.

Real-time signal;Data acquisition;Ultra high speed;Wide band;Spectrum recording;Data transferring

10.3969/j.issn.1002-2279.2015.05.023

TP274

A

1002-2279(2015)05-0088-04

丁宏毅(1974-),男,辽宁省兴城市人,学士,工程师,主研方向:卫星导航定位、信号分析处理。

2014-10-23