栅接地NMOS管的ESD特性研究

2015-08-07任志伟崔艾东

任志伟,崔艾东

(中国电子科技集团公司第四十七研究所,沈阳110032)

栅接地NMOS管的ESD特性研究

任志伟,崔艾东

(中国电子科技集团公司第四十七研究所,沈阳110032)

ESD电路的作用是保护集成电路,使静电不损坏芯片内部电路,不造成集成电路失效,因此ESD研究是集成电路可靠性研究的重点方向之一。在新工艺下根据电路特点,设计GGNMOS器件的防护单元,为提供有效可靠的ESD防护起到至关重要的作用。

集成电路;静电释放;栅接地NMOS

1 引 言

随着集成电路制造工艺水平已进入深亚微米时代,集成电路的器件特征尺寸不断缩小,芯片集成度持续提高,先进的工艺对集成电路设计而言是一个福音,但芯片的可靠性问题也日益严峻,ESD防护设计已成为当前集成电路设计中最严重的可靠性问题之一。据统计30%到50%的芯片失效是由ESD放电引起的,这些数据说明降低ESD失效可以给集成电路设计带来很大的提升空间[1]。根据集成电路的新需求,改进或重新设计ESD防护单元,提供有效可靠的ESD防护对电路设计至关重要,具有重要的应用价值。

2 静电释放和栅接地NMOS(GGNMOS)工作原理介绍

ESD(Electro Static discharge)的意思是“静电释放”。静电是一种客观存在的自然现象,产生方式多种,如接触、摩擦、电器间感应等。静电的特点是长时间积聚、高电压、低电量、小电流和作用时间短。生产过程中静电防护的主要措施为静电泄露、耗散、中和、增湿、屏蔽与接地。人体静电防护系统主要由防静电手腕带、脚腕带、手套或指套等组成,具有静电泄放,中和与屏蔽等功能。静电防护在任何环节的失误或疏漏,都将导致静电防护的失败。ESD防护的设计目的就是引导芯片中的放电电流,使其不损坏内部电路,造成IC失效。

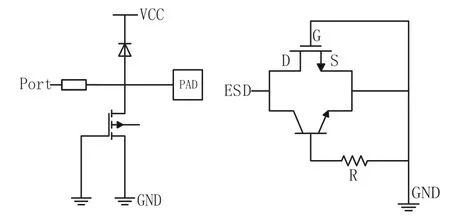

目前应用广泛的ESD防护电路是栅接地NMOS,其中ESD保护电路的一个基本结构如图1所示。它包括:一个栅极接地的NMOS,一个二极管和一个在保护电路和输入输出缓冲端口之间的扩散电阻。栅接地NMOS用以保护从压焊点到地的正负ESD脉冲,MOS管本身没有承受数安培电流的能力,在ESD应用下的MOS管实际的导通结构是其中的寄生双极晶体管。二极管用以保护从压焊点到VCC的正负脉冲,它是电压钳位二极管。扩散电阻起着隔离压焊点和输入输出缓冲端口的作用,在ESD脉冲到来时可以提供一定的延迟功能。

图1 ESD保护结构及GGNMOS工作原理图

2.1 GGNMOS工作原理

GGNMOS主要依靠漏、源、衬底寄生的NPN来释放大电流,从而达到对端口电压的钳位,图1给出GGNMOS工作原理图。设Vav为漏与衬底构成的寄生二极管的雪崩击穿电压,M是雪崩击穿倍增因子,Vd(正的ESD应力)为施加在漏端的电压,则有:M=1/(1-(Vd/Vav)n),当(Vd/Vav)n很小的时候,M=1;当Vd开始接近甚至等于Vav的时候,寄生在PN结发生雪崩击穿,M值开始迅速变大。Iav为产生的雪崩击穿电流,IC是寄生三极管的集电极电流,它们具有如下关系:Iav≈(M-1)*IC,衬底电势Vsub=Iav*R随着电流的增大,Vsub升高。在寄生三极管中,衬底相当于它的基极。当基极电压升至0.7V左右时,寄生三极管开始导通。随着ESD应力进一步增大,寄生三极管将进入回滞区域,大电流可从寄生三极管流向地,从而将端口电压钳置在安全电压以下。当面临负ESD应力时,GGNMOS类似于一个由P-WELL与NMOS的漏端构成的正向偏置二极管。所以说GGNMOS是ESD保护电路的主要组成部分,承担大部分ESD电流的泄放任务。

2.2 器件宽度对GGNMOSESD特性的影响

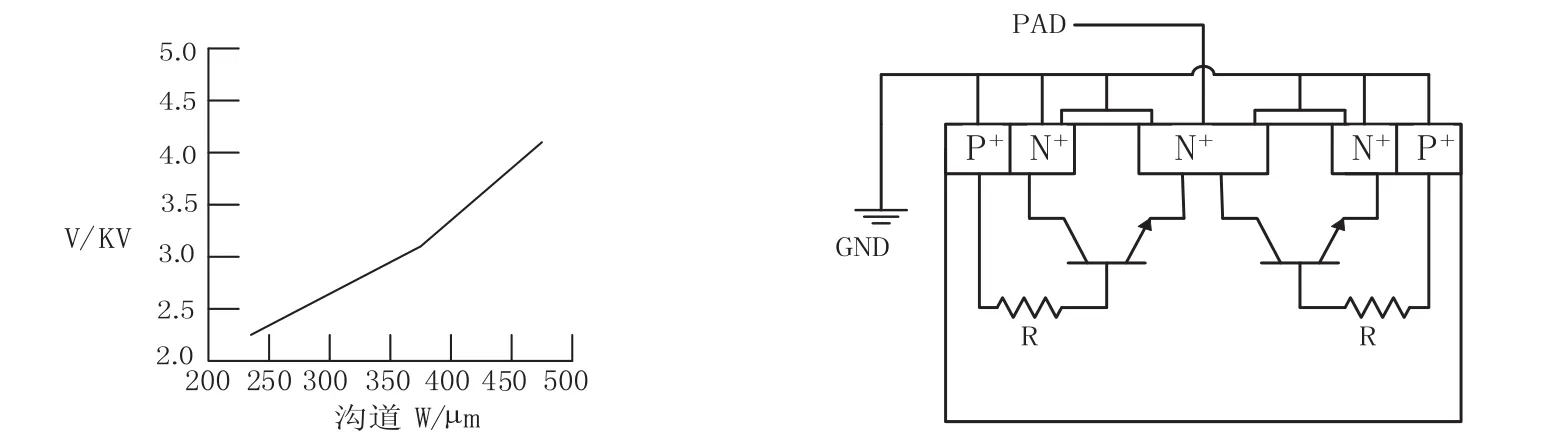

在设计GGNMOS的时候,器件宽度被认为是最重要的物理尺寸,是决定器件ESD防护能力的一个最关键因素。GGNMOS中器件宽度对二次击穿电流起决定性作用。对沟道长度L=0.4μm,漏端孔到栅的距离(DCG)=1.72μm,三叉指的GGNMOS进行TLP测试,结果如图2所示。

图2 器件宽度与GGNMOS抗ESD能力的关系和均匀触发GGNMOS结构

可以看出,随着器件宽度W的增加,GGNMOS的ESD防护能力几乎呈线性增加。但是设计端口ESD防护器件时,不可能一味的增加W。首先这将考虑增加所需的面积,其次将引入更大的寄生电容,W的取值范围大多在80到100μm之间,并采用多叉指结构法来提升ESD防护能力。但是,多叉指结构存在均匀性的问题[2],因为每一根GGNMOS寄生的侧向NPN基极电阻都不一样大。一般是位于中间的那支先开启,因为它的寄生NPN基极电阻最大。为克服这一问题,可在每一根GGNMOS旁边补充一个P+,以保证每一支的寄生NPN基极电阻大致相等,来尽量保证其开启的均匀性。这种结构如图2所示的均匀触发GGNMOS结构。

NMOS的沟道长度L是寄生的侧向NPN的有效基区宽度。随着L的增加,有效基区宽度增加,GGNMOS的触发电压会略有增加。除了会影响GGNMOS的触发电压,理论上L还会影响GGNMOS的二次击穿电流。

2.3 漏端孔到栅的距离和源端孔到栅的距离对GGNMOSESD特性的影响

在设计GGNMOS版图时,漏端孔到栅的距离(DCG)值是需要优化的。在代工厂做时,所有的ESD防护器件都会要求做Silicide Block工艺,所以DCG越大意味着电阻值越大。优化过的值将影响器件的热量散耗以及电流分布的均匀性,热击穿容易发生在较小的角度里面。较大的漏端孔到栅的距离会形成更大的角度更易耗散热量,对于提高二次击穿电流有益。漏端电阻充当镇流电阻的作用,将有益于多叉指GGNMOS的均匀触发。而过大的DCG将带来过大的电阻,增加器件的导通电阻,使其维持电压变大。同时过大的电阻使热耗散增加,降低GGNMOS的抗ESD能力,降低器件的ESD电鲁棒性。在文献中关于GGNMOS漏到栅距离取值的讨论挺多的,理论上GGNMOS工作时,雪崩击穿和热击穿都发生在NMOS的漏区,所以认为漏到栅的距离与器件特性关系紧密,而在源区则无关紧要。但随着器件特征尺寸的日益减少,漏端与源端的距离已经很小了,在漏端产生的热量也会影响到源端。

在0.18μmCMOS工艺下对单指GGNMOS(W=360μm,L=0.35μm),源端孔到栅的距离(SCG)=1.7μm进行测试,通过变化的SCG取值来观察其对抗能力的影响,测试结果如图3所示。

图3 SCG与GGNMOS抗ESD能力的关系

可以看出随着SCG的增加,GGNMOS抗ESD的能力逐步增强,主要原因是此处测试的是单指结构,与参考文献中6叉指结构不同[3]。6叉指结构在泄放ESD电流时是由6根GGNMOS共同工作,每根只要承担约0.4A的电流,所以SCG对器件性能的影响不明显。然而,此处测试的是单指GGNMOS,需要独自承担高达几安培的ESD电流,所以较宽的SCG有益于热量耗散,也能获得更好的抗ESD能力。综上可以得到这样的结论:如果是多叉指GGNMOS,SCG几乎不会影响其抗ESD的性能,所以在设计SCG值的时候,可以根据设计规则尽可能取较小的值。在设计单指大宽度的GGNMOS时,有必要优化SCG的值,以对版图设计起到至关重要的作用。

3 结束语

主要介绍GGNMOS器件的宽度及其漏端孔到栅的距离和源端孔到栅的距离对ESD特性的影响。为以后在进行这类器件的版图设计时,要注意GGNMOS管的结构、尺寸、参数的选择,提供些经验。在ESD防护设计中,版图设计起到至关重要的作用,往往决定整个设计方案的成功与否。

[1] R GWagner,JM Soden,C FHawkins.Extentand Cost of EOS/ESD Damage in an ICManufacturing Process[M].Proc EOS/ESD Symp,2003:49-55.

[2] Ker M,Chen J.Self-substrate-triggered technique to enhance turn-on uniformity ofmulti-finger ESD protection devices[J].Journalof Solid-State Circuits,2006,41(11):2601-2609.

[3] Dong S,Du X,Han,et al.Analysis of 65 nm technology grounded-gate NMOS for on-chip ESD protection application[J].Electronocs Letters,2008,44(19):1129-1130.

Research on ESD Characteristic of Gate Grounded NMOS

Ren Zhiwei,Cui Aidong

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

The ESD circuit is used to protect the integrated circuit chip from electrostatic damage and failure of functions.So the ESD research is one of the key directions of integrated circuit reliability research.According to the characteristics of the circuit in the new technical processing,the protection unit of GGNMOS device is designed to provide effective and reliable ESD protection.

Integrated circuit;Electro Static Discharge;GGNMOS

10.3969/j.issn.1002-2279.2015.01.002

TN4

A

1002-2279(2015)01-0005-02

任志伟(1983-)男,辽宁省凌源人,工学学士,助理工程师,主研方向:集成电路设计。

2014-07-10