填充辅助多晶硅图形的参数成品率版图优化

2015-07-11韩晓霞

韩晓霞,韩 雁

(浙江大学 微电子与光电子研究所,浙江 杭州310027)

在纳米工艺下,由于CMOS器件许多电学特性对特征尺寸的依赖,导致工艺波动对芯片功耗和性能带来显著影响,不同工艺批次下生产出来的芯片的功耗和时序性能变化非常大,严重影响到芯片的参数成品率[1-3].工艺波动引起的物理参数变化中最为重要的是线宽变化,尤其是多晶硅栅线宽,即MOS管的沟道长度.MOS管沟道长度是影响MOS管性能的主要参数,由于多晶硅线宽最小,最容易引起变化,由工艺波动引起的多晶硅宽度变化指的就是MOS管沟道长度的变化.MOS管沟道长度变化会影响MOS管的工作速度以及亚阈值电流,由此对电路时序和亚阈值电流引起的静态功耗产生影响,导致参数成品率下降[4-6].在纳米工艺中,参数成品率已成为影响芯片成品率的主要因素[7-10].

导致MOS管沟道长度发生变化的最主要原因是光刻时的曝光系统不理想.虽然采用分辨率增强技术(resolution enhancement techniques,RET),如:光学临近效应校正(optical proximity correction,OPC)、嵌入散射条(scattering bar insertion,SBI)、移相掩模(phase shift masks,PSM)和离轴照明(off axis illumination,OAI),能在一定程度上缓解由于曝光时的光学临近效应所引起的MOS管沟道长度变化[11-14],但RET 仅在假设一定的工艺条件(一定的聚焦误差和曝光剂量范围)下通过修改设计图形特征保证印制到硅片上图形的准确性.当工艺条件发生变化时,MOS管沟道长度变化反而会加剧.除此之外,掩模版错误、光刻胶厚度变化不均匀、曝光剂量变化、聚焦误差、透镜失常以及刻蚀过程中的微负载效益也会导致沟道长度发生变化[15].

MOS管沟道长度变化引起的参数成品率下降问题已经受到研究人员的高度关注[16-19].Orshansky等[20]发现由于曝光的光学临近效应使得不同疏密程度(即不同的多晶硅线间距)的多晶硅图形会导致MOS沟道长度产生不同变化,由此提出了一种考虑图形周围环境引起沟道长度变化的时序分析方法.Gupta等[21]针对由聚焦误差引起的沟道长度变化进行了分析,并对标准单元库中的每个逻辑单元建立了相应的沟道长度变化表,在此基础上实现的时序分析比采用传统的基于工艺角的时序分析更为精确,设计时需要设置的时序裕量可以减少40%.Kahng等[22]更进一步地通过分析研究由聚焦误差和多晶硅线间距共同作用引起的多晶硅线宽变化,提出了一种更为精确的亚阈值电流分析方法.但上述研究工作都仅以提高性能分析的准确度为目标,缺乏通过减小MOS管沟道长度的变化来优化电路性能的措施.

本文在对由聚焦误差和多晶硅线间距共同作用引起的多晶硅线宽变化(即MOS管沟道长度)的研究基础上,提出对现有版图填充辅助多晶硅图形的版图优化方法.填充的辅助多晶硅图形不影响现有版图的功能,辅助多晶硅图形的线宽和最小间距取决于掩模版制作要求,一般比工艺设计规则要求的最小多晶硅线宽和最小多晶硅线间距值更小.通过修改辅助多晶硅图形的特征属性,包括辅助多晶硅图形的多晶硅线宽、间距和条数,利用光刻仿真得到针对不同多晶硅特征图形的最优辅助多晶硅图形,最大程度地消除由聚焦误差引起的多晶硅线宽变化,由此构建一个查表模型.在现有版图基础上,针对位于标准单元边界处的MOS管,根据其周围的图形环境提取出多晶硅特征图形,并利用提取出的特征图形查找查表模型得到最优的辅助多晶硅图形,在不违反版图设计规则的前提下将最优的辅助多晶硅图形填充到两相邻的标准单元间.

1 多晶硅线宽变化的光刻仿真

利用美国北卡州立大学(North Carolina State University)提供的FreePDK45nm 工艺设计包搭建基于Mentor Graphics Calibre LFD 的光刻仿真平台[23].该光刻仿真平台采用分辨率为193nm 的光刻曝光系统,光刻仿真前,首先需要在正常聚焦情况下对版图进行OPC处理.

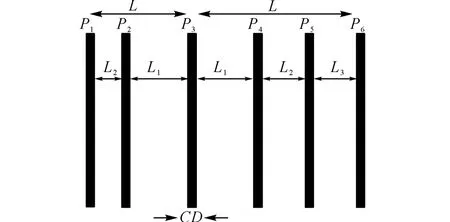

对由聚焦误差和多晶硅线间距共同作用引起的多晶硅线宽变化进行光刻仿真分析.FreePDK45nm 工艺下的多晶硅最小线宽为50nm,由此构建如图1(a)所示的3条线宽为50nm、间距为L 的多晶硅图形.图1(b)在图1(a)基础上增加了2条线宽为50nm 的辅助多晶硅,其与中间条多晶硅间距固定为L1.图中,CD 为所关注的中间条多晶硅线宽.

1.1 多晶硅线间距对多晶硅线宽的影响

在正常聚焦情况下,中间条多晶硅线宽CD 随着与其相邻的多晶硅条间距L 的不同而发生变化.Cao等[24]研究发现,在不同间距的多晶硅条间填充辅助多晶硅可以减小多晶硅线宽CD 受多晶硅间距L 的影响.

1.2 聚焦误差对多晶硅线宽变化的影响

图1 多晶硅图形Fig.1 Polysilicon pattern

填充辅助多晶硅后,相邻的多晶硅间距对多晶硅线宽变化的影响减小,更为重要的是,由于聚焦误差引起的多晶硅线宽变化得以明显改善.光刻仿真多晶硅线宽CD 在不同聚焦误差下的线宽变化情况如下:聚焦误差范围为-120~120nm,步长为20 nm.如图2所示分别为无辅助多晶硅和填充辅助多晶硅这2种情况下,多晶硅线宽CD 在不同聚焦误差下的线宽变化情况.从图2得到的仿真曲线中可知,填充辅助多晶硅后,50nm 线宽的多晶硅由于聚焦误差引起的线宽CD 的变化量△CD 从13.6nm减小到7.6nm.因此,填充辅助多晶硅对由聚焦误差引起的多晶硅线宽变化的改善非常明显.在填充辅助多晶硅时,L1越小越好,但L1有工艺设计规则要求,应满足所填充的辅助多晶硅与有源区的最小间距要求.FreePDK45nm 工艺下的要求是50nm,因此,选L1=50nm.

图2 聚焦误差对线宽变化的影响(L =520nm)Fig2 Effect of defocus on linewidth variety when Lis 520nm

2 填充辅助多晶硅图形的版图优化方法

2.1 辅助多晶硅图形的特征属性优化

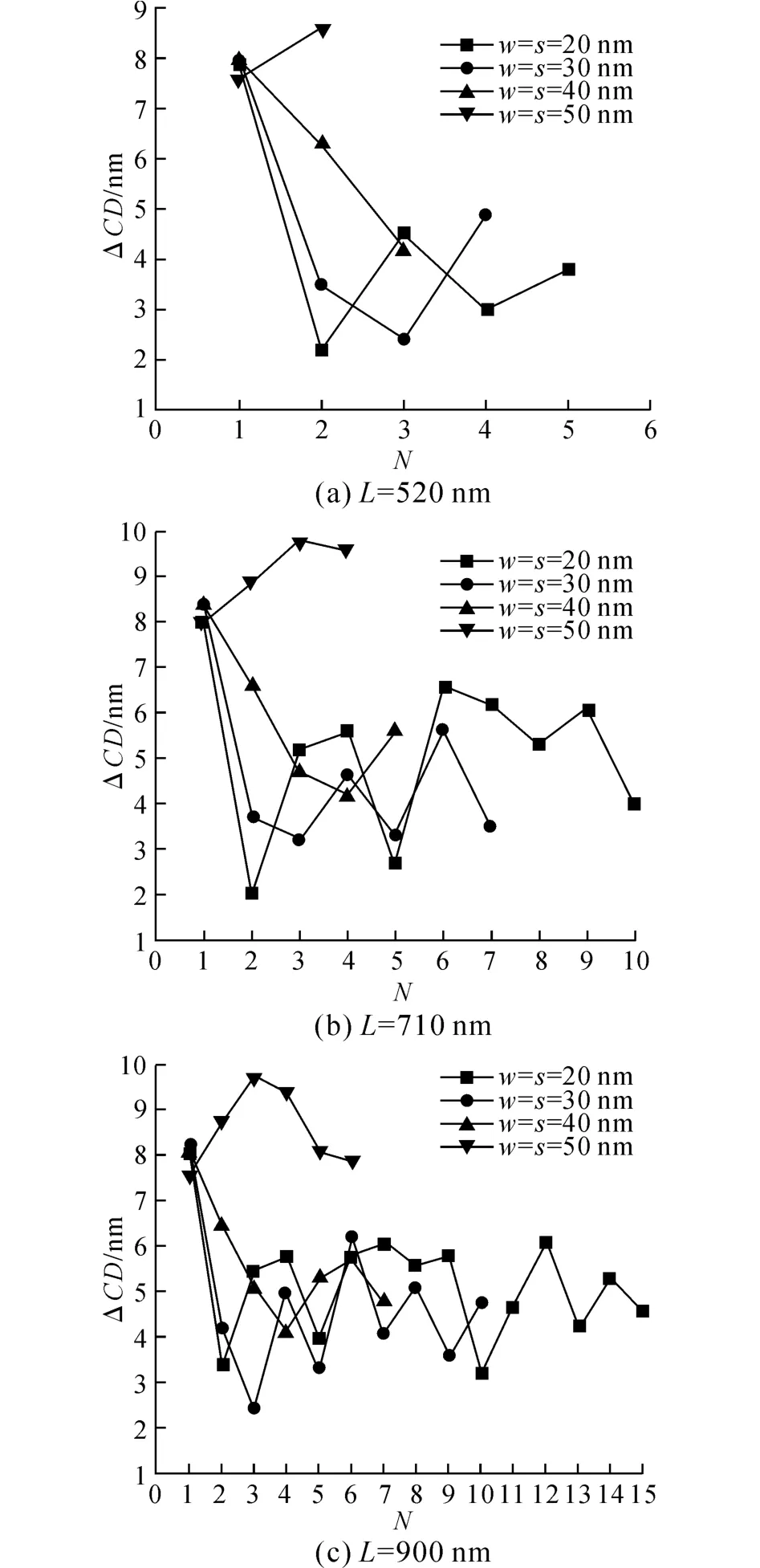

光刻仿真发现,填充的辅助多晶硅的不同特征属性包括间距、线宽和条数都会对由聚焦误差引起的MOS管沟道长度变化带来很大影响.如图3 所示,在间距为L 的3条多晶硅P1、P2、P3之间填充了2组相同的辅助多晶硅阵列M3.设N 为填充的辅助多晶硅阵列条数,W 为辅助多晶硅线宽,S 为辅助多晶硅阵列中的多晶硅间距.根据ITRS 2010年对45nm 工艺下掩模版的技术预测,掩模版上可制作的亚分辨率辅助图形的最小尺寸为81nm[25],因此,版图中可填充的辅助多晶硅的最小线宽为20 nm.如图4所示为光刻仿真后得到的由于聚焦误差引起的多晶硅线宽变化量△CD 与L、N、W 和S 的关系.当L=520nm 并填充2条W =S=20nm 的辅助多晶硅时,△CD 最小,为2.2nm;当L=520 nm 并填充2 条W =S=50nm 的辅助多晶硅时,△CD 最大,为8.6nm.当L=710nm 并填充2条W =S=20nm 的辅助多晶硅时△CD 最小,为2 nm;当L=710nm 并填充3条W =S=50nm 的辅助多晶硅时,△CD 最大,为9.7nm.当L=900nm并填充3条W =S=30nm 的辅助多晶硅时,△CD最小,为2.4nm;当L=900nm 并填充3条W=S=50nm 的辅助多晶硅时,△CD 最大,为9.6nm.因此,对辅助多晶硅图形进行特征属性优化可以明显改善多晶硅线宽随聚焦误差引起的波动变化.

图3 填充辅助多晶硅阵列的多晶硅图形Fig.3 Polysilicon pattern of filling dummy polysilicon line

2.2 辅助多晶硅图形查表模型构建

在基于标准单元的版图设计中,由于标准单元内的多晶硅条间距已固定,且间距比较小,多晶硅条比较密集,位于标准单元内的MOS 管由于聚焦误差导致的沟道长度的变化值比较小.相邻标准单元间的多晶硅条间距将随版图设计阶段中标准单元的不同布局而发生改变,且间距比较大,多晶硅条比较稀疏,因此,位于标准单元边界处的MOS管的沟道长度的变化取决于相邻标准单元间的多晶硅条间距,并且随聚集误差引起的变化要远大于位于标准单元内的MOS管.为了更好地抵抗工艺波动的影响,减小位于标准单元边界处的MOS管沟道长度随聚焦误差引起的变化,提出一种在现有版图基础上在两相邻标准单元间填充最优辅助多晶硅图形的版图优化方式.

图4 多晶硅线宽变化量与多晶硅线间距、辅助多晶硅线条数、辅助多晶硅线宽和辅助多晶硅线间距的关系曲线Fig.4 Width variation of polysilicon line impacted by polysilicon line-to-line space,number of dummy polysilicon lines,dummy polysilicon line width and line-to-line space

以基于FreePDK45nm 工艺设计包基础开发的用于研究的标准单元库Nangate 45nm 作为研究对象建立辅助多晶硅图形查表模型[23].

在分析Nangate45nm 标准单元库的基础上构建各种多晶硅特征图形.多晶硅线宽变化受影响的范围取决于光学临近效应的最大影响范围.文献[22]指出,当在90nm 工艺下采用193nm 曝光系统时,其光学临近效应影响范围的有效半径为600 nm,FreePDK45nm 工 艺 也 是 采 用193nm 曝 光 系统,因此选取700nm 为光学临近效应影响范围的有效半径,即超过700nm 距离的版图图形特征不会影响多晶硅线宽的变化.由于光学临近效应只受左右图形的影响,不受上下图形的影响,根据版图中可能出现的各种不同标准单元的组合,在所关注的多晶硅条的左右各700nm 处构建出多种组合的多晶硅特征图形.两标准单元完全相邻时位于相邻标准单元处的两多晶硅最小间距为290nm,位于标准单元内的多晶硅间距为140nm,选取步长为50 nm,由此构建如图5所示的多晶硅特征图形.实际版图中不同标准单元的各多晶硅图形都有所差异,并不是简单的多晶硅条,但多晶硅线宽都是50nm,对此进行简化选用50nm 线宽的多晶硅条进行多晶硅特征图形构建.图中,所关注的多晶硅条为P3,光学临近效应影响范围的有效半径L 为700nm,L1为290、340、390、440、490、540、590、640nm,L2为140、290nm,L3为140nm.因此,在构建多晶硅特征图形时,所关注的多晶硅一边没有多晶硅时为1种情况;一边有一条多晶硅时有8种组合,即L1的8种组合;一边存在两条多晶硅时有5种组合,分别是(L1,L2)为(290,140)、(290,290)、(340,140)(390,140)和(440,140);一边存在3条多晶硅时只有1种情况,即(L1,L2,L3)为(290,140,140)时.这样,总共有15种组合情况.由于区分左右两边,多晶硅特征图形数共有C215=105种组合.

针对这105种多晶硅特征图形,分别利用光刻仿真得到针对不同多晶硅特征图形的最优辅助多晶硅图形,由此构建辅助多晶硅图形查表模型.

图5 多晶硅特征图形Fig.5 Feature pattern of polysilicon

2.3 版图优化

利用构建的辅助多晶硅图形查表模型进行版图优化的流程如图6所示.在现有版图的基础上,先提取出各标准单元的位置信息,然后提取出位于标准单元边界处所关注的多晶硅条左右各700nm 处的多晶硅特征图形,再通过查找查表模型填充最优辅助多晶硅图形,得到优化后的版图.进行版图设计规则检查(design rule checking,DRC)时,可以忽略由于填充辅助多晶硅图形引入的多晶硅最小线宽和最小间距的伪错误.由于填充的辅助多晶硅图形位于标准单元之间,而标准单元间没有有源区存在,填充的辅助多晶硅图形不会形成MOS 管的栅,也不会产生寄生MOS管.该优化方法不会影响原有电路的功能,也不会对器件可靠性带来影响.

图6 版图优化流程Fig.6 Layout optimization flow

3 实验结果与数据分析

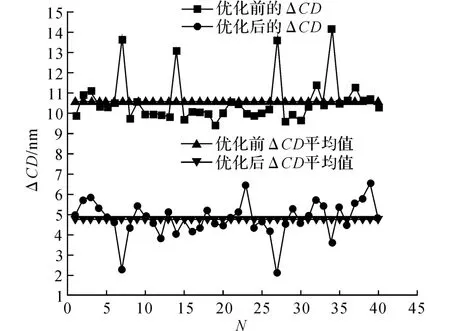

对测试电路进行光刻仿真以测试所提出的填充辅助多晶硅图形的版图优化方法.如图7所示为测试电路版图,图中只显示了版图的多晶硅层、有源区层以及标准单元外框.如图8所示为在相邻标准单元间填充最优辅助多晶硅图形后的优化版图.如图9所示为位于标准单元边界的各MOS 管的多晶硅线宽变化量△CD 在优化前后的变化,△CD 的平均值从10.58nm 优化为4.79nm.位于标准单元内部的各MOS管的多晶硅线宽变化量△CD 如图10所示,版图优化前,位于标准单元内部的各MOS管的多晶硅线宽变化量△CD 的平均值为7.85nm,版图优化后△CD 的平均值为7.83nm,因此,位于标准单元内部的MOS管的多晶硅线宽变化基本不受版图优化的影响.结果表明:填充最优辅助多晶硅后,在不影响位于标准单元内的MOS 管的多晶硅线宽变化前提下,位于标准单元边界的MOS 管的多晶硅线宽变化量△CD 从版图优化前的10.58nm降低至4.79nm..因此,该版图优化方法对抵抗由聚焦误差引起的MOS管沟道长度变化有显著的改善作用.

图7 测试电路版图Fig.7 Layout for test circuit

图8 优化后的版图(填充辅助多晶硅)Fig.8 Optimized layout with filling dummy polysilicon

图9 位于标准单元边界的各MOS管的多晶硅线宽变化量Fig 9 Linewidth variation for each MOS transistor located at boundary of standard cells

图10 位于标准单元内的各MOS管的多晶硅线宽变化量Fig.10 Linewidth variation for each MOS transistor located in standard cells

4 结 语

本文提出了一种在现有版图基础上填充辅助多晶硅图形以提高参数成品率的版图优化方法.利用光学临近效应,通过在标准单元间填充辅助多晶硅图形来减少位于标准单元边界处的MOS管的多晶硅线宽变化.填充的辅助多晶硅图形是通过光刻仿真后得到的能使MOS管沟道长度在不同聚焦误差情况下变化最小的特征图形,因此,填充辅助多晶硅图形后的版图对抵抗由聚焦误差引起的MOS管沟道长度变化有显著的改善作用.由于光学临近效应有一定的影响范围,该优化方法对填充辅助多晶硅处相距较远的位于标准单元内的MOS管的多晶硅线宽没有影响.测试电路的光刻仿真验证表明:使用所提出的版图优化方法,在不影响位于标准单元内的MOS管的多晶硅线宽变化前提下,位于标准单元边界的MOS 管的多晶硅线宽从版图优化前的10.58nm 降低至4.79nm..

(

):

[1]RAMAKRISHNAN H,SHEDABALE S,RUSSELL G,et al.Analysing the effect of process variation to reduce parametric yield loss[C]∥IEEE International Conference on Integrated Circuit Design and Technology and Tutorial.Austin:IEEE,2008:171-176.

[2]BAKER A M,WANG L,JIANG Y.High level circuit synthesis with system level statistical static timing analysis under process variation[C]∥IEEE 56th Interna-tional Midwest Symposium on Circuits and Systems.Columbus:IEEE,2013:817-820.

[3]MIRANDA M,FIERICKX B,ZUBER P,et al.Variability aware modeling of SoCs:from device variations to manufactured system yield[C]∥Quality of Electronic Design.San Jose:ISQED,2009:547-553.

[4]MULLER J,JALLEPALLI S,MOORAKA R,et al.Employing an on-die test chip for maximizing parametric yields of 28nm parts[C]∥International Conference on Microelectronic Test Structures,Tempe:ICMTS,2015:50-53.

[5]BYUNG S K,BYOUNG H L,HUNG_BOK C,et al.Parametric yield-aware sign-off flow in 65/45nm[C]∥SoC Design Conference(ISOCC).Busan:ISOCC,2008:74-77.

[6]BORKAR S,KAMIK T,NARENDRA S,et al.Parameter variations and impact on circuits and microarchitecture[C]∥Proceedings of ACM/IEEE Design Automation Conference.Anaheim:ACM/IEEE,2003:338-342.

[7]UKHOV I,ELES P,PENG Z.Probabilistic analysis of power and temperature under process variation for electronic system design[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2014,33(6):931-944.

[8]BASU S,THAKORE P,VEMURI R.Process variation tolerant standard cell library development using reduced dimension statistical modeling and optimization techniques[C]∥8th International Symposium on Quality Electronic Design.San Jose:ISQED,2007:814-820.

[9]BHUNIA S,MUKHOPADHYAY S,ROY K.Process variations and process-tolerant design[C]∥20th International Conference on VLSI Design.Bangalore:VLSI DESIGN,2007:699-704.

[10]DUTT S,CHAUHAN A,NANDI S,et al.Variability-aware parametric yield enhancement via post-silicon tuning of hybrid redundant MAC units[C]∥2015International Symposium on VLSI Design,Automation and Test(VLSI-DAT).Hsinchu:VLSI-DAT,2015:1-4.

[11]POOMIMA P,TRIPATHY S K,RAO R,et al.Resolution enhancement techniques for optical lithography[C]∥Proceedings of SPIE-The International Society for Optical Engineering.Washington:SPIE,2002:1260-1262.

[12]CHANDRACHOLLD M,LEUNG T Y B,YU K,et al.Overcoming mask etch challenges for 45nm and beyond[C]∥Mask and Lithography Conference(EMLC),European.Dresden:EMLC,2008:1-10.

[13]CHAN S H,LAM E Y.Inverse image problem of designing phase shifting masks in optical lithography[C]∥15th IEEE International Conference on Image Processing,ICIP 2008.San Diego:IEEE,2008:1832-1835.

[14]PENG Y,SHI S X,PAN D Z.Process variation aware OPC with variational lithography modeling[C]∥Proceedings of ACM/IEEE Design Automation Conference.San Francisco:ACM/IEEE,2006:785-790.

[15]BOMA A,PROGLER C,BLAAUW D.Correlation analysis of CD-variation and circuit performance under multiple sources of variability [C]∥Proceedings of SPIE-the International Society for Optical Engineering.Bellingham:SPIE,2005:168-177.

[16]MOHSEN R,JACK S.A yield improvement technique in severe process,voltage,and temperature variations and extreme voltage scaling[J].Microelectronics Reliability.2014,54(12):2813-2823.

[17]MIRZAEI M, MOSAFFA M, MOHAMMADI S.Variation-aware approaches with power improvement in digital circuits [J].Integration,the VLSI Journal.2015,48(1):83-100.

[18]SALEHUDDIN F,AHMAD I,HAMID F A,et al.Optimization of input process parameters variation on threshold voltage in 45nm NMOS device[J].International Journal of Physical Sciences,2011,6(30):7026-7034.

[19]BEECE D K,JINJUN XIONG,VISWESWARIAH C,et al.Transistor sizing of custom high-performance digital circuits with parametric yield considerations[C]∥Proceedings of ACM/IEEE Design Automation Con-ference (DAC). Anaheim: ACM/IEEE, 2010:781-786.

[20]ORSHANSKY M,MILOR L,CHEN P,et al.Impact of spatial intrachip gate length variability on the performance of high-speed digital circuits [J].IEEE Transactions On Computer-Aided Design of Integrated Circuits and Systems,2002,21(5):544-553.

[21]GUPTA P,HENG F L.Toward a systematic-varation aware timing methodology[C]∥Proceedings of the 41st annual Design Automation Conference.San Diego:ACM,2004:321-326.

[22]KAHNG A,MUDDU S,SHARMA P.Defocus-aware leakage estimation and control[J].IEEE Transaction On Computed-Aided Design of Integrated Circuits and Systems.2008,27(2):130-140.

[23]KNUDSEN J,MARKERING VP.Nangate 45nm open cell library[EB/OL].(2008-04-16)[2015-11-10].http:∥www.si2.org/events_dir/2008/oacspring2008/nan.pdf.

[24]CAO K,DOBRE S,HU J.Standard cell characterization considering lithography induced variations[C]∥Design Automation Conference,43rd ACM/IEEE.San Francisco:ACM/IEEE,2006:801-804.

[25]2010Tables_FEP_FOCUS_C_ITRS[EB/OL].(2010-12-20)[2015-11-10].http:∥www.itrs.net/ITRS%201999-2014% 20Mtgs,% 20Presentations% 20&%20Links/2010ITRS/2010Update/ToPost/2010Tables_FEP_FOCUS_C_ITRS.xls