基于北斗的高速摄像机时间同步器设计※

2015-07-03邸兴张杰

邸兴,张杰

(中国飞行试验研究院,西安 710089 )

基于北斗的高速摄像机时间同步器设计※

邸兴,张杰

(中国飞行试验研究院,西安 710089 )

为了满足民用飞机在飞行试验中高速摄像机对时间同步的需求,基于国产北斗卫星导航系统设计了具有精确输出IRIG-B(AC)码的时间同步器,用于机载高速摄像机的精确时间同步。以FPGA为核心,使用直接数字频率合成技术实现了IRIG-B(AC)码的产生。实验结果表明,该同步器时间同步精度满足要求,可以实现对高速摄像机进行时间同步的功能。

北斗卫星系统;FPGA;直接数字频率合成;时间同步

引 言

在民用飞机飞行试验中,为了保证图像测试数据准确可靠,机上图像测试系统中不同测试设备的时间需要严格统一。原子钟是一种非常稳定的时钟源,可以提供精确的时间信息用于时间同步,但是在机载环境下,由于安装空间狭小,安装位置受限,无法使用原子钟作为时钟源。

使用导航卫星对机载高速摄像机进行时间同步,可以满足图像测试系统对时间同步的精度要求。随着我国北斗二代卫星导航系统一期组网完成和接口控制文件的公布,北斗卫星导航系统开始向亚太大部分地区正式提供连续无源定位、导航、授时等服务。本文使用北斗卫星导航系统,设计了机载高速摄像机时间同步器。

1 时间同步技术方案

目前,绝大多数机载高速摄像机外部同步时间输入都支持IRIG-B码[1],时间同步器接收北斗卫星时间信息,将卫星发送的UTC时间编码转换为IRIG-B时间码需要的格式,并产生IRIG-B时间码的波形输出,IRIG-B时间码的起始位置必须和整秒的起始位置严格对齐。时间同步器内部结构如图1所示。

图1 时间同步器内部结构

UM220-T接收北斗二代卫星时间信息,将时间信息以NMEA-0183语句输出至STM32微控制器,STM32微控制器解码UTC时间,并将其编码为IRIG-B需要的时间信息,通过串行总线输入FPGA中,同时STM32微控制器通过SPI接口控制OLED显示屏,实时显示当前定位状态和时间信息。FPGA将接收的时间信息编码为IRIG-B(DC)码和IRIG-B(AC)码输出,由于FPGA输出的IRIG-B(AC)码实际上为数字信号,需要通过高速D/A转换器以及运放信号调理来实现将数字IRIG-B(AC)码转换成模拟信号,用于机载高速摄像机时间同步。

1.1 UM220-T北斗卫星接收模块

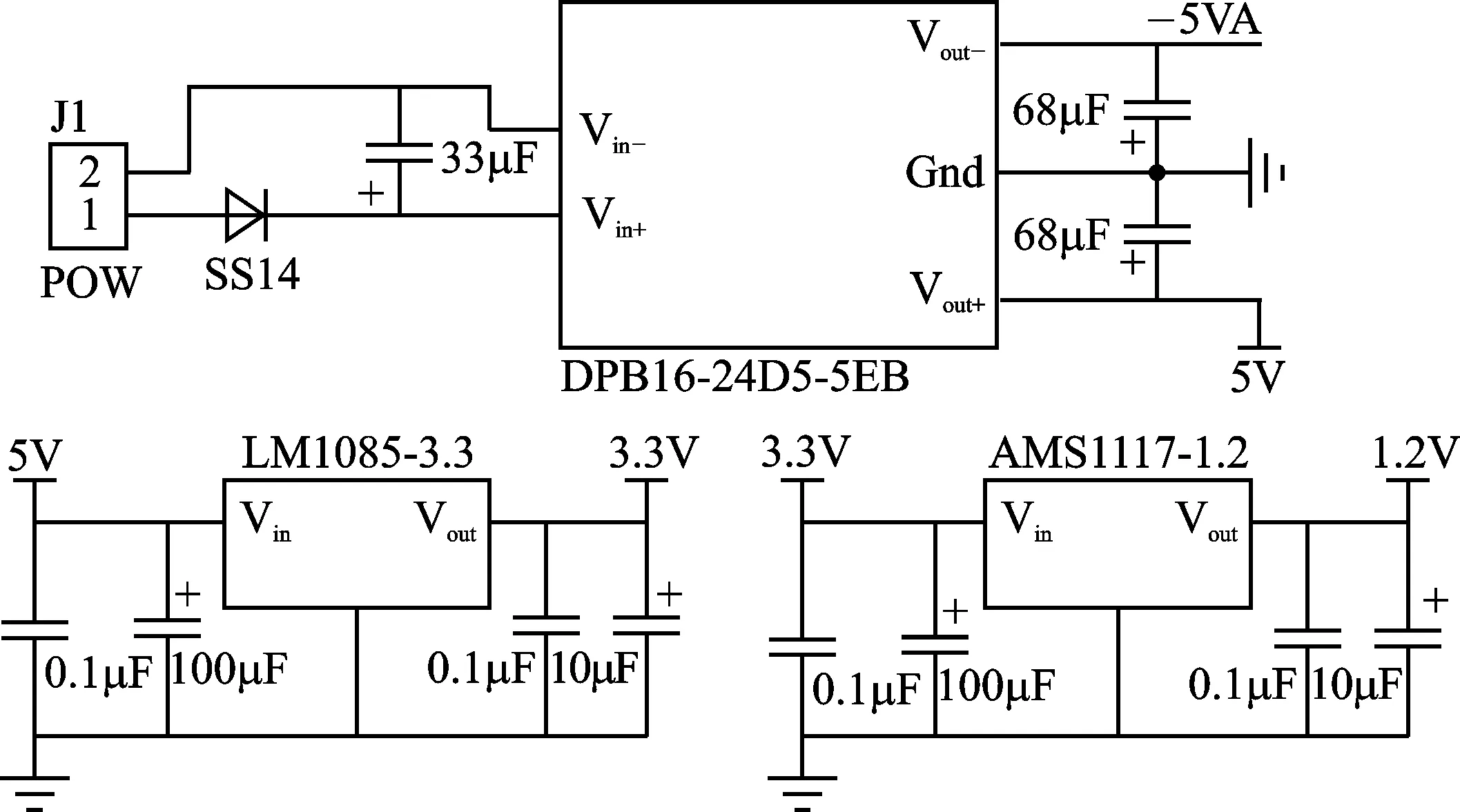

图2 电源供电部分电路

UM220-T模块是针对授时应用领域推出的北斗/GPS双系统精密授时产品,支持静态授时、单星授时,集成度高、功耗低,适合北斗授时领域的应用;采用先进的多路径抑制技术,以及优化的授时算法,提供精确的1 PPS输出。创新的多系统融合开放式架构,保证不同系统的可用卫星均可参与联合定位、授时,保障长时间连续可靠的授时输出。支持单星授时功能,在仅有一颗可见卫星时,仍能保持精确、稳定的 1 PPS输出。

1.2 STM32微控制器

本设计使用ARM Cortex-M3内核的STM32F103RB,具有扩展工业级的工作温度范围,主频可达72 MHz。

方案中使用STM32F103RB微控制器完成接收UM220-T发送的时间信息[2],从中解码出当前UTC时间,将其转换为标准的IRIG-B时间后通过自定义串行输出口输出至FPGA。同时,STM32F103RB微控制器还负责驱动OLED显示屏,实时显示当前的定位状态和时间信息,方案设计中还增加了实时时钟芯片(RTC),以便于在收星条件不好时,为测试系统提供一个参考时间。

1.3 FPGA芯片实现IRIG-B编码

当前,绝大多数机载高速摄像机都支持使用IRIG-B进行时间同步,IRIG是美国靶场仪器组的简称。IRIG时间标准有两大类:一类是并行时间码格式,这类码由于是并行格式,传输距离较近,且是二进制,因此远不如串行格式广泛;另一类是串行时间码,共有6种格式,即A、B、D、E、G、H。它们的主要差别是时间码的帧速率不同,IRIG-B为其中的B型码,B型码的时帧速率为1 F/s。北斗时间同步器设计中使用FPGA直接数字频率合成技术实现时间信息的IRIG-B码型产生。

2 时间同步器设计

2.1 硬件电路设计

2.1.1 供电部分电路

同步器内部设计中,UM220-T、STM32F103RB、RTC供电电压为3.3 V,FPGA的I/O供电电压为3.3 V,FPGA内核以及PLL供电电压为1.2 V,高速D/A运放供电为±5 V,机上电源提供28 V供电,故需要将28 V电压转换为各个部分需要的电压。设计中采用北京新雷能科技有限公司生产的DPB16-24D5-5EB电源,它具有18~36 V的宽范围输入电压,输出±5 V。通过LM1085-3.3的LDO芯片,将5 V电压降压得到3.3 V电压,此芯片最大电流支持到3 A。再通过AMS1117-1.2获取1.2 V电压,由于1.2 V是FPGA内核的工作电压,以及FPGA内部PLL的工作电压,因此对1.2 V电压的纯净程度要求比较高。需采用钽电容滤波,设计中电源输入部分还加入了SS14二极管反接保护电路。电源供电部分电路如图2所示。

2.1.2 FPGA编码部分电路

FPGA使用EP2C5T144I8,主要实现IRIG-B时间同步码的编码工作,STM32F103RB将解码到的时间信息编码成天、时、分、秒的8 421码,在数据有效脉冲的使能下将数据送入FPGA,FPGA精确检测秒脉冲(PPS)的上升沿,在秒脉冲的上升沿开始一整秒B码时间数据的发送。本设计中FPGA将输出的数据编码为12位的并行数字信号,需要使用D/A信号调理将并行的数字信号转换成模拟信号[3]。本设计中选用美信公司的MAX7541,它具有0.6 μs的转换时间和12位的分辨率。MAX7541输出数据经运放信号调理和阻抗变换后产生标准的IRIG-B(AC)码。

IRIG-B(AC)码实际上是用IRIG-B(DC)码对标准正弦波载频进行幅度调制,标准正弦波载频的频率与码元速率严格相关,一般为码元速率的10倍。B码的标准正弦波载频频率为1 kHz。同时,其正交过零点与所调制格式码元的前沿相符合,标准的调制比为10:3。

正弦波是FPGA产生的[4-5],利用Quartus自带的LMP模块来进行ROM建模,存储了256个点的SIN函数的波形值。首先计算256个SIN函数的值,由于点数比较多,利用MATLAB工具产生一个完整周期SIN函数的256个点的值。考虑到FPGA处理整数相对简单,所以需要对SIN函数值进行整数化。

2.1.3 STM32编解码显示电路

STM32解码UM220-T输出的NMEA-0183语句,从中解算出当前的UTC时间,将其编码后送入FPGA。STM32通过I2C接口与RTC时钟芯片SD2400通信,提供当无法接收卫星时间时的参考时间输出。

OLED作为下一代显示技术,由于其显示屏为全固态器件,因此具有高低温范围宽、抗震特性好的特点。本设计中采用并行接口驱动OLED显示,完成时间、定位状态的显示功能。OLED显示驱动电路略——编者注。

2.2 软件程序设计

2.2.1 NMEA-0183解码

NMEA-0183是美国国家海洋电子协会(National Marine Electronics Association)为海用电子设备制定的标准格式。目前已成为GPS导航设备统一的 RTCM(Radio Technical Commission for Maritime services)标准协议。

NMEA-0183常用命令如表1所列。

表1 NMEA-0183常用命令

每条语句都有固定的格式,输出的各个参数之间使用逗号隔开。UM220-T北斗卫星接收模块也使用这些标准语句进行导航数据的输出。本设计主要用于时间同步,因此仅需要对GPRMC语句中的定位状态和时间信息进行解码。

STM32F103RB先在内存中开辟两块缓冲区A和B,使用中断模式接收UM220-T发送的数据。当接收到$符号时表示数据帧开始,接下来将数据存入内存中开辟的数据缓冲区A中;当接收到回车换行符时表示一条数据帧接收完成,置位A区数据完成标志位,等待下一帧数据到来时采用同样的方式存入数据缓冲区B。

当主程序检测到缓冲区接收完成标志位置位时,从缓冲区中取出数据,完成数据解码[6],解算出当前UTC时间,清空数据缓冲区和标志位,将时间信息编码成串行数据送入FPGA中(编码时需要注意闰年B码天数的处理)。主程序实现的流程图如图3所示。

图3 主程序流程图

2.2.2 FPGA实现IRIG-B时间码

IRIG-B码是每秒一帧的时间串码,每个码元宽度为10 ms,一个时帧周期包括100个码元,为脉宽编码。码元的“准时”参考点是其脉冲前沿,每一帧的参考标志由一个位置识别标志和相邻的参考码元组成,其宽度为8 ms。每10个码元有一个位置识别标志:P1、P2、P3、…、P9、P0,它们均为8 ms宽度。二进制“1”和“0”的脉宽为5 ms和2 ms。

使用Verilog语言进行编码逻辑的设计,首先根据STM32F103RB输出的时间,产生相应的IRIG-B(DC)码,再使用DC码调制正弦载波,产生AC码信号,通过运放调理电路实现对D/A输出信号的低通滤波以及分配为多路的功能。

3 实验结果与应用

为了验证北斗时间同步器的精度,课题组将其输出的波形与中国科学院国家授时中心的标准时码发生器进行了对比实验。实验结果表明,北斗时间同步器的同步精度能满足设计要求。对比实验结果如图4所示。

图4 与标准时码发生器时序对比

课题组将北斗时间同步器用于机载高速摄像机和模拟视频采集记录器进行时间同步,结果表明北斗时间同步器输出的IRIG-B(AC)码可以实现对机载高速摄像机的时间同步功能,同步时间精度小于10 μs。

结 语

利用我国自主知识产权的北斗卫星导航系统,使用基于FPGA的数字频率合成技术设计了北斗卫星时间同步器,实现了对机载高速摄像机进行精确的时间同步,并将其应用于飞行试验中,为飞行试验高速摄像机时间同步提供了一种新的方式,具有较好的应用前景。

[1] 邴志光,束坤,顾燕飞.IRIG-B码在时间同步系统中的应用[J].现代电子技术,2012,35(7):16-18.

[2] STMicroelectronics.STM32 Reference Manual RM0008[EB/OL].http://www.stmicroelectronics.com.cn/stonline/stappl/resourceSelector/app?page=fullResource Selector& doctype=reference_manual&SeriesID=1031.

[3] 杨秀增.基于AD7543和FPGA的数/模转换电路设计[J].现代电子技术,2009, 32(9):31-33.

[4] 陈亮,张炜.基于FPGA的多功能信号源生成系统设计与实现[J].现代电子技术,2009,32(6):34-37.

[5] 杨东霞,巨永锋.基于FPGA和DDS的数字调制信号发生器设计与实现[J].电子设计工程,2013,21(6):90-93.

[6] 钟鼎,尹媛媛.基于STM32人流量统计监控系统设计[J].电子设计工程,2011,19(20):94-96.

邸兴(硕士),研究方向为光电测试技术。

Di Xing, Zhang Jie

(Chinese Flight Test Establishment, Xi’an 710089, China)

In order to meet the high speed camera of civil aircraft requirement of time synchronization in the flight test, the time synchronizer with accurate output IRIG-B(AC) code is designed based on Beidou satellite navigation system,which is used for precise time synchronization of airborne high speed camera.Taking FPGA as the core, the IRIG-B (AC) code can be generated using the direct digital frequency synthesis technology.The results of experiment show that the time synchronizer can satisfy the requirement of accuracy,and it can realize the time synchronization of high speed camera.

Beidou satellite system;FPGA;direct digital frequency synthesis;time synchronization

TP23

A

士然

2014-07-24)