基于ADF4350与AD9913的跳频频率合成器设计

2015-06-23胡丽格

胡丽格

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

基于ADF4350与AD9913的跳频频率合成器设计

胡丽格

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

很多系统对频率合成器的频率捷变性能和相位噪声特性提出了越来越高的要求。介绍了基于锁相环ADF4350与DDSAD9913的跳频频率合成器的设计与实现方法。通过对跳频理论与锁相环技术理论研究,以及对ADF4350锁相环内部结构进行分析,设计了基于ADF4350与AD9913的900~4 000 MHz跳频频率合成器。测试结果表明,输出信号相位噪声优于-86 dBc/Hz@10 kHz,频率步进0.76 Hz,频率转换时间优于175μs,频率合成器性能良好。

频率合成;直接数字频率合成;锁相环;跳频

0 引言

频率合成技术作为现代电子系统中一项极为重要的技术,对现代通信、雷达、卫星和电子对抗都具有相当重要的作用。特别是在抗干扰通信和雷达电子系统中,跳频频率合成技术更是成为关键技术之一,倍受各国电子系统设计师们的青睐。

频率合成技术是将1个(或多个)基准频率信号变换为另1个(或多个)所需频率信号的技术。频率合成分3类:直接频率合成(DS-Direct Synthe-sis)、间接频率合成(Indirect Frequency Synthesis)和直接数字频率合成(DDS-Direct Digital Frequency Synthesis)。其中,间接频率合成又称锁相频率合成是应用锁相环(Phase Locked Loop,PLL)的频率合成方法。

以上3种频率合成技术各有优缺点,目前频率合成的发展趋势是将DS、PLL、DDS、混频和倍频等技术合理组合使用,使得频率合成器的相位噪声、杂散、频率范围以及跳频时间等技术指标大大提高。本文提出了一种全新的PLL+DDS+混频的跳频频率合成器的设计与实现,该频率合成器具备低相位噪声、小步进和快速跳频的性能,同时体积小、功耗低[1-3]。

1 锁相环的相位噪声及跳频时间分析

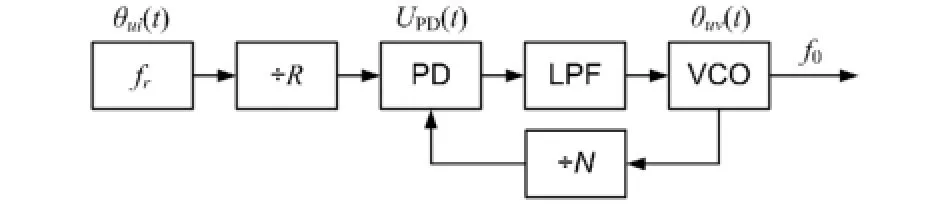

由于锁相频率合成十分有利于集成化和小型化,目前在电子领域中应用十分广泛。在线性近似下,运用线性分析方法,可求得环路对各类噪声与干扰的总过滤特性。为方便分析,设基本环路存在着3个主要噪声源,标出噪声与干扰的环路线性相位模型如图1所示。

图1中,θui(t)为输入白高斯噪声形成的等效输入相位噪声;UPD(t)为输出谐波或鉴相器本身的输出相位噪声电压;θuv(t)为压控振荡器内部噪声形成的相位噪声。

图1 环路线性相位模型

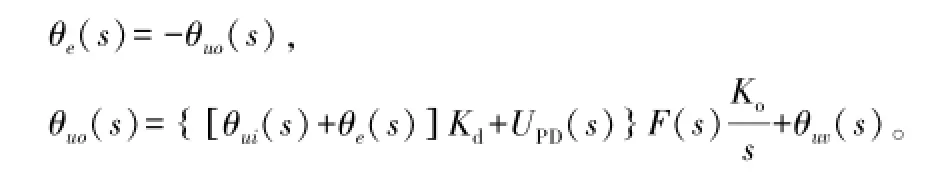

运用线性分析方法,设输入信号相位θ1(t)=0,可得环路方程:

经合并运算后,可得环路总输出相位噪声为:

若设Sθui(F)为θui(t)的相位噪声功率谱密度,SUPD(F)为UPD(t)的电压噪声功率谱密度,Sθuv(F)为θuv(t)的相位噪声功率谱密度,则环路输出的总相位噪声功率谱密度Sθuo(F)为:

2 ADF4350芯片

ADF4350是ADI公司推出的一款集成压控振荡器(VCO)的宽带频率合成器芯片。芯片内部集成R分频器、小数N分频器、鉴相器、宽带VCO、内部/1/2/4/8/16分频器等电路。只需外配环路滤波器和参考基准源,即可构成一个完整的锁相环。ADF4350内部集成的VCO输出基波频率为2 200~4 400 MHz,利用内部/1/2/4/8/16分频电路可使输出频率最低拓展至137.5 MHz。所有内部寄存器均可通过三线进行控制。

与其他锁相环相比,ADF4350具备快速锁定功能。首先,VCO具备分段预置功能。ADF4350的VCO内核由3个独立的VCO组成,每个VCO使用16个重叠频段。VCO既具备较低的压控灵敏度(Kv),以保证低相位噪声输出,同时,又可以覆盖较宽的频率范围。上电或寄存器更新时,VCO的频段选择逻辑会自动选择正确的频段,实现频率预置功能,频率预置最快可达80μs。其次,锁相环内部增加了快速锁定模式。使用快速锁定模式时,电荷泵电流增大16倍,以保证在较宽的环路带宽下环路锁定。锁定后电荷泵电流恢复正常,环路带宽恢复正常。基于ADF4350的以上功能设计跳频频率合成器[8-10]。

3 跳频频率合成器的设计

跳频频率合成器的技术指标要求如下:

①输出频率范围:900~4 000MHz;

②相位噪声:≤-65 dBc/Hz@100 Hz;

≤-75 dBc/Hz@1 kHz;

≤-85 dBc/Hz@10 kHz;

≤-95 dBc/Hz@100 kHz;

③频率步进:100 Hz;

④跳频时间:<200μs;

⑤参考输入:10MHz。

3.1 频率合成器实现原理

锁相环输出的相位噪声与频率步进是一对矛盾。为了获得较小的频率步进,需要较低的鉴相频率。但较低的鉴相频率,会带来相位噪声的恶化。在设计时,通常先考虑满足相位噪声的要求,再通过其他方法来实现较小的频率步进。当参考输入为10 MHz时,假定取10 MHz为鉴相频率。通过ADIsimPLL软件仿真,当输出频率为4 000 MHz,环路带宽取30 kHz时,相位噪声为:-74 dBc/Hz@100 Hz;≤-87 dBc/Hz@1 kHz;≤-87 dBc/Hz@10 kHz;≤-101 dBc/Hz@100 kHz,满足指标要求。当鉴相频率大于10 MHz时,环路带宽内输出的相位噪声将更低。

当鉴相频率为10 MHz时,取ADF4350的MOD为最大值4 095,可得最小频率步进约为2.44 kHz,不满足步进100 Hz的指标要求。为了实现较小的频率步进,可采用DDS激励锁相环的方法来实现,跳频频率全盛器原理如图2所示。

图2 跳频频率合成器原理

DDS芯片选取ADI公司的AD9913,这款芯片体积小、功耗低。10 MHz参考信号作为AD9913的时钟信号。通过频率控制,使AD9913输出2.25 MHz。2.25 MHz信号与10 MHz参考信号混频产生12.25 MHz信号,并经过滤波器滤除带外杂散。滤波后的12.25 MHz信号作为ADF4350的参考信号,再通过ADF4350输出900~4 000MHz的射频信号。通过AD9913产生极小的频率步进激励锁相环,可使锁相环输出较小的频率步进。以10 MHz为时钟的AD9913芯片,输出最小频率分辨率约为0.002 3 Hz。通过锁相环的倍频作用,射频输出4 000 MHz时,最小频率步进约为0.76 Hz,满足指标要求的100 Hz步进。

跳频时间取决于AD9913的换频时间和ADF4350的锁定时间。通常AD9913的换频时间远小于ADF4350的锁定时间,可以忽略不计。ADF4350的锁定时间由2部分组成:VCO的预置时间和锁相环的快速锁定时间。VCO的预置时间取最快80μs。若环路带宽取30 kHz,通过ADIsimPLL仿真,启用快速锁定功能时,锁定时间为90μs。预置时间和锁定时间之和为170μs,即ADF4350的锁定时间,满足小于200μs的指标要求[11-14]。

3.2 测试结果及分析

根据图2制作的跳频频率合成器,实测结果如下:输出频率为4 000 MHz;跳频时间为175μs;频率步进为0.76 Hz;相位噪声实测结果如表1所示。

表1 实测结果

从以上测试结果可知,在频偏100 Hz和1 kHz时,相位噪声的实测结果与仿真结果相比,相差最大约7 dB。仿真数据是理想情况下得出的结果,未考虑外部电路对其影响。而实测数据则是在实际电路中测得的结果,受多种外部干扰的影响,其中电源低频噪声对其影响最大。电源低频噪声的叠加造成频率合成器近端相位噪声变差。可通过在电源上增加低通滤波器,滤除低频噪声,减小其对频率合成器的影响,但通常会增加电路模块的体积。频偏10 kHz和100 kHz时,相位噪声的实测结果与仿真结果相吻合。跳频时间是频率合成器由900 MHz跳至4 000 MHz的时间,测试结果与仿真结果基本一致。频率步进与计算结果一致。

4 结束语

本文提供了一种基于ADF4350和AD9913的跳频频率合成器的设计方案。在此方案的基础上,可由多个跳频频率合成器并联,再外加开关切换,实现更高跳速的跳频频率合成器。此频率合成器的研制成功,为今后实现更高跳速的频率合成器打下基础。

[1] 张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,1994:69-71.

[2] 姚剑清.锁相环技术[M].北京:人民邮电出版社,2007:152-172.

[3] 孔 京,郭黎利,战兴文.直接数字频率合成技术在跳频通信中的应用[J].应用科技,2001,28(9):13-15.

[4] 周炳利,许波强,王从道.一种高速跳频频率合成器的实现[J].电子科技,2013,26(8):88-89.

[5] 杨 光.低相噪快跳频率合成器[D].成都:电子科技大学,2007:17-23.

[6] 崔小明.基于DDS高速跳频源的研制[D].西安:西安电子科技大学,2012:31-54.

[7] 魏福立,张华鹏.具有快速锁定时间的新型低相噪频率合成技术[J].半导体技术,2006,31(5):321-324.

[8] 薛 军,潘高峰,谢 勇.基于ADF4350的多频段信号源的设计与实现[J].无线电工程,2011,41(11):53-55.

[9] 徐述武,汪海勇,唐云峰.基于ADF4350锁相频率合成器的频率源设计与实现[J].电子器件,2010,33(6):725-729.

[10] 单月忠,刘太君,叶 焱,等.基于ADF4351的频率源设计与实现[J].无线电通信技术,2014,40(6):85-88.

[11]付钱华.X波段捷变频雷达目标模拟器频率源研制[D].成都:电子科技大学,2005:34-53.

[12] 袁 文.高分辨率低杂散频综的研制[D].成都:电子科技大学,2004:30-39.

[13] 陈宝林.小型化频率综合器技术分析[J].无线电通信技术,2013,39(3):67-68,96.

[14] 吴永洪.低杂散、捷变频频率合成技术研究[D].成都:电子科技大学,2005:25-40.

Design of Frequency Hopping Synthesizer Based on ADF4350 and AD9913

HU Lige

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

Many systems require that the frequency synthesizer provide high performance in frequency agility and low phase noise characteristics.A design and implementation of frequency hopping synthesizer based on ADF4350 and AD9913 is presented.Based on studying the theory of frequency hopping and phase locked loop,and analyzing the internal structure of ADF4350,a design of frequency hopping synthesizer ranging from 900MHz to 4 000MHz is realized combingwith AD9913.Testing results show that the phase noise is lower than-86 dBc/Hz@10 kHz,frequency hopping step is 0.76 Hz,andfrequency conversion time is 175μs,which provides a good performance and meets the requirement.

frequency synthesis;direct digital frequency synthesis;phase locked loop;frequency hopping

TN74

A

1003-3106(2015)09-0065-03

10.3969/j.issn.1003-3106.2015.09.17

胡丽格.基于ADF4350与AD9913的跳频频率合成器设计[J].无线电工程,2015,45(9):65-67.

胡丽格女,(1975—),高级工程师。主要研究方向:卫星通信、频率合成。

2015-06-15