基于FPGA的狄克型辐射计数据采集系统设计

2015-06-08蔡朋飞

蔡朋飞,赵 飞

(中国科学院空间科学与应用研究中心微波遥感技术重点实验室 北京 100190)

随着微波遥感的日益广泛应用,对辐射测量技术也提出了越来越高的要求,目前国内使用的微波辐射计大多是全功率型辐射计,这种辐射计具有较高的理论灵敏度,结构也比较简单,但由于接收机增益的波动,其实际灵敏度及工作稳定性都比较差,而狄克型辐射计则克服了增益波动带来的不良影响,提高了辐射计的实际灵敏度和测量精度[1]。

目前传统狄克型辐射计的各项技术已经比较成熟,它通过调制,同步解调和积分器实现零平衡进而抑制增益变化,然而它们的实现都是通过模拟电路来实现的,这样就导致了传统的狄克型辐射计时序精确性和准确性不是很高,本文设计的基于FPGA的数据采集系统可将传统的调制,同步解调和积分比较器改进为数字型,这样就使得对辐射计的时序控制更加精确,系统也更加紧凑、小型化。

1 总体设计方案

本系统以型号为EP2C8Q208的FPGA芯片作为主要的控制单元,该芯片成本低、功耗低、且配置灵活,系统主要包括电源模块、主芯片配置模块、数据采集模块、存储模块及NIOS II数据读取与传输模块,总的框图如图1所示。

图1 系统总体框图Fig.1 Verall block diagram of the system

2 硬件电路设计

硬件部分主要包括电源模块、主芯片配置模块、数据采集模块、存储模块等组成。电源模块主要有PTH12050、LT1764等芯片组成,系统上电后,由线性电源提供12 V电源,经PTH12050后输出5 V电压,再经LT1764后得到3.3 V电压和1.2 V电压,其中3.3 V电压主要供数据采集模块、存储模块、数据传输模块、FPGA的IO口使用,1.2 V是FPGA的内核电压;数据采集模块主要由AD7606组成,AD7606能最多采集八路信号,16位的分辨率,最大采样率可达200 KSPS;存储模块主要由MT48LC16M16A2型SDRAM组成,最高时钟频率可达133 MHz,容量为256 M;数据传输模块主要有串口传输模块和网口传输模块组成,串口采用max3232芯片,网口采用W5300芯片。

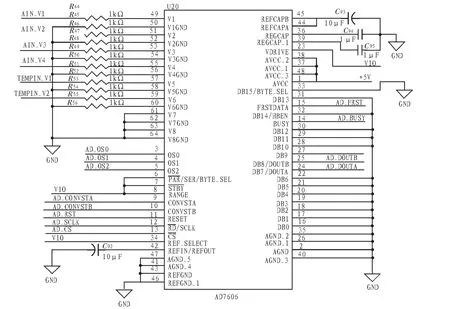

硬件系统的核心是在于FPGA中搭建的NIOS II软核,它控制着外围电路的正常工作,而外围电路主要包括数据采集电路、数据缓存电路和上位机通信电路。数据采集电路包括ADC及ADC控制单元,本设计中为节省资源将AD7606设计成串行输出,其设计原理图如图2所示,ADC的控制部分主要通过verilog HDL语言编写的控制程序在FPGA中实现;数据缓存单元的存在是因为软核与外设ADC的读写速度不一致造成的,数据缓存单元用来缓存AD控制单元送来的数据,该单元由一块RAM组成,这块RAM分为上下各半部分,当上半部分存满之后开始存储下半部分,同时NIOS II软核读取上半部分,依次循环,这种结构能保证数据连续采样而不丢失[2];上位机通信电路主要是串口电路和网口电路,系统采集的数据能通过串口或者网口传至上位机。

3 软件设计

3.1 FPGA逻辑设计

FPGA逻辑设计主要用来完成AD7606的控制、数据的缓存及自定义逻辑,系统上电后,AD控制部分控制AD7606的初始化及数据转换,主要是控制CONVSTA、CONVSTB、CS、及RESET信号的时序,CONVSTA与CONVSTB是两个通道的转换开始信号,CS和RESET分别是片选和复位信号,当各个控制信号满足时序要求时,AD7606即能正常工作;同时AD控制部分将采得的数据写入Ram中,当Ram上半部分写满后会产生中断来通知软核读取上半部分的数据,同时继续将数据写入下半部分,依次循环,其中Ram与软核的通信是通过Avalon总线实现的,这中间需要自定义一个Avalon slave型的Ram读组件,由于软核只需要读Ram中的数据而不需要对其进行写操作,因此自定义组件只包含了读地址和读使能信号[3],通过该组件即可实现软核与Ram的正常通信。

3.2 C程序设计

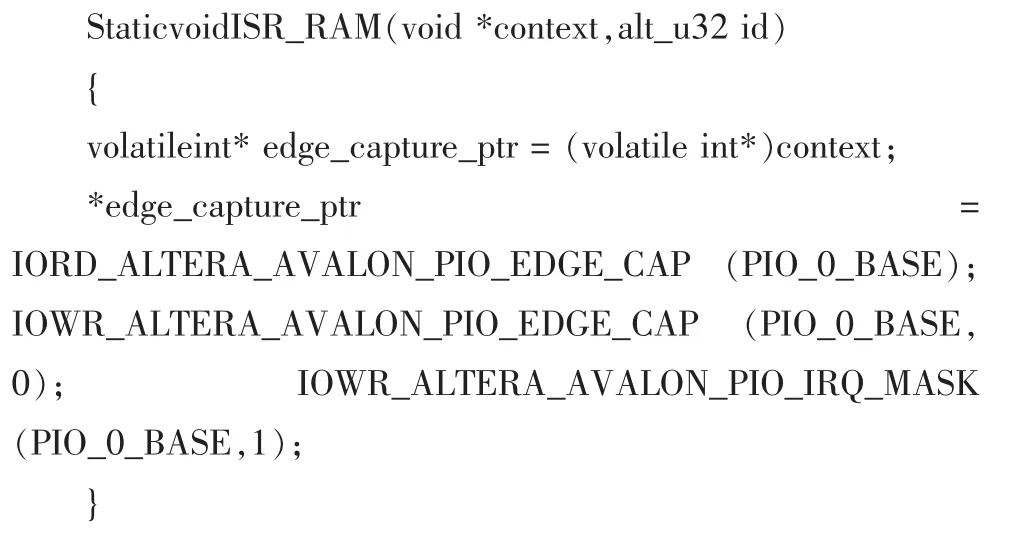

该部分设计主要是针对NIOS II软核的程序开发。NIOS II处理器的软件开发环境IDE为开发者提供了低层设备驱动及丰富的标准库资源,并在main函数之前自动完成系统和外设的初始化,因此开发者只需做好应用程序的开发即可[4],软件流程图如图4所示。

图2 AD7606电路图Fig.2 Schematic of AD7606

初始化部分由NIOS II软核自带的驱动自动完成,在采集开始之前加上一PIO使之与CONVSTA信号相与来作为AD7606的开始采样信号,在采样开始后采得的数据会写入到Ram中,进而产生中断来将数据存入到SDRAM中并输出。

3.2.1 中断控制

在Ram控制中,当Ram的上半部分或者下半部分写满时会产生中断信号,该中断信号与一个PIO信号相连接,通过控制与PIO相关联的四个寄存器即可使NIOS II软核响应中断来实时读取Ram中的数据[5]。

图3 软件流程图Fig.3 Flow diagram of software

NIOS II处理器在响应中断时需要调用相对应的中断服务函数,而NIOS II中的中断服务函数有着特定的要求,每个中断服务函数须经注册后才能生效[4],以下为中断服务函数。

3.2.2 RAM的读取

NIOS II处理器读取外设的信息时牵涉到地址对齐问题,而要读取Ram中的信息需采用动态地址对齐方式,在动态地址对齐方式下,NIOS II处理器一次读操作将连续读取4个字节的数据,所以在编写程序时偏移地址应每次加4[6],以下是读取RAM的程序。

3.2.3 数据的传输

NIOS II处理器将读取的数据存入SDRAM后可通过串口或者网口发到上位机上。网口的数据传输程序比较复杂,本文只介绍串口的数据传输,同其他外设,使用串口时也需先注册串口中断,然后再写串口中断服务函数。UART核内有5个关键的寄存器,通过控制这5个寄存器即可有效控制串口的正常工作,并将采得的数据通过串口传输到上位机[5]。

4 实验结果与验证

由于微波辐射计最后检波输出的信号频率比较低,且用串口传输的速率也比较低,所以程序中将AD7606的采样率设置的比较低,为验证系统性能,以5 K的采样率对100 Hz的标准正弦波和方波进行了采样,从采样结果可以看出,无论是采样幅度还是采样精度都能满足辐射计的要求。图4是标准的正弦波采样结果,图5是标准方波采样结果。

图4 标准正弦波采样结果Fig.4 Sampling results of standard sine wave

图5 标准方波采样结果Fig.5 Sampling results of standard square wave

5 结 论

文中设计的以FPGA为核心的数据采集系统,通过添加外设和自定义逻辑到NIOS II软核实现了对系统的整体控制,而且设计比较灵活,易于实现,移植性也比较强。经试验验证,该系统能够很好的实现数据采集功能,能达到微波辐射计数据采集的要求。

[1]雷震东,林士杰,张祖荫,等.脉冲噪声注入式零平衡型高精度微波辐射计系列[J].微波学报,1990(2):1-5.LEI Zhen-dong,LIN Shi-jie,ZHANG Zhu-yin,et al.High precision microwave Radiometer series of impulse noise injection and zero balanced[J].Microwave Journal,1990(2):1-5.

[2]杨林楠,李红刚,张丽莲,等.基于FPGA的高速多路数据采集系统的设计[J].计算机工程,2007,33(7):246-248.YANG Lin-nan,LI Hong-gang,ZHANG Li-lian,et al.Design of high-speed and multi-channel data acquisition system based on FPGA[J].Computer Engineering,2007,33 (7):246-248.

[3]王建国,洪胜峰.基于SOPC的视频点播系统设计[J].计算机工程,2007,33(22):277-282.WANG Jian-guo,HONG Sheng-feng.VOD system design based on sopc[J].Computer Engineering,2007,33 (22):277-282.

[4]李兰英.NIOS II嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[5]刘福齐.基于VHDL的FPGA和NIOS II实例精炼[M].北京:北京航空航天大学出版社,2011.

[6]万里,李刚,林凌.基于NIOS II的数据采集系统[J].新技术新工艺,2009(3):1-4.WAN Li,LI Gang,LIN Ling.Data acquisition system based on NIOS II[J].New Technology and Crafts,2009(3):1-4.