基于FPGA的数据采集与处理系统研究

2015-06-08王薇

王薇

(四川财经职业学院 电子商务系,四川 成都 610101)

现代工业生产和科学研究对数据采集的要求日益提高,要求数据采集系统接口有较高数据传输率的同时还需要配备高性能控制器件对数据做出快速准确的处理[1]。可编程逻辑门阵列(FPGA)可现场直接根据系统要求定义和修改其逻辑功能,采用FPGA能短时间完成低成本、低功耗的数据采集系统设计[2-3]。

针对绝对编码器等SSI接口传感器的应用,文中设计了一种基于FPGA的多通道数据采集与处理系统。系统的数据分析和输出显示完全由PC机软件来完成,而数据采集是在SOPC软件的控制下由FPGA上运行的逻辑语言实现的。

1 硬件设计

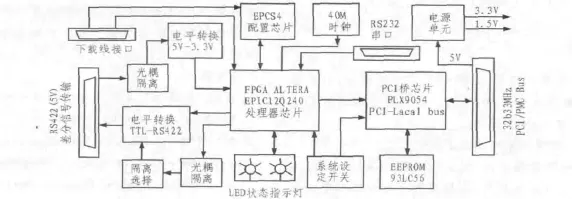

根据常见的SSI接口传感器实际需求,综合考虑数据采集系统开发难易程度及元器件性能和优势等多方面因素后,设计的多通道数据采集系统硬件总功能框图如图1所示。

图1 数据采集系统硬件功能总框图Fig.1 Data acquisition system total block diagram of the hardware capabilities

数据采集系统的核心微处理器FPGA采用了ALTERA公司的CYCLONE系列芯片EP1C12Q240C8,主要用于实现同步串口(SSI)时钟产生、数据采集与整理、数据码制转换、数据通道选择、波特率转换及FIFO存储等功能,系统的所有控制语言都是在FPGA内部编程实现的。所设计的数据采集系统通过PCI9054桥接芯片实现FPGA局部总线到PMC/PCI总线的转换,而后通过PMC/PCI总线完成数据采集系统与上层母板的连接和通讯。数据采集系统的采集接口部分通过RS422串口来实现传感器到采集系统的数据传输,因工业现场数据大部分存在大量的电磁干扰,设计中采用双沟道配置高速光耦HCPL263对输入信号进行隔离,同时为满足光耦隔离电路输出信号电平需求,系统选用ADG3304 BRU进行电平转换。

TTL-RS422电平转换电路采用MAXIM公司生产的MAX3030E芯片,主要用来完成SSI控制时钟的TTL-RS422电平转换。系统通过DB9与PC机相连,采用PC机中使用最广泛的RS232接口,物理接口符合RS232电气标准,自定义通讯协议,实现了可编程片上系统(SOPC)对系统的管理。方便用户清楚的了解数据采集系统的工作状态,系统设计了一个专用的电源和一个供用户自定义的LED状态指示灯。同时为了应对数据采集系统工作中出现故障等紧急情况,还设计了两个供用户自定义的复位开关。数据采集系统通过40MHz的有源晶振系统提供时钟,其中PCI9054局部总线的时钟由FPGA内部锁相环分频得到,而PCI9054的PMC总线侧的时钟由PMC端口通过PCLK引针提供33MHz的工作频率。数据采集系统通过EPCS4配置芯片对FPGA进行上电配置,具体可采用串行配置和并行配置,也可通过外部下载接口进行FPGA的在线内部代码更新。

系统主要电路设计:1)电源设计,通过AMS1117-ADJ和LM1117-3.3芯片将PMC总线Pn1/Jn1接口提供的5 V电源转换为FPGA芯片(EP1C12Q240C8)及其它器件所需的1.5 V及3.3 V电源;2)FPGA设计,通过基于Flash的可在线多次编程EPCS4芯片实现FPGA的配置,并设计电路实现被动串行和主动串行两种配置方式;3)RS232设计,通过MAXIM公司的MAX3232E转换芯片完成LVTTL和RS232信号电平的转换与传输,其中一路收发信号与DB9接插件相连,另一路收发信号与CON3相连以作备用收发端,其余信号直接输入FPGA。

2 软件设计

FPGA数据采集系统软件用于实现:1)与计算机的信息交互,即接收波特率、数据分辨率、数据编码方式、工作模式以及运行控制等信息;2)实现对传感器的SSI接口协议;3)实现传感器数据的传输。主要包括固化在数据采集卡存储器装置内的嵌入式软件和逻辑。其中用户逻辑包括数据处理、数据缓存、数据传输、波特率发生器以及SSI配置接口模块等,而SOPC系统包含Nios II软核、BRAM、EPCS控制器、RS232控制器、SSI寄存器接口部件以及系统互联[4]。

通过FPGA开发软件Quartus II进行主要模块的设计:1)波特率发生器,根据输入的波特率选择信号产生相应的波特率作为多路数据的输入时钟以及数据处理模块的时钟;2)数据接收整理模块,接收符合SSI接口协议的数据,实现了SSI接口协议以及数据的串并转换;3)码制转换模块,根据输入的编码方式按需要进行格雷码与二进制间的转换[4-6];4)数据输出模块,接收码制转换输出的数据并经握手操作将数据传给数据复接模块;5)数据复接模块,接收多路数据输出模块的数据并再对每路数据组帧以后输入数据缓存(FIFO)[4-6];6)数据源发生器以及切换器,根据输入的数据源选择信号选择内数据源发生器还是所采集数据进行输出;7)数据缓存,异步FIFO通过Show-ahead/First-word Fall-through模式存储复接模块的输出数据;8)数据传输模块,将数据缓存中读取的数据传输到PCI 9054的 Local Bus上;9)SSI配置接口模块,包含针对系统以及SSI接口的命令和控制寄存器控制系统运行及配置等[4]。

软件设计中没有对中断处理及处理器执行效率很高的要求,SOPC设计中没有使用TCM,这样可以节省FPGA器件内部的嵌入式RAM块;SOPC对应的嵌入式软件的代码量不大,所以指令和数据Cache大小采取最小设置,这样可以节省FPGA器件内部的嵌入式RAM块;Nios II软件的调试中因为没有使用硬件断点、数据触发、指令跟踪、片内跟踪及片外跟踪等高级调试手段,所以SOPC中只选择了最简单的JTAG调试级别。

通过VxWorks进行PMC总线的驱动程序设计。进行处理器驱动程序编程时首先编写处理器的I/O接口子程序SSICreate()、SSIDelete()、SSIOpen ()、SSIClose()、SSIRead ()、SSIWrite()及SSIIoctl (),SSICreate()的作用是通过调用iosDevAdd()函数将设备添加到I/O系统。然后编写驱动程序的主要部分PMC_FPGA_Init(),其用于实现设备查找、物理空间的获取、中断初始化、信号量使用、加载I/O函数。同时编写中断服务子程序intHandle(),实现中断响应后需要执行的操作。

3 系统调试

调试时,主要通过Siemens公司生产的SSI接口的绝对编码器对所设计数据采集处理系统的SSI接口和内外数据源特性进行了验证。

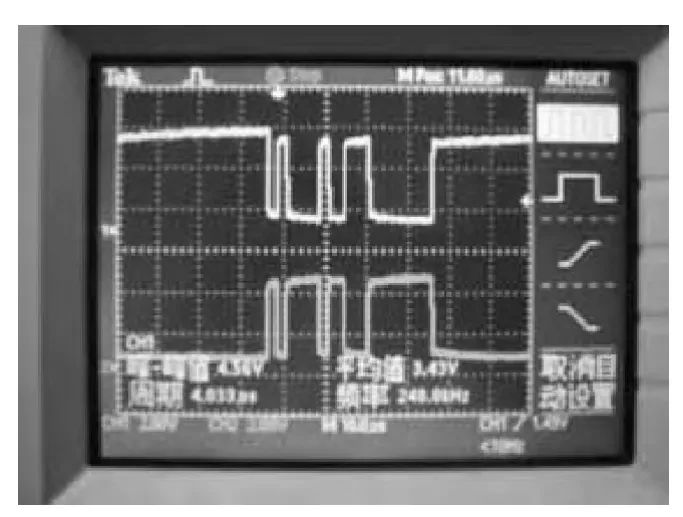

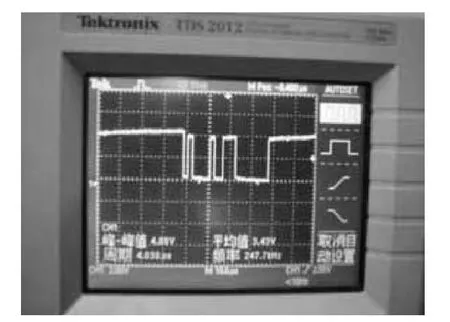

进行SSI接口特性测试,将编写的逻辑写入FPGA配置芯片后,对所设计的采集系统和绝对编码器分别供给5 V和24 V电源,把编码器的接口依次与采集卡的4路时钟和数据信号相连,用示波器观察输入输出信号。其中绝对编码器输出的差分数据信号和经光耦隔离之后输入FPGA的TTL电平的数据信号分别如图2与图3所示,可见所设计的SSI接口可以实现数据采集功能。

4 结束语

图2 SSI接口测试--编码器输出的差分数据信号Fig.2 SSI interface test--differential data signal output of the encoder

图3 SSI接口测试--输入FPGA的TTL电平信号Fig.3 SSI interface Test--TTL level input FPGA signal

文中主要设计了一个基于FPGA的多通道数据采集处理系统,该系统前端接口为SSI接口,可应用于符合SSI接口的绝对编码器和磁致伸缩型磁尺等。设计时选用Altera公司的FPGA作为核心处理器,并配置有PCI9054作为FPGA与PMC总线的数据传输通道[4]。以SSI绝对式编码器为标准对所设计的系统进行了调试,可见所设计的数据采集与处理系统能够以较高的精度实现预定的功能。

[1]张琴,马游春,李锦明.基于 PCI Express高速数据采集卡的接口设计[J].测控技术,2010,29(2):63-66.ZHANG Qin,MA You-chun,LI Jin-ming.High-Speed data acquisition card interface design based on PCI expres[J].Measurement&Control Technology,2010,29(2):63-66.

[2]龙雷.基于FPGA的多通道数据采集系统设计[J].电子科技,2014,7(1):128-130.LONG Lei.Design of multichannel data acquisition system based on FPGA[J].Electronic Science and Technology,2014,7(1):128-130.

[3]余林,张厚武,姚凯学.基于 FPGA和单片机的 PCI数据采集卡[J].仪表技术与传感器,2011(12):108-110.YU Lin,ZHANG Hou-wu,YAO Kai-xue.Design of PCI data acquisition card based on FPGA and microcontroller[J].Instrument Technique and Sensor,2011(12):108-110.

[4]郭耀华,姚明林,张银蒲.基于FPGA的SSI接口传感器通信系统[J].仪表技术与传感器,2010(11):11-15.GUO Yao-hua,YAO Ming-lin,ZHANG Yin-pu.Design of communication system for SSI interface sensor based on FPGA[J].Instrument Technique and Sensor,2010(11):11-15.

[5]刘怿恒.基于FPGA的数据采集与处理系统设计[D].长沙:湖南大学,2013.

[6]徐祥,蒋哲,王威廉.基于FPGA的高速数据采集、缓存与处理系统[J].电子测量技术,2013,36(4):68-71.XU Xiang,JIANG Zhe,WANG Wei-lian.High-speed data acquisition,caching and processing system based on FPGA[J].Electronic Measurement Technology,2013,36(4):68-71.