硅微波BJT集电极-发射极漏电的失效机理分析

2015-05-16胡顺欣李明月苏延芬邓建国

胡顺欣,李明月,苏延芬,邓建国

(中国电子科技集团公司第十三研究所,河北石家庄050051)

硅微波BJT集电极-发射极漏电的失效机理分析

胡顺欣,李明月,苏延芬,邓建国

(中国电子科技集团公司第十三研究所,河北石家庄050051)

介绍了硅微波双极晶体管中一种集电极-发射极漏电的失效模式,着重从芯片制造工艺方面研究了失效机理。建立了RIE等离子体刻蚀等效电容模型,研究了电容介质隧穿/击穿诱发的工艺损伤和接触孔侧壁角度对PtSi的影响。结果表明:RIE干法刻蚀在接触孔局部诱发Si损伤,接触孔侧壁角度减小导致参与合金的Pt总量增加,部分Pt沿此通道穿透发射结进入中性基区形成深能级陷阱,在高反偏集电极-发射极电压VCE作用下进入扩展的集电结空间电荷区,增加了空间电荷区电子-空穴对的产生率和集电结反偏电流ICO,形成快速增大的集电极-发射极漏电流ICEO,导致芯片失效。

硅微波双极晶体管;介质击穿/隧穿;等离子体充电效应;等离子体损伤;PtSi合金

随着装备系统对硅微波双极晶体管提出更高增益、更高效率、更高可靠性的要求,硅微波双极晶体管研制中的设计线宽和结深不断缩小,器件的功率性能和频率性能不断提升。但随着器件结深的减小和中性基区的减薄,越容易出现集电极-发射极穿通或漏电现象。对于集电极-发射极穿通或漏电失效机理研究,尤其是从工艺层面进行的研究鲜有报道。本文从工艺层面对硅微波双极晶体管芯片制造中出现的一种发射结反向击穿电压BVEBO和集电结反向击穿电压BVCBO均正常、而集电极-发射极电压VCE漏电的失效机理进行了研究。

1 失效分析

1.1 失效现象

一种梳状电极结构的硅npn型微波双极晶体管芯片进行BVEBO、BVCBO、BVCEO等直流参数测试。BVEBO、BVCBO均在规定范围内,单参数测试成品率达99%以上;芯片综合成品率主要受BVCEO失效影响,表现为集电极-发射极电压VCE漏电,测试曲线示意图如图1所示。

图1 VCE测试曲线示意图

图2给出了VCE正常芯片和VCE漏电芯片的发射极接触孔PtSi合金剖面SEM照片,基极接触孔与发射极接触孔现象相同。可以观察到:在VCE正常的发射极接触孔内PtSi欧姆接触层厚度均匀且连续;而在VCE漏电大的发射极接触孔内出现如图2b所示的“PtSi异常”现象。

1.2 失效机理

图2 发射区接触孔PtSi合金SEM照片

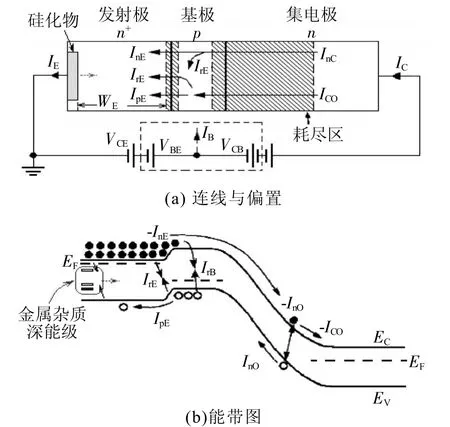

图3给出了VCE测试时的npn晶体管偏置和能带图,PtSi位置及Pt引入的深能级也同时绘制在图中[1-3]。

随着局部PtSi合金深度的增加,有效发射区厚度WE减小,同时PtSi/Si界面及其下方具有一定浓度和深度分布的深能级陷阱[2-4]逐渐接近、进入甚至穿透发射结和中性基区;随着VCE的增大,反偏的集电结空间电荷区向中性基区逐步扩展,包含了越来越多的深能级陷,电子-空穴对的产生速率随之加快,增大的集电结反偏漏电流ICO形成快速增加的集电极-发射极漏电流ICEO(抑ICO),导致芯片失效。

图3 VCE测试时的npn晶体管

1.3 失效验证

PtSi合金制备工艺模块包含接触孔RIE干法刻蚀工艺、直流磁控溅射Pt和退火工艺。实验采用两组正交条件进行:(1)溅射Pt及退火条件不变、改变接触孔刻蚀后的介质保留厚度和侧壁角;(2)刻蚀和Pt退火条件不变,改变Pt厚度。同时利用椭偏仪测量氧化层厚度,利用扫描电镜观测接触孔侧壁角和PtSi合金状态。

2 实验结果与讨论

2.1 实验结果

实验发现,Pt溅射厚度的改变对PtSi合金状态没有明显影响。表1给出了接触孔侧壁角为50°、65°、80°和接触孔刻蚀后介质保留厚度为30 nm、60 nm、90 nm时的PtSi合金状态。其中,d为Pt常规厚度,合金状态以发生异常(图2b)的接触孔数量与总接触孔数量的百分比来表征。由实验结果可以看出:(1)随着干法刻蚀后介质保留厚度从30 nm增加到90 nm,所有Pt溅射厚度和接触孔侧壁角度下的PtSi合金均趋于正常;(2)随着接触孔侧壁角度由50°增加到80°以上,所有Pt溅射厚度和干法刻蚀SiO2保留厚度下的PtSi合金均趋于正常;(3)随着Pt溅射厚度的减小,厚介质保留厚度和大侧壁角条件下的PtSi合金均趋于正常。

2.2 讨论

从实验结果可以看出,PtSi合金的好坏与接触孔硅表面状态有关,干法刻蚀后硅接触孔界面缺陷是导致PtSi合金异常的主要原因。

2.2.1 RIE干法刻蚀工艺

干法刻蚀工艺的采用会引入等离子体辐照损伤、物理损伤等工艺缺陷[5]。对于芯片表面覆盖有一层导电薄膜的多晶硅栅刻蚀,人们进行了大量天线效应、等离子充电效应损伤研究[6-9]。对于芯片表面为绝缘层的干法刻蚀损伤研究较少,并且集中在直接刻蚀到硅界面的研究。Ming Yang对干法刻蚀接触孔到硅界面的损伤机理进行了研究,指出直接刻蚀至Si界面时氧化层刻蚀副产物中的O+会导致结漏电、接触电阻增大[10]。对于在未刻蚀到硅界面前,除了等离子体辐照损伤[11]外,本文认为还存在一种“电容介质”隧穿/击穿诱发Si损伤。图4a给出了RIE刻蚀系统结构和等离子体-下电极等效电容模型示意图,图4b给出了刻蚀系统上、下电极和等离子体之间的电势分布示意图,图4c给出了接触孔刻蚀过程中接触孔形貌及介质厚度变化示意图。

表1 实验结果

由于刻蚀过程中等离子体与阴极之间电势差V2的存在,芯片附近自然形成一个以等离子体和下电极为两极、等离子阴极鞘层和芯片表面SiO2为介质的串联等效电容。接触孔刻蚀前的芯片表面介质高低起伏,接触孔底部SiO2层是表面介质最薄区如图4c所示。由于RIE刻蚀SiO2过程中的沟槽刻蚀效应[12],接触孔底部两侧成为介质最薄区,等效电容会在高电压V2作用下发生Fowler-Nordheim隧穿或击穿[12],并在硅表面形成毛细放电通道。随着刻蚀进程深入,SiO2不断损失,薄弱点/击穿点会持续向接触孔两侧扩展(图4c)。同时SiO2的减薄,电场不断增强,导致介质击穿/隧穿的损伤愈发严重。在刻蚀到介质保留厚度终止时,形成中间轻微、两侧严重的放电损伤区。

2.2.2 Pt溅射及退火工艺

图4 RIE刻蚀系统示意图

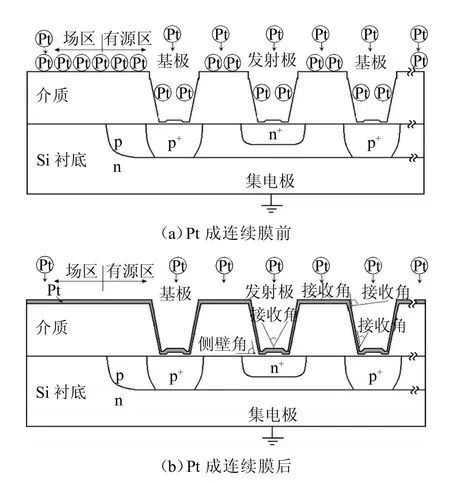

直流磁控溅射是物理淀积系统的一种,其溅射厚度遵循接收角理论[12],即系统平面中任意角度溅射速率均相等,芯片表面任意一点的薄膜溅射厚度与平面的溅射厚度之比等于其所在点的接收角度与平面角度(180°)之比。图5给出了溅射过程中Pt成为连续膜前(图5a)、后(图5b)的接触孔内外Pt分布、接触孔侧壁角和接收角。根据接收角理论,平面处的接收角度明显比台阶处的大,并且在接触孔底部边缘有最小接收角,因而平面处的Pt会快于接触孔侧壁上的Pt从颗粒变成连续膜。

高温下Pt会向Si晶格中扩散,形成替位式和间隙式杂质存在并引入深能级陷阱[2-4]。当接触孔底部Si表面存在损伤通道时,Pt会沿着通道优先扩散,在参与合金的Pt总量(即PtSi总体积)一定时,减小有效扩散面就会导致局部PtSi厚度增加。此外Pt的来源除了接触孔底部,还有接触孔侧壁甚至孔外平面。接触孔底部宽度一定时,随着接触孔侧壁角度的增加和Pt溅射厚度的减薄,参与合金的Pt总量在减少,PtSi厚度随之减小。

图5 溅射过程中Pt膜的变化

3 结论

介绍了硅微波晶体管芯片制造工艺中一种集电极-发射极漏电的失效现象,从工艺层面分析了芯片失效机理:Si表面在接触孔刻蚀等效电容介质隧穿/击穿作用下形成损伤通道,减小了Pt合金面积;接触孔侧壁角度减小导致参与合金的Pt总量增加;Pt在退火温度下沿此通道快速扩散进Si形成PtSi,同时部分Pt穿透发射结进入中性基区并引入深能级陷阱;陷阱在持续提高的反偏集电极-发射极电压VCE作用下被包进不断扩展的集电结空间电荷区,增加了空间电荷区电子-空穴对的产生率,集电极-发射极漏电流ICEO随集电结反偏电流ICO快速增大,导致芯片失效。通过增加接触孔侧壁角度和接触孔刻蚀后介质保留厚度,避免了由于PtSi合金异常导致的集电极-发射极漏电失效。

[1] S M Sze,KWOK K NG.Physics of Semiconductor Devices(Third Edition)[M].Hoboken,New Jersey:JohnWiely&Sons Inc.,2007.

[2] 丁孙安,许振嘉.Pt/Si界面反应与肖特基势垒形成的研究[J].红外与毫米波学报,1993,12(5):389-391.

[3] 丁孙安,许振嘉.(Pt及其硅化物)/硅界面的深能级研究[J].半导体学报,1994,15(3):149-155.

[4] RAND M J,ROBERTS J F.Observations on the formation and etching of platinum silicide[J].Appl.Phys. Lett.,1974,24(2):49-52.

[5] STEPHEN A C,著,曾莹,严利人,王继民,等译.微电子制造科学原理与工程技术(第二版)[M].北京:电子工业出版社,2003.281-282.

[6] WATANABE T,YOSHIDA Y.Dielectric Breakdown of Gate Insulator due to Reactive Etching[J].Solid State Technology,1984,26(4):263.

[7] FANG S,MCVITTIE J.Thin-Oxide Damage from Gate Charging During Plasma Processing[J].IEEE Electron Devices Lett.,1992,13(5):288.

[8] GABRIEL C,MCVITTIE J.How Plasma Etching Damages Thin Gate Oxides[J].Solid State Technol.,1992,34(6):81.

[9] CHEUNG K P,CHANG C P.Plasma-charging damage:A physical model[J].Journal of Applied Physics,1994,75(9):4415-4426.

[10]YANG M.Plasma damage and contact resistance[C]. Proceedings of5th InternationalConference on Solid-State and Integrated Circuit Technology.Beijing,China,1998:94-97.

[11]WU W,MCLARTY P K.Reactive ion etching induced damage with gas mixtures CHF3/O2 and SF6/O2[J].J. Vac.Sci.Technol.,1995,13(1):67-72.

[12]JAMES D P,MICHAEL D D,PETER B G.Silicon VLSI Technology:Fundamentals,Practice and Modeling[M].北京:电子工业出版社,2003.539-554,621-637.

[13]伍过珏,著,李秋俊,冯世娟,徐世六,等译.半导体器件完全指南(第二版)[M].北京:科学出版社,2009. 596-598.

Study on the Failure Mechanism of Collector-Emitter Leakage in Silicon Microwave Bipolar Transistor

HU Shunxin,LI Mingyue,SU Yanfen,DENG Jianguo

(The 13thResearch Institute of CETC,Shijiazhuang 050051,China)

The failure model of the collector-emitter leakage in the silicon microwave bipolar transistor was introduced.The failure mechanism was studied base on the manufacture process.The equivalent capacitor model in RIE etch system was built,the influences of the contact sidewall angle and the plasma damage from the capacitor dielectric breakdown or tunneling to the PtSi alloy were researched. The results show that the partial increased total Pt by decreasing the contact sidewall angle,diffused into the base,the traps which could increase the electron-hole generation rate and reverse currentICOin collector-base junction depletion region were formed,and the collector-emitter currentICEOwas quickly increase with the collector-base junction currentICO.

Silicon microwave bipolar transistor;Dielectric breakdown or tunneling;Plasma charging effect;Plasma damage;PtSi alloy

TN305;TN405

:A

:1004-4507(2015)07-0018-05

胡顺欣(1979-),男,山东临沂人,硕士,工程师,研究方向为微波功率器件芯片制造及失效分析。

2015-06-26