高速串行数据发送接收芯片CY7B923/933的原理及应用设计(下)

2015-05-08耿启立

耿启立

(中国地质装备集团有限公司,北京100102)

高速串行数据发送接收芯片CY7B923/933的原理及应用设计(下)

耿启立

(中国地质装备集团有限公司,北京100102)

本文主要介绍高速串行HOTLink发送接收芯片CY7B923/933的构成及工作原理,并给出了针对光纤传输、同轴电缆传输、屏蔽双绞线传输的应用设计。

高速串行;HOTLink;传输链路;发送;接收;CY7B923; CY7B933

(续第3期)

5 CY7B923发送器工作方式

正常情况下,发送芯片工作于编码或旁路两种工作模式之一。在编码工作模式,允许用户发送和接收8位数据和控制信息,而不需要将发送数据或控制字符转换为发送字符;旁路工作模式用于编码和解码由外部协议控制器来完成的系统。

两种工作模式下,CKW时钟上升沿将数据输入到输入寄存器,发送芯片的输入时序和功能可以匹配异步FIFO和时钟驱动FIFO的时序和功能(如图5所示)。

5.1 编码工作模式

编码工作模式,输入数据解析为8个数据位(D0-D7),1个控制位(SC/D)和1个系统诊断位(SVS)。如输入数据是正常的信息数据,SC/D输入应为低电平,使用表2所示的有效数据字符集对数据进行编码;如输入数据的内容是控制或协议信息,SC/D输入应为高电平,使用表4所示的有效控制和特殊字符集对数据进行编码,特殊字符包括用于光纤通道、ESCON、专有系统和诊断所需的所有协议字符。

5.2 旁路工作模式

旁路模式,输入数据解析为Db-h、SC/D(Da)和SVS(Dj)等10位进行序列化的预编码数据,通过链路发送。这时可采用适合设计者的任一编码方式,仅限制数据编码方法要适于接收器PLL数据同步器转换密度(每个字节10位),且和传输介质兼容。

CKW上升沿加载到输入寄存器的数据,在下一个CKW上升沿加载到移位寄存器,其后利用内部时钟发生器产生的时钟,每次移位一位数据到输出,首位发送字符(Da)在下一个CKW的上升沿出现在输出端(OUTA±、OUTB和OUTC±)。

不论是编码工作模式还是旁路工作模式,如在CKW上升沿到来时发送芯片输入未使能(ENA和ENN为高电平),编码器插入一个填充字符K28.5维持正常的链路同步。通过强制方式使发射芯片始终处于使能状态(即ENA或ENN强制连接到低电平),可以阻止自动插入填充字符。

5.3 PECL输出功能和连接选择

三个PECL输出对包含相同的输出信息,其设计初衷是用于具有多路连接的系统。每个输出对可以连接不同的串行传输介质,各传输介质可有不同的长度、连接方式和接口。对于不需要全部3个输出对的应用,为降低输出功耗和噪声,未使用的输出对应连接到VCC,内部电压比较器检测到输出对连接到VCC后,会禁止该输出对的电流源,可减低约5mA的功耗。

对于链路传输被禁止期间需要关闭输出的应用,其通过FOTO输入为高电平实现。虽然在旁路工作方式通过发送全“0”数据可以确保PECL输出驱动为低电平(即关闭光信号输出),但不方便在数据传输通道插入该级别的控制,且在编码工作方式也无法实现。FOTO信号简化且增强了该控制功能(常见于基于激光的串行传输应用)。FOTO输入高电平,强制OUTA+和OUTB+变为高电平,OUTA-和OUTB-变为低电平。OUTC±通常用于子系统诊断输入,不受POTO控制。这种功能分离允许设计者进行不同的系统架构设计,且不会使功能控制信号和数据通道过载。

5.4 发送器串行数据字符特性

CY7B923 HOTLink©发送芯片串行输出符合光纤传输通道的规范要求。串行数据输出由内部PLL锁相环控制,PLL锁相环通过10倍频CKW时钟产生位时钟。PLL锁相环和逻辑单元的抖动特性要求如下:

(1) 稳态抖动(Dj)<35PS(峰-峰值,在发送连续的K28.5(C5.0)条件下测试)

(2) 随机抖动(Rj)<175PS(峰-峰值,在发送连续k28.7(c7.0)条件下测试)

5.5 测试模式

CY7B923提供两种测试模式:BIST方式和TEST方式。在常规应用中,BIST方式可用来检查发送、接收功能以及连接链路。BIST方式对用户系统逻辑影响最小,且可作为系统诊断的一部分。

5.5.1 BIST模式

BIST模式的连接和时序如图14所示。

图14 BIST模式连接和时序示意图

BIST模式的功能如下:

(1)设置BISTEN为低电平,进入测试模式,发射芯片以位比特速率发送…1010…码串;

(2)设置ENA或ENN为低电平,生成测试序列;

(3)允许发送芯片执行多个BIST循环,或直到接收芯片测试完成,RP每个BIST循环产生一个低脉冲,连接到外部计数器用来监控测试模式循环;

(4)测试完成时,设置BISTEN、ENA和ENN为高电平,恢复到正常功能。

BIST模式用于检查发送、串行链路和接收的全部功能,同时增强了工厂的正常ATE测试,在不显著增加系统开销的情况下,为应用设计者提供了一个用于链路和传输系统检查的缜密测试机制。

在旁路模式,BIST逻辑功能同编码方式。MODE为高电平,BISTEN为低电平,使发送芯片切换到编码模式并开始发送BIST参数;如MODE为低电平,当BISTEN切换到高电平时,发射芯片恢复到正常的旁路模式。在TEST模式, BIST功能工作于正常模式。

5.5.2 TEST模式

发送芯片的3种工作方式通过MODE输入管脚来选择。当MODE连接到VCC时,旁路编码器,Da-j直接从输入寄存器加载到移位寄存器;当MODE连接到GND时,采用光纤通道8B/10B编码序列对输入D0-7、SVS和SC/D进行编码。由于发送器通常硬连接到编码方式或旁路方式且两种方式间不切换,为MODE管脚设计了第三种选择功能,即悬空MODE管脚(内部电阻保持MODE管脚为VCC/2电平)选择芯片TEST工作方式,用于工厂芯片生产测试或用户来料检验。

测试模式使发射芯片工作于编码模式,OUTA+/OUTB+作为位速率时钟,替代了内部PLL锁相环产生的位时钟。在TEST模式,输入数据由CKW时钟锁存到输入寄存器,输入寄存器和移位寄存器间的数据传输由内部计数器来定时。位时钟和CKW必须保持固定的相位和10倍频关系。RP信号相位和脉冲宽度由位计数器(PLL反馈计数器)相位来控制,输入和输出参数可由内部逻辑获取RP状态来同步,或使用下列技术,通过芯片初始化来匹配ATE测试参数:

(1) 不管MODE引脚为高电平或低电平,停止CKW和位时钟;

(2) 在时钟停止期间,强制MODE引脚为MID状态(悬空或保持VCC/2电平);

(3) 启动位时钟,确保其运行至少两个周期;

(4) 启动CKW时钟,其频率为位时钟频率的十分之一。

6 CY7B933接收芯片工作方式

正常情况下,CY7B933可工作于两种模式之一。编码模式允许用户发送和接收8位数据和控制信息,而无需先将其转换为传送字符;旁路模式用于编码和解码由外部协议控制器来完成的系统。

在任一工作模式下,通过两个差分输入对之一接收串行数据,路由到移位寄存器和时钟同步单元,时钟同步器内的PLL锁相环用其内部产生的比特率时钟“对齐”输入位数据流,并将位数据流输入到移位寄存器,在完成1个字节移位时(10个位数据移位时间),累计在数据移位寄存器的数据传送给解码寄存器。

为了按预设的字节边界“对齐”输入位数据流,必须对时钟同步器的位计数器进行初始化。成帧器逻辑单元按定义字节边界的特定参数检查输入位数据流。组合逻辑滤波器查询X3.230符号定义的K28.5特殊字符(逗号),找到K28.5后,时钟同步器内的自由运行位计数器同步地复位到其初始化状态,从而按正确的字节边界“组帧”数据。

由于感应噪声误码会导致输入数据流的“损坏”,同时由于误码和正常合法数据会组合创建K28.5字符,设计了禁止位计数器重复同步的选择,当RF输入保持低电平时,将禁止成帧器;当RF为高电平时,直到查询到K28.5,禁止RDY,其后,RDY恢复到正常功能。

6.1 编码方式操作

编码方式,串行输入数据解码为八位数据(Q0-Q7),上下文控制位(SC/D)和系统诊断输出位(RVS)。如解码寄存器中的数据和有效数据字符表中数据一致,数据被解码为正常的数据信息,SC/ D输出低电平;如输入位流数据和有效特殊字符编码和序列表中数据一致,其被解码为“控制”或“协议信息”, SC/D输出高电平。特殊字符包括用于光纤通道、ESCON、其他专用和诊断数据包所定义的所有协议字符。

6.2 旁路方式操作

旁路方式,不对串行输入数据进行解码,10位数据(Qa-j)直接从解码寄存器传送到输出寄存器。系统默认在传送之前已对数据进行过预先编码,并由连接到HOTLink链路的其他外部逻辑单元进行解码,数据可以使用适于设计者的任一编码方式,唯一限制是编码方式要采用适于接收芯片PLL锁相环数据同步器的转换密度(每个字节10个bit),且和传输介质兼容。

旁路方式,成帧器功能同编码方式,K28.5参数仍用于“帧重构”串行位流数据。

6.3 并行输出功能

Q0-7、SC/D、RVS等10个输出同时转换,通过RDY和CKR对齐,其时序可直接连接异步FIFO或时钟驱动FIFO。

利用CKR时钟上升沿(或下降沿),或RDY上升沿(或下降沿)均可将数据输出锁存入系统。如使用CKR做数据输出锁存,RDY可用作接收允许逻辑信号;RDY低脉冲表示已经接收到新的数据并准备交付新数据,RDY信号为低电平60%占空比的字节速率脉冲串,适于用作CY7C42X异步FIFO 写脉冲,或CY7C44X时钟驱动FIFO写输入允许。RDY高电平表示呈现在输出端的接收数据为可忽略的NULL字符(发送芯片在输入数据间插入的填充字符)。

当禁止发送芯片时,其将连续发送填充字符(K28.5),为确保接收FIFO不被这些虚拟字符填充而溢出,在此期间禁止RDY脉冲输出。由于K28.5字符串解码为Q0-7=00000101和SC/D=1,Q0-7输出数据反映出接收数据正确但无变化。当新的数据(非K28.5)出现时,RDY输出恢复正常功能,最后一个K28.5将伴随输出正常RDY脉冲。

填充字符被定义为任一K28.5字符后接续的仍是K28.5字符,所有的填充字符都不会引发RDY脉冲。任一K28.5字符后接续的任何其他字符(包括违规字符和非法字符)都将被解析为有效数据,会引发RDY脉冲。

如上所述,RDY也可用来表示接收数据帧正确。而当接收芯片在RF高电平状态等待接收K28.5字符时,RDY输出被禁止。当RDY再次恢复启用后,接收数据会被正常的“组帧”和解码。在RF为高电平状态下的旁路模式,每接收到一个K28.5字符,RDY就输出一个脉冲。

6.4 接收芯片测试模式

CY7B933提供两种测试操作方式,BIST方式和TEST方式。在正常应用情况下,BIST方式用来检查发送芯片、接收芯片及链路的功能,该模式对用户系统逻辑影响最小,且可将其作为用户系统诊断的一部分。

6.4.1 BIST方式

BIST方式的功能如下:

(1)设置BISTEN为低电平,允许自测试功能;等待RDY变为低电平,表示接收到初始化编码;

(2)监测RVS,在任一字节时间,利用RVS管脚的高电平来检测参数是否失配。RDY在每个BIST循环输出一个高脉冲信号,可被外部计数器用来监测测试模式进程。Q0-7、SC/D用来表示预期的参量,可用于调试;

(3)测试完成时,设置BISTEN为高电平,恢复正常工作模式。

6.4.2 TEST方式

MODE输入管脚用来选择接收芯片的三种工作方式之一。当MODE管脚连接到VCC时,旁路解码器,移位寄存器的数据直接从解码锁存器所存到输出寄存器的Qa-j输入端;当MODE管脚连接到GND时,使用8B/10B编码进行解码,输出Q0-7、RVS、SC/D;第3个功能为TEST方式,用于工厂测试和来料检验,通过保持MODE管脚开路来选择(内部电路使MODE管脚维持VCC/2电平)。

TEST模式使接收芯片工作于编码模式,将INB(INB +)用作位速率时钟,替代内部PLL锁相环产生的位速率时钟。在TEST模式,由正常逻辑控制移位寄存器、解码寄存器、输出寄存器间的传输,但使用外部位速率时钟替代PLL锁相环内部时钟,内部逻辑和测试参数输入通过发送一个SYNC参数来同步,使成帧器对齐位数据流逻辑,流程如下:

(1)维持TEST方式多个时钟周期,用来建立正常的计数器序列;

(2)维持RF为允许“帧重构”状态;

(3)输入表示K28.5( Sync)的重复位序列;

(4)RDY变为低电平,表示通过K28.5输入参数建立了字节边界;

(5)通过参数、电压和时序测试进程,可方便测试程序和测试者。

TEST方式,在无需测试人员提供输入数据或PLL锁频及部分正常工作方式下所需的跟踪和频率特性条件下,对接收芯片进行逻辑、DC和AC测试。

7 应用设计

依据传输距离及传输速率要求,可分别选用光纤、同轴电缆、双绞线作为传输介质,与CY7B923/933一起构成高速串行传输链路。

7.1 基于光纤传输的应用设计

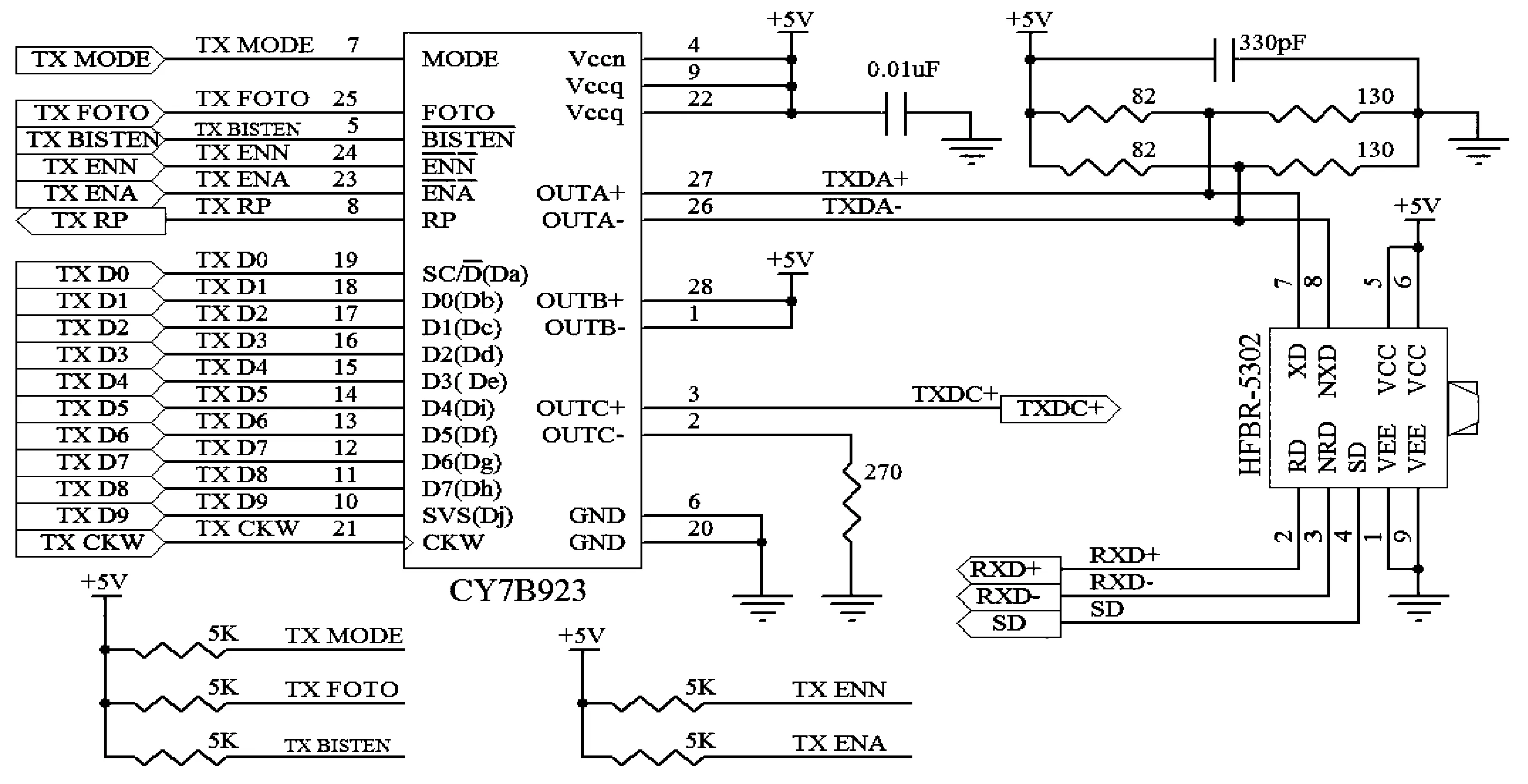

图15和16是采用光纤为传输介质的CY7B923发送端口设计原理图和CY7B933接收端口设计原理图。

图15 光纤传输CY7B923发送端口设计原理图

采用光纤传输的应用设计,应考虑以下因素,并采取适当的设计对策:

(1)去耦合。为了消除电源耦合,需在发送和接收每个芯片的VCC和GND间旁接0.01uF电容;

(2)光纤的选型。远距离(20~120km)传输,可考虑选用单模光纤;中远距离(2~5km)传输,可考虑选用多模光纤;短距离(100m左右)传输,可考虑选用塑料光纤。

(3)光纤收发模块的选型。光纤模块的选型需综合考虑传输距离、传输速率、安全性等要求。短距离较低传输速率的应用,建议选择LED光源型光纤收发模块,即降低了成本,又无需采取安全性保障措施;长距离较高传输速率的应用,建议选用激光光源型光纤收发模块,但需采取安全性设计保障对策,确保应用安全。

7.2 基于同轴电缆、屏蔽双绞线传输的应用设计

图17、图18是采用75Ω同轴电缆(或150Ω屏蔽双绞线)为传输介质的CY7B923发送端口设计原理图和CY7B933接收端口设计原理图(说明:同轴电缆采用BNC/TNC连接器,屏蔽双绞线采用9芯D型连接器)。

图18 同轴电缆(屏蔽双绞线)传输CY7B933接收端口设计原理图

[1] CYPRESS. CY7B923/CY7B933 HOTLink© Transmitter / Receiver[Z]. 2014.

[2] CYPRESS. HOTLink© Design Considerations[Z]. 2014.

2015-03-01

耿启立,男,中国地质装备集团有限公司地质仪器室主任、高级工程师,1984年毕业于长春地质学院地质仪器专业,长期从事地震仪器、电法仪器及嵌入式产品设计开发、研发管理、项目管理、质量技术管理等工作,多次主持开发国家重点技术创新项目,Tel:18600398326,E-mail: gengqili@cgeg.com.cn。

P631.32

A

1009-282X(2015)05-0021-05