一种宽频带频率源的设计与实现

2015-04-28张贯强田克纯

张贯强 田克纯

【摘 要】频率源是现代通信系统中不可或缺的一部分,在卫星通信、数字通信、雷达和导航等领域有着广泛的应用。本文给出了一种利用TI MSP430控制ADF4350设计频率合成器的方法,然后利用ADIsimPLL软件对其性能进行了仿真,最后,通过制作电路板,对其性能进行了实际测试。测试结果表明,该频率合成器具有较好的杂散水平和较低的相位噪声,能够满足教研室宽频带多制式软件无线电样机的本振源的要求。

【关键词】宽频带;频率源;ADF4350;MSP430F149

0 引言

随着无线通信、数字电视、卫星定位、遥控遥测技术以及精密制导等现代高技术的广泛应用和不断发展,对频率源的频率稳定度、频谱纯度、频率范围和输出频率点数的要求越来越高[1]。本文主要介绍了ADF4350频率合成器芯片,并利用该芯片设计了覆盖137.5~4000MHz的宽频段频率源,并对其性能进行了主要的测试。该频率源外围电路简单,体积较小,调试的时候只需要修改环路滤波器的参数和单片机控制程序,与用分离元器件实现的锁相环电路相比,调试量较小,抗干扰性能良好。

1 宽频带频率源的软硬件设计

1.1 ADF4350频率合成器芯片介绍

ADF4350频率合成器芯片内部集成了压控振荡器,基波输出频率范围为2200~4400MHz,利用内部可编程的1/2/4/8/16/32分频电路,可以产生137.5~4400MHz的射频信号。利用SPI接口可以很方便的对其控制,且输出功率也可以编程控制,可以工作在低噪声模式和低杂散模式[2]。采用TI公司的MSP430F149单片机进行控制,ADF4350与MSP430之间通过IO口模拟SPI进行通信。

1.2 宽频带频率源的参数设计

ADF4350频率合成器的设计主要包括内部寄存器的配置、外部环路滤波器的设计和芯片的外围电路设计。ADF4350射频频率输出公式为

ADF4350的频率输出可以通过单片机配置芯片内部的R5~R0寄存器实现,每个寄存器都是32位的,通过控制其低3位(C3~C1)可以对寄存器进行选择,上电初始化的时候需要先初始化寄存器5依次到寄存器0。本文根据锁相环频率合成器系统设计的要求,其公式(1)和(2)中的各参数具体为:

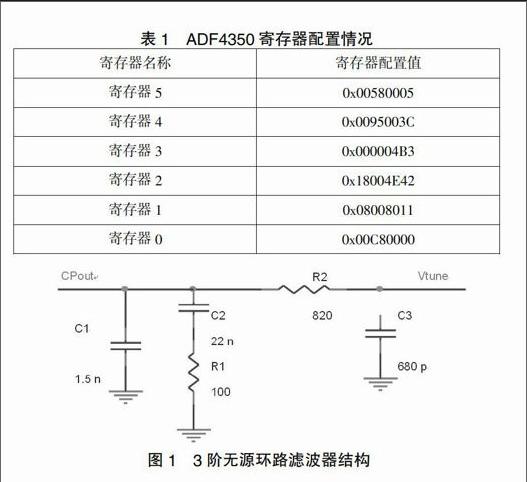

环路滤波器是一个低通滤波器,它主要由线性电容、电阻和运算放大器组成。其输入信号来自鉴相器的输出电压,它在滤除鉴相器输出电压中的高频分量和噪声后,取出平均分量去控制压控振荡器的频率。它的设计是频率合成器的关键环节,其设计结果的好坏直接决定了频率合成器最终的杂散、相位噪声、环路稳定性以及捷变时间等性能。环路带宽和相位裕量是影响锁相环频率合成器的两个关键因素,环路带宽越宽,频率合成器的锁定时间越短,但是相位噪声会变得越差[3]。环路滤波器结构主要分为无源环路滤波器和有源环路滤波器。采用有源环路滤波器将会增加相位噪声、复杂度以及成本,且有源环路滤波器主要用于电荷泵电压低于 VCO 调谐电压的情况。因此,本文选用3阶无源环路滤波器2R3C结构,首先利用ADIsimPLL软件对不同的环路带宽进行仿真,最终确定环路带宽为20KHz。环路滤波器结构如图1所示。

图1 3阶无源环路滤波器结构

经计算并且优化后元器件数值为:C1=1.5 n,C2=22 n,C3=680 p,R1=100,R2=820。对于环路滤波器的设计,可以利用ADI公司的ADIsimPLL软件进行仿真设计,并且能够观察到设计的频率合成器的性能,该频率合成器在2GHz处的相位噪声仿真曲线如图2所示,从图2中可以看出,在偏离载波频率10KHz处的相位噪声大约为-94dBc/Hz。这是个理想值,实际制作出来的频率源测试的相位噪声会变得差些[4]。

图2 2.0GHz频率处的相位噪声曲线

1.3 宽频段频率源的硬件电路设计

ADF4350宽频段频率合成器的硬件电路主要包括电源电路模块、MCU电路模块、环路路滤波器、芯片外围电路和频率显示模块等,其原理框图如下图3所示。

图3 ADF4350频率合成器硬件电路原理框图

本设计参考源采用两种方式提供,一种是10MHz的温度补偿晶振,另一种是外部参考源。有两种锁定模式,正常锁定模式和快速锁定模式,并且有LED锁定指示。在电路设计时,相位噪声和杂散是两个非常重要的指标,如果设计时滤波不充分、接地不当和PCB设计不正确,会导致频率源的指标严重恶化。为了能够得到较好的输出信号,需要采用优质电源并加强滤波和退耦,对温补晶振的电源、VCO电源和电荷泵电源要加强去耦,在靠近电源引脚处依次放置10p、100p、100n和10u(有极性)电容,这样可以有效减少电源纹波引入的杂散和最大限度滤除电源线上的干扰[5]。该电路同时存在数字电路部分和模拟电路部分,为了减少数字电路对模拟电路产生的干扰,通常情况下将数字部分和模拟部分分别接地,最后两者通过射频电感或者0欧姆电阻连接在一点。ADF4350采用双端差分输出,可以提高共模抑制比。并且通过射频扼流电感连接到VCO的电源端,可以获得更好的匹配性能,能够有效提高输出功率。

1.4 宽频段频率源的软件设计

系统软件设计部分主要包括单片机程序和上位机程序,单片机程序采用IAR环境开发,其功能接收上位机串口的数据并写入ADF4350的内部寄存器和实现频率的正确的显示。上位机程序采用VB6.0开发,其功能是按照ADF4350的数据格式进行编写,并通过串口发给单片机。ADF4350有两路差分输出,设计时只使用了主差分输出,辅助差分输出关闭。ADF4350的数字接口是与SPI兼容的串行接口,用于将数据写入器件,其单片机控制程序采用IO口严格模拟SPI时序实现。其串行时钟信号线CLK、串行数据线DATA、加载使能LE和芯片使能CE分别连接MSP430F149的P5.0、P5.1、P5.2和P5.3引脚。在CLK上升沿将32位数据逐位写入对应的寄存器,当LE变为高电平时,数据被传输至对应的锁存器。频率控制部分只要保证电平和送数时序正确,就能够完成对ADF4350芯片的配置,其程序可以通过BSL下载到MCU里面[6]。

2 系统性能测试

利用R&S频谱仪对频率源输出的信号进行测试,测试相位噪声时,将频谱仪的中心频率设置为2000MHz,将RBW设为10KHz,VBW设为30kHz,SPAN设为500kHz,测试结果如下图4所示,其值为-95.7dBc/Hz @100kHz。

图4 2000M射频输出信号偏离载波100K处的相位噪声

测试杂散时,将频谱仪的中心频率设置为2000MHz,将RBW设为1kHz,VBW设为3kHz,SPAN设为100MHz,测试结果如下图5所示,其值为-67.1dBc。

图5 2000M射频输出信号的杂散

3 结束语

本文利用ADF4350芯片实现了宽频段覆盖的频率合成器,可以作为收发信机的本振源。从测试的结果来看,该频率合成器具有较好的杂散水平和较低的相位噪声,能够满足教研室宽频带多制式软件无线电样机的本振源的要求。该频率源成本低和操作方便,能够很好用于实际应用中。

【参考文献】

[1]杨檍,鲍景富.现代频率合成技术的研究进展[J].电讯技术,2007,47(2).

[2]Analog Devices Inc. Wideband Synthesizer with Integrated VCO [M].Analog Devices Inc, 2011.

[3]Dean Banerjee.PLL Performance, Simulation and Design(4th Edition) [M]. National Semiconductor, 2006:11-17.

[4]赵浩平,刘乃安.锁相频率合成器ADF4360-4及其在W LAN 混频电路中的应用[J].国外电子元器件,2007,10.

[5]刘永智,徐盛旺,高树廷.超宽带频率合成器的设计与实现[J].电讯技术, 2009,12.

[6]万琰.基于单片机控制的ADF4106锁相频率合成器设计[J].电子元器件应用, 2009, 11.

[责任编辑:薛俊歌]