基于JESD204B协议的数据传输接口设计

2015-04-25周典淼陈维华孙兆林刁节涛

周典淼,徐 晖,陈维华,李 楠,孙兆林,刁节涛

(1.国防科学技术大学 电子科学与工程学院,湖南 长沙410073;2.南京军区气象水文中心,江苏 南京210016)

传统采样数据采用多路数据线并行传输方式,易受码间同步及串扰影响,且PCB布线复杂,已难以满足多通道、高宽带、小型化数传终端需求。目前,模数转换器(ADC)正经历从并行LVDS(低压差分信号)和CMOS数字接口到高速串行接口的转变。因此,JEDEC国际组织推出了新的AD/DA采样数据传输标准JESD204。

JESD204协议于2006年首次提出,只支持单一通道的数据传输,传输速度为3.125 Gbit·s-1;其升级版JESD204A协议增加了对多路串行通道传输的支持能力;JESD204B增加了对确定延时的条款并将传输速度进一步提高到了12.5 Gbit·s-1。

目前Xilinx公司已开发出实现JESD204B接口的商业化IP核,但收费较高。且对于特定的应用不便裁剪。当数据传输的准确率成为设计的重点时,可通过增加串行数据的控制字符、牺牲部分传输效率实现,当数据传输的速率成为考虑的重点时,则可适当减少串行数据中的控制字符。Xilinx公司Kintex-7系列的FPGA内部一般最少集成了8个高速串行收发器,可结合项目需求充分利用这些收发器。另外,目前国内对采集数据串行传输接口的研究较少,网上能收集到的相关论文较少,从丰富国内在此领域的研究成果上考虑,研究基于JESD204B协议的采集数据串行传输接口设计也较有意义。

1 JESD204B接口原理分析

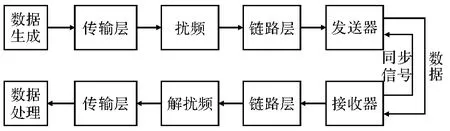

JESD204B接口包含发送接口和接收接口两种类型。无论是发送接口还是接收接口,其结构均可分为物理层、链路层、传输层和应用层,接收接口功能上总体可视为发送接口的逆过程,其结构框图如图1所示。

图1 JESD204B发送和接收接口框架

物理层为高速串行信号的发送和接收提供底层通路。本文中物理层采用Xilinx公司的高速收发器实现。

链路层主要实现8B/10B编解码、确定发送/接收规则、链接操作等功能。串化之后,8B/10B码组中最左端的比特位最先被发送。链接操作主要包括码组同步、SYNC~信号组合、初始化帧同步、帧队列检测和校准。

JESD204B发送和接收装置支持数据扰频。每个通道有一个扰频器和解扰频器,其处于传输层和链路层之间。扰频的主要目的是避免当帧之间相同的数据8位组重复时产生光谱尖峰[4]。

传输层将转换采样映射为未经扰频的8位组。将全部采样结果或部分采样结果分成由F个8位组组成的帧。JESD204B允许每个转换器每个帧时钟周期传输多个采样结果。每个转换器每个帧时钟周期传输的采样数必须为整数。每个采样作为N'Byte的组进行传输,这个N'Byte的组包含N Byte数据、可选择的控制位以及可选择的尾位。帧结尾处额外的尾位用于填满每通道每帧周期的整批8位组。

2 JESD204B接口实现

协议的实现主要是完成对数据的组帧(或解帧)、编码(或解码)。物理层完成了数据在线路上的传输,可直接使用GTX高速收发器实现。发送接口作为发送端,接收接口作为接收端。GTX接口内嵌了8B/10B编解码模块和控制字符检测模块,可方便地实现与JESD204B标准设备的对接。在FPGA中基于GTX实现JESD204B协议,其难点主要有GTX时钟的配置,以及对协议据帧的解析。另外,发送接口电路总体上是接收接口电路的逆过程。因此,这里主要介绍接收接口电路的实现要点。

2.1 GTX时钟配置

考虑到今后项目需要,假定所设计的接收接口对应的目标A/D输出位宽为14位,采样率为250 MSample·s-1。根据JESD204B协议,其14位A/D采样数据需经低2位补0后,以16 bit数据组成一帧(frame),如图2所示。

图2 JESD204B数据帧格式

组帧后数据经8B/10B编码,变为20 bit,将编码后的比特流送入接收端,由接收端完成8B/10B解码以及对JESD204B协议的解析[4]。由于采样时钟为250 MHz,故经添加尾位及8B/10B编码后,各部分的线速度如表1所示。

表1 GTX线速度

设计过程中需根据所用FPGA芯片的速度范围、外部时钟频率以及GTX内部QPLL/CPLL的FVCO的工作范围,设置合适的CPLL_REFCLK_DIV、CPLL_FB、DIV_45、PLL_FBDIV、TXOUT_DIV、RXOUT_DIV等参数,使GTX稳定工作在5.0 Gbit·s-1[2]。

2.2 协议数据解析

JESD204B字被映射成有效的8B/10B编码字,并以特定规则设为帧和多帧。在此过程中,8B/10B编码结合控制字符可带来串行数据链路方面的优势,这些控制字符具备执行各种通路对齐功能的能力。8B/10B编码中主要有5个控制字符,可为JESD204B数据流实现各种功能。这些字符为/K/、/F/、/A/、/R/和/Q/。

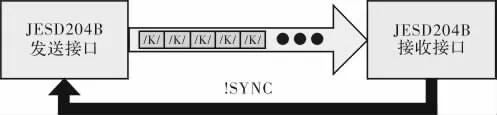

/K/=/K28.5/控制字符通过同步接口用于代码组同步(通过置位!SYNC)。接收器发出同步请求后,发射器就开始发出/K/=/K28.5/字符。接收器同步,并等待至少4个连续的/K/=/K28.5/字符。然后,接收器取消其同步请求。该过程按照操作子类要求执行。对于子类0,接收器在收到4个连续的/K/=/K28.5/字符之后,取消任何帧边界上的同步请求。对于子类1和子类2(有确定性延迟,分别为SYSREF或!SYNC),接收器在收到4个连续的/K/=/K28.5/字符之后,取消任何局部多帧时钟边界上的同步请求。

图3 /K/控制字符

/A/=/K28.3/控制字符用于串行数据流中的多帧对齐。由发射器在特定条件下插入多帧末尾。这种情况下,当多帧末尾的当前帧的最后8位字等于上一帧的最后8位字时,该8位字将被一个/A/=/K28.3/字符取代。即使上一帧的最后8位字是一个控制字符,也会被取代。

/R/=/K28.0/控制字符用于指示多帧的开始。如果发射器发射一个初始通道对齐序列,则/R/=/K28.0/将是发出的第一个非/K28.5/字符。在初始通道对齐序列期间,发射器将始终发射一个/R/=/K28.0/字符以指示多帧的开始,发射一个/A/=/K28.3/字符以指示多帧的结束。

/Q/=/K28.4/控制字符用在初始通路对齐序列中,用于提示接收器,配置数据即将开始。必须记住,这个特定的控制字符只用于初始通路对齐序列中,而不用在数据传输的任何其他阶段。

图4 /R/、/A/、/Q/控制字符

/F/=/K28.7/控制字符用于串行数据流中的帧对齐。该字符由发射器在特定条件下插入帧末尾。当前帧的最后8位字(不是多帧的最后8位字)等于上一帧的最后8位字时,该8位字将被一个/F/=/K28.7/字符取代。然而,若上一帧的最后8位字为一个/F/=/K28.7/字符,则当前8位字不会被取代。

图5 /F/和/A/控制字符——帧和多帧对齐

所有这些控制字符(/K/、/F/、/A/、/R/和/Q/)都在表2中与其10位二进制表达式一并列出。每个控制字符均对应两个10位二进制表达式,从而确保了数据传输的直流平衡,以及接口的交流耦合。这与8b/10b数据字中同样存在DC平衡的数据是一致的。该方案符合IEEE 802.3中的8b/10b编码规范。

表2 8B/10B控制字符

3 实验结果及分析

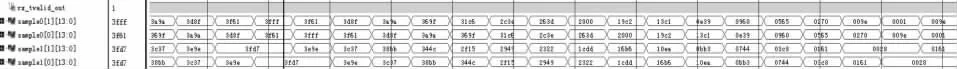

为验证所设计的传输接口的逻辑功能,文中在Xilinx的开发工具Vivado下对设计的接口电路进行了逻辑功能仿真。所设计的JESD204B传输接口用到了2个GTX高速串行收发器,收发器的传输速率设置为5 Gbit·s-1,每个Lane的数据缓存位宽为32 bit,待传输的测试数据设计为14 bit的正弦信号。由于设计的JESD204B传输接口采用了2 Lanes,每个Lanes的数据缓存位宽为32 bit,故接收端经帧解析及8B/10B解码后得到的数据实际为64 bit。这64 bit数据中包含了4个原始的并行采集数据,为了便于与接收端解析到的数据比较,这里将原始的测试数据也拆分成了4路,得到的是4路分辨率较低的正弦波,其数值如图6所示。接收端解析出的数据中,sample0[0]、sample1[0]信号对应于Lane0接收到的数据,sample0[1]、sample1[1]信号对应于Lane1接收到的数据,且sampleL[0]对应于Lane L的低16 bit数据,sampleL[1]对应于Lane L的高16 bit数据。因此,这4路数据的相位顺序从前往后依次为sample0[0]、sample1[0]、sample0[1]、sample1[1]。

图7为接收端解析出的数据。数据数值与传输前的测试数据数值一致,中间一段数据数值按sample0[0]、sample1[0]、sample0[1]、sample1[1]的顺序依次递减,可见其相位顺序亦与分析的一致。经仿真测试,可认为本设计实现了基于JESD204B协议的数据传输功能。

图6 传输前原始数据

图7 接收端解析出的数据

4 结束语

高速数据采集在生活、科研等众多领域具有重要的地位,传统的A/D采集数据并行传输在降低码间同步及串扰、布线复杂度、占用资源等方面陷于瓶颈状态。鉴于此,笔者研究了基于JESD204B协议的数据传输接口设计,并对设计结果进行了仿真测试。经仿真验证,该并行数据串行传输接口及对串行数据解串接口逻辑功能正确。该设计的初衷是为解决A/D采集项目中PCB布线复杂及码间同步的问题,但其应用并不局限于此。如引言部分提到的,当数据传输的误码率成为关注的焦点时,可在传输的串行比特流中插入纠错码,减小误码率。

[1]Xilinx.LogiCORE IP 7 series FPGAs transceivers wizard v3.4[M].USA:Xilinx,2014.

[2]Xilinx.7 Series FPGAs GTX/GTH Transceivers[M].USA:Xilinx,2014.

[3]Xilinx.Logicore IP JESD204 v2.1 user guide[M].USA:Xilinx,2012.

[4]JEDEC.Serial interface for data converters JESD204B.01[S].USA:JEDEC.2011.

[5]Xilinx.Xilinx 7 series FPGAs configurable logic block user guide[M].USA:Xilinx,2014.

[6] 张峰,王战江.基于JESD204协议的A/D采样数据高速串行传输[J].电讯技术,2014,54(2):174-177.

[7] 徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2012.

[8] 冉焱,席鹏飞.基于JESD204协议的高速串行采集系统[J].电子科技,2015,28(5):17-19.