任意分频器的DDS实现方法

2015-04-23范瑞林

范瑞林

(中国人民解放军驻十一所军事代表室,北京100012)

1 引言

随着科技日新月异的发展,人们对时间的要求也逐渐提高,特别是军事应用、外空探索工作的开展,需要高精度、高稳定度的频率源,而且需求从单一的时间频率源发展到多个标准源的同时使用。

在实际的生产和研发工作中,已经具有同时产生多种标准频率源的应用设计,但大多采用直接的模拟分路或简单计数器进行数字分频,如遇到偶数分频、奇数分频、半整数分频等,通过计数器或计数器的级联构成各种形式的偶数分频和奇数分频[1]。本文重点阐述基于全数字DDS合成技术的任意分频器,实现频率准确率高,占宽比准确的多个标准频率源同时产生的新技术。

2 传统分频器原理

2.1 传统分频基本原理

所谓分频,就是把一个晶振或参考源信号的频率变成成倍数地低于输入频率的输出信号,如图1所示。

图1 传统分频器原理

传统分频器的基本原理:首先对计数器进行复位和置位操作,对于不同的输出频率其置位的值不同。公式如下:

式(1)中:fIN为参考频率源,fOUT为分频输出,N为计数器权值。fIN为参考频率源为晶振或外部时钟设备;为计数器权值是通过外部控制器对分频器的计数器进行置位得到。计数器的权值不同得到的fOUT为分频输出不同,在实际应用中,同时需要多个频率源输出时,就需要进行多个计数器的置位,进而得到不同的频率输出。

把输入的参考频率源作为计数器的驱动输入端,在参考源脉冲的驱动下,计数器按照一定规律进行脉冲计数,对不同端口输出的信号脉冲,就可以看作是对输入信号的分频。

至于分频频率是多少,由选用的计数器的权值所决定。如果是十进制的计数器那频率输出结果就是十分频,如果是二进制的计数器那频率输出结果就是二分频,还有四进制、八进制、十六进制等等。以此类类推,在资源和条件许可的情况,可以实现任意整数倍的分频。

2.2 传统分频占宽比

由于传统分频器是采用计数器实现频率分频。其脉冲的占宽比主要靠传统的D触发器进行控制,D触发器随着计数器的状态变化而进行翻转。当计数器权值是2的倍数或2的n次方幂时,其占宽比为1∶1,但对于任意整数的分频器,其但占空比大多不是1∶1,对于占宽比不是1∶1的情况时,其计数器权值 越大,占宽比越接近理想的1∶1。

3 基于DDS的任意分频

现代技术的发展,大规模超大规模可编程逻辑器件随着深入应用,以其低廉的价格及灵活的应用、全新的设计方式、丰富的功能等特点全面应用于电子设计中。基于DDS(直接数字频率合成技术)的任意分频实现方法是采用大规模可编程器件实现。

3.1 可编程器件

在当今数字发展爆炸的时代,现场可编程门阵列(FPGA)器件在电子行业中是一颗闪亮的明星,这是一种正在不断采用新的半导体制造工艺,逻辑容量不断增加,应用领域不断拓展,器件成本不断下降的器件,随着相应开发软件和方法不断的进步,呈现出一个盘古开天时期的景象。

FPGA它是作为专用集成电路领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。它的出现,可以替代几十甚至上百块通用IC芯片。这种芯片具有可编程和实现方案容易改动等特点。

由于FPGA芯片自身的特点,因而在可编程门阵列芯片及外围电路保持不动的情况下,换一块EPROM芯片,就能实现一种新的功能。它具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及实时在检验等优点。

3.2 基于DDS的任意分频原理

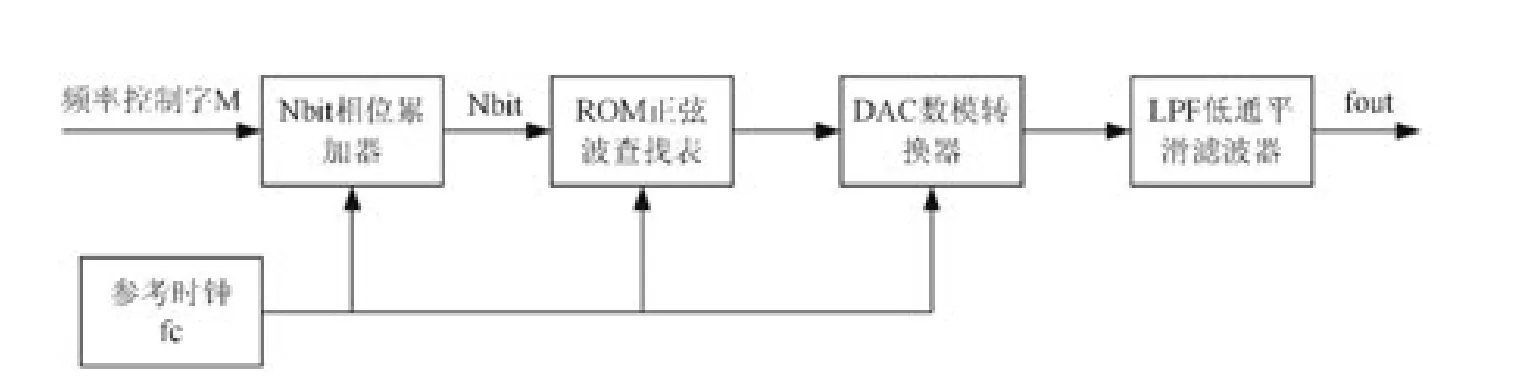

DDS(直接数字频率合成技术)技术基本原理是利用全新的FPGA现场可编程门阵列数字器件,通过循环查表法产生所需要的任意频率的脉冲波形。DDS的基本结构电路原理可用图2表示。

图2 DDS原理

DDS方程如下:

其中:fOUT为DDS输出频率;fc为系统参考时钟;M为频率控制字;N为相位累加器位宽;

直接数字频率合成(DDS)是采用全数字化技术,通过改变不同的频率控制字M,产生各种不同频率、不同波形信号的一种频率合成方法,它主要由相位累加器、ROM表、数模转换器和低通滤波器构成。

3.3 基于DDS的任意分频实现

3.3.1 硬件实现

FPGA的应用不仅使得数字电路系统的设计非常方便,并且还大大缩减了系统的研制周期,缩小了数字电路系统的整体体积和所使用芯片的品种,而且,目前一些主流FPGA的时钟频率已可达数百MHz,加上它的灵活性、可编程以及强大的EDA软件的支持,非常适合用于多种频率同时产生的数字电路部分。系统设计框图如下。

图3 任意分频器原理

图3为任意分频器原理框图,系统工作时,在外部时钟的驱动下,对频率控制字进行相位累加,进行处理以得到相应的相位码,然后由相位码寻址波形存储器进行相位码―幅度编码变换,再经过D/A数模变换器得到相应的阶梯波,最后经过低通滤波器对阶梯波进行平滑处理即可得到由频率控制字决定的频率可调的输出波形。通过数据接口调整不同的频率控制字,即可得到不同频率的参考波形,实现任意分频。

本系统采用的 FPGA是 Altera公司的EP2C70F672C8芯片,具有丰富的存储器和嵌入式乘法器,这些内嵌的存储器使我们在设计硬件电路时省去了外部存储器。

3.3.2 DDS 核心代码

3.3.3 试验分析

输入参考频率源采用200MHz参考时钟的DDS分频器,任意分频器输出的频率为10MHz。以下实验结果取自泰克数字存储示波器TDS2022B的显示界面照片(图4)。

3.4 基于DDS的任意分频器性能分析

3.4.1 频率分辨率极高

在本设计中,输入参考频率源采用200MHz,计数器为32位计数器,则输出频率为:

公式3中FCW为频率控制字,当FCW=1时,即可得到频率分辨率,由公式(3)得:

故其频率分辨率为0.046Hz。从上面可以看出,只要增加相位累加器的位数N即可获得任意小的频率分辨率。

图4 实际调试波形

3.4.2 频率转换时间短

由DDS工作原理可知,在启动DDS任意分频器工作后,整个DDS系统在系统时钟的驱动下进行工作,只需经过一个系统时钟周期之后即可按照新的频率控制字进行相位累加。当fc=200MHz时钟,其转换时间越为5纳秒。如果提高系统时钟,其转换时间还可缩小,能够满足实际工作中的任何需要。

4 结语

任意分频器的DDS实现新方法采用全数字实现方式,产生的波形可以随意选择,只需更新FPGA中的ROM表即可;易于实现、功耗低、可靠性高,极其方便使用者的需要,易于程控、使用相当灵活,因此性价比极高。

[1]许文建,陈洪波,李 晓.利用Verilog_HDL实现基于FPGA的分频方法[EB/OL].[2007-11-20].http://www.poper edu.cn/releasepaper/content/200711-381.

[2]付慧生.复杂可编程逻辑器件与应用设计[M].北京:中国矿业大学出版社,2003.

[3]王伦发,安桂生,龚享铱.基于直接数字频率合成器(DDS)的驯钟实现新方法[C]//中国电机工程学会.2013年会论文集.北京:中国电机工程学会,2013.