达芬奇异构多核处理器核间通信技术研究

2015-04-10国常义李超群

国常义,李超群,刘 峰

(南京邮电大学 图像处理与图像通信江苏省重点实验室,江苏 南京 210003)

达芬奇异构多核处理器核间通信技术研究

国常义,李超群,刘 峰

(南京邮电大学 图像处理与图像通信江苏省重点实验室,江苏 南京 210003)

针对目前通用的达芬奇异构多核处理器,研究了其ARM核、DSP核以及视频协处理器之间的通信与协作机制。在分析多核处理器核间通信原理的基础上,研究了TMS320DM816x系列达芬奇异构多核处理器的核间通信技术,详细阐述片上核间互联结构与核间通信软件的实现。最后基于SysLink底层通信模块设计了多路高清音视频应用系统,对核间通信进行验证。系统可充分发挥各处理核的性能,实现了各核间的高效协作。

异构多核;核间通信;SysLink;TMS320DM816x

随着信息技术的发展与需求的提升,传统单核SOC不能满足人们的需求,市面上出现越来越多的嵌入式多核处理器。嵌入式多核处理器主要分两类:第一类是同构多核,如联发科MTK6592集成8颗Cortex-A7核;另一类是异构多核,如德州仪器(TI)的达芬奇与OMAP系列的ARM+DSP系列处理器。异构多核处理器集成结构、性能不同的多个核心,可发挥各核所长,实现资源的最佳配置,能够很好地提升系统整体性能、降低功耗。但是,多核处理器性能的发挥离不开核间的通信与协作,因此处理器核间的通信技术至关重要。

达芬奇技术是TI专为数字图像、视频、音频信号处理设计的平台,包括达芬奇处理器、开发环境、算法库和其他技术支持等[1]。TI为用户提供ARM+视频协处理器、ARM+DSP、ARM+DSP+视频协处理器等不同架构的达芬奇处理器。文章基于达芬奇异构多核处理器,研究片上多个处理器核的互联结构及核间通信的实现,并介绍了底层核间通信软件的实现。最后,基于底层核间通信模块SysLink实现了不同核之间的任务通信与算法调用,通过系统高效的核间协作与通信,完成多路高清视频采集、编码、处理、传输、显示以及音频编码的软件框架。

1 异构多核间通信的基本原理

本文主要基于TMS320DM816x(以下简称DM816x)系列达芬奇异构多核处理器进行研究。DM816x集成ARM Cortex-A8核、C674x DSP核、高清视频/图像协处理器(HDVICP2)、高清视频处理子系统(HDVPSS)以及SGX530图形加速器。HDVICP2由基于ARM968内核的Video M3核管理,可完成H.264、MPEG-4、MJPEG编解码;HDVPSS由VPSS M3核管理,具有2路高清视频捕获通道及显示通道。

异构多核处理器大多采用主从式的结构。主从式结构根据不同核的功能把处理器核分为主核和从核。主核的结构和功能一般较为复杂,负责全局资源、任务的管理和调度并完成从核的引导加载。从核主要接受主核的管理,负责运行主核分配的任务,并具有本地任务调度与管理功能[2]。在多核处理器中,根据不同核的结构,各个核可运行相同或不同的操作系统。在DM816x中ARM为主核、DSP和协处理器为从核,ARM核运行开源的Linux系统,DSP核和M3核运行TI为其DSP设计的SYS/BIOS实时内核。

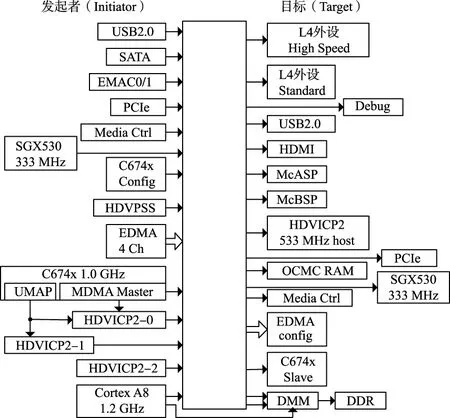

主从式的异构多核处理器核间的互联结构如图1所示。

图1 主从式异构多核互联结构

从图1可知,为了实现异构多核之间的通信,在芯片内设计了核间中断控制器以及核间互联的总线。核间中断是多核间任务同步与通信的桥梁,核间中断寄存器各标志位分配给芯片内不同的核,通过核间中断向另一个核发送中断请求,执行相应的中断服务程序或通过中断寄存器传递地址,配合共享内存实现数据的传递与共享。各个核心对于外设的访问则通过配置总线等实现。

综上,实现各个处理器核有效的管理和通信需要具备以下功能:

1)主处理器对从处理器进行管理;

2)内部处理器之间信息的传输和交换。

前者可通过片上互联实现,后者则由核间中断和内存共享来实现。下面将以DM816x为例详细说明上述功能的实现。

1.1 核间中断

为了实现高效的片上核间通信,DM816x系列达芬奇处理器片上集成硬件邮箱中断(Mailbox Interrupts)和自旋锁(Spinlocks)。DM816x有12个邮箱,每个邮箱有4个中断源以向4个核发送中断,并且提供4个消息深度的FIFO,每个消息32位宽。每个邮箱都可以由任意一个核读写,通过相应的寄存器设置中断发送者以及接收者,通过消息寄存器传递消息[3]。ARM、DSP和2个M3媒体控制器之间通过系统级的邮箱进行通信,每个HDVICP2有各自独立的邮箱,可以向自身内部模块和其他核发送中断。

1.2 片上互联与内存映射

共享内存的实现首先需要系统对内存进行合理的映射与管理。每个子系统或处理器都有自己的内存和内存映射寄存器,为了简化软件的开发,DM816x使用统一的映射,映射到L3的4 Gbyte的空间,从而使得芯片资源具有一致性。

DM816x使用分层架构(L3,L4)的互连技术,将多处理器和子系统连接到一起。L3基于可扩展性、高带宽、低成本的片上网络(NoC)技术实现高效互联,NoC使用一个内部基于包的通信规程[4],由发起者(Initiator)向目标(Target)请求并返回数据。L3的互联结构如图2所示。

图2 L3互联概貌

图2中箭头表示Master/Slave(或者Initiator/Target)关系。发起者向目标通过L3总线请求并返回数据,实现处理器中多个核之间、核与外设间的连接。

在上述连接中,ARM cortex A8的高2 Gbyte地址空间由一个特殊的端口master0 直接连接到DMM(动态内存管理),以实现低延时访问DDR;低2 Gbyte物理地址连接到L3,再通过DMM端口(128 bit宽)存取DDR,直接通过L3互连端口(64 bit)存取芯片的其他模块。

DSP内部采用物理地址,DSP有1个独立的CFG配置总线用来访问L4外设,并且提供1个主接口和从接口连接到L3,以及3个主端口以供直接访问HDVICP2子系统。DSP访问外部的存储通过MDMA(Master DMA)存取,并由DEMMU(DSP/EDMA内存管理单元)进行地址翻译,DEMMU将地址翻译成系统物理地址,并保护ARM的内存区不被DSP代码修改,并允许在用户空间分配缓冲区,而不需要在ARM和DSP之间进行地址翻译,以实现用户分配的缓冲区在ARM与DSP之间共享[3]。

HDVPSS包括1个第33位地址位,用于附加的4 Gbyte地址范围,用作虚拟寻址和非物理内存寻址,用于目标地址空间的定位。

L4连接到外设,提供处理器对外设的访问,这里不做详述。

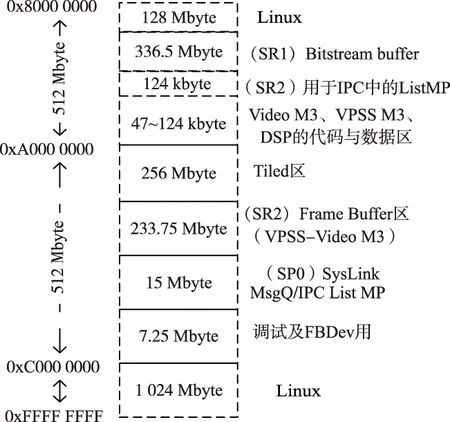

1.3 共享内存

DM816x中运行Linux和SYS/BIOS两套操作系统,它们分别采用makefile机制与XDC构建系统。Linux在运行时通过内核启动参数来配置由内核管理的内存空间,SYS/BIOS在构建时采用XDC配置文件进行数据区、代码区等内存区的分配。系统构建与运行时需要对各个核所使用的内存以及共享内存进行划分。使用2 Gbyte内存时,典型的内存配置及其作用如图3所示。

图3 内存分配

图3中SR0-3作为共享内存,可供不同处理器共享使用,为了实现共享资源的互斥访问,芯片集成硬件自旋锁,以解决多核间共享资源的访问互斥问题。

2 异构多核间任务通信的实现

异构多核处理器实现高效的核间通信与协作,不仅需要片上硬件模块的支持,还需要在软件中提供任务间通信的机制。Linux和SYS/BIOS都提供了本操作系统上进程通信的机制,在Linux中有管道、消息队列、信号量、共享内存等任务间同步与互斥的方式,SYS/BIOS中提供了处理器间通信的IPC(Inter-Processor Communication)模块。IPC模块为单核或多核处理器提供核间任务的通信,实现了Notify、MessageQ、ListMP等单核或核间任务通信的机制。

下面首先研究IPC模块在多核架构中的实现,然后介绍SYS/BIOS与Linux之间任务通信的实现。

2.1 IPC模块的实现

IPC模块包含处理器名称及ID管理模块、内存管理模块以及进程间通信模块。常用的模块的实现及其功能如下:

Notify:使用Notify驱动核间中断来实现进程间通信的通知功能。传输的数据一般为32位,可以为事件动态注册处理函数。

GateMP:使用硬件自旋锁实现共享资源的互斥访问。

SharedRegion:负责共享资源的虚拟地址空间和本地处理器地址空间的转换。同一片共享内存在不同处理器上映射的地址可能不同,此模块创建共享区域的查询表,记录在不同处理器中该共享区域的地址。

ListMP模块:在处理器间共享链表。ListMP是一个双向链表,它使用SharedRegion的查找表管理共享内存,使用GateMP解决多任务同时访问一个资源的互斥。

Heap*MP模块:基于SharedRegion模块,实现动态内存分配。

MessageQ:采用上述各模块,提供可变长结构化消息队列通信机制。

另外还有对各个核进行唯一ID管理的MultiProc,对处理器名称管理的NameSever模块等。

2.2 底层通信模块SysLink的实现

运行SYS/BIOS系统的处理器间可以通过IPC模块完成核间的通信,而运行Linux的ARM要想与之通信则需要提供类似的IPC模块,为了简化程序的开发,采用SysLink底层通信模块来实现ARM与其他处理器核的通信。

SysLink是一套软件与相关工具的集合,为运行在ARM上的Linux和运行在其他处理器核上的RTOS提供统一的进程间通信的接口[5]。在ARM侧SysLink作为内核驱动,可以在Linux用户空间方便操作核间中断、自旋锁等硬件;在DSP侧SysLink基于IPC模块进行封装,供开发者使用。

SysLink使用户应用程序不用关心进程间的通信是在同一个处理器核上还是在不同的处理器核上,而视频数据的共享与核间传递则采用共享内存的方式实现。DM816x基于SysLink的软件设计架构如图4所示。

图4 基于SysLink的软件框架

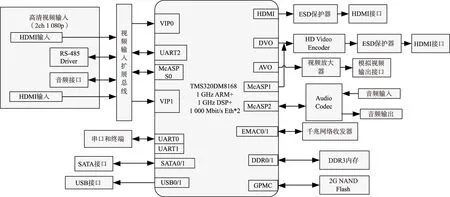

3 核间通信的验证与实验结果

为了验证上述基于SysLink/IPC底层通信模块的高效性,设计了一个多路高清音视频采集、编码、传输系统。系统硬件设计框图如图5所示。

系统采用DVRRDK软件包进行开发,DVRRDK将运行在各个核上的线程统一为Link结构,一个Link即为具有一定功能的线程及相关数据结构的组合,每个Link都有一个唯一的ID,可以有一个或多个输入队列和输出队列以及Notify机制通知新数据是否准备好,并通过prevId和nextId与该Link之前的preLink和之后的nextLink进行连接形成一个数据链,而Link中的各个线程则通过MessageQ、信号量等线程通信机制进行同步与互斥,对于视频数据则通过核间共享内存避免了数据的转移,实现了高效的核间数据共享。

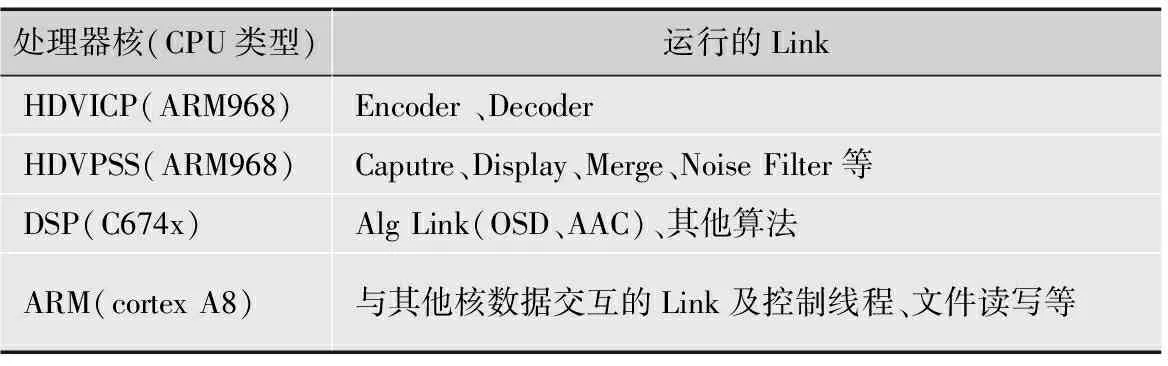

运行在各个处理器核中的Link如表1所示。

图5 高清音视频系统框图

表1 系统中主要Link分配

处理器核(CPU类型)运行的LinkHDVICP(ARM968)Encoder、DecoderHDVPSS(ARM968)Caputre、Display、Merge、NoiseFilter等DSP(C674x)AlgLink(OSD、AAC)、其他算法ARM(cortexA8)与其他核数据交互的Link及控制线程、文件读写等

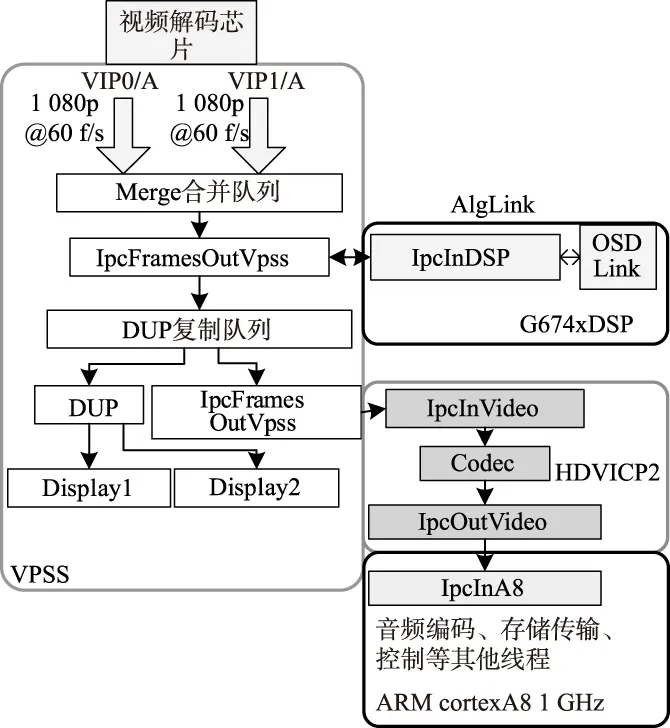

在多路视音频应用中通过HDVPSS驱动视频AD采集视频数据[6],然后将2路高清视频数据经过Merge Link合并成一个输出队列,由DSP完成视频数据的OSD叠加处理,视频数据流进入Dup Link复用形成两个输出队列分别送往Display Link和Encoder Link,同时ARM将Encoder Link送来的数据进行存储或传输。音频数据则采用ALSA框架进行音频采集,然后送往DSP进行编码,再由ARM进行存储、传输。系统中的数据链路图如图6所示。

图6 系统数据链路图

系统在ARM核的控制下,完成2路1 080p@60 f/s(帧/秒)视频的采集并处理,由DSP完成图片、文本等信息的OSD叠加,同时由Video M3完成2路视频的实时H.264 High Profile编码,并通过ARM进行音视频的存储和网络传输。系统中各核之间高效协作,完成了在单核甚至多核ARM或DSP中难以完成的任务。

5 总结

本文研究了嵌入式异构多核处理器中各个处理核间的通信与协作机制,以达芬奇系列高性能处理器DM816x为例,从硬件结构到软件框架详细分析了处理核之间任务通信与协作的实现过程,并基于文章所述的多核间通信机制设计了多路高清音视频应用系统,系统在各个处理核的高效协作下,完成了多路高清音视频的采集、编码、处理等任务。

[1]高玉龙.达芬奇技术开发基础、原理与实例[M].北京:电子工业出版社,2012.

[2]蒋建春.异构多核嵌入式软件关键问题研究[D].重庆:重庆大学,2011.

[3]Texas Instruments.TMS320DM816x DaVinci digital video processors technical reference manual[EB/OL].[2014-08-27].http://www.ti.com/lit/ug/sprugx8b/sprugx8b.pdf.

[4]马清勇.片上网络(NoC)互连技术研究[D].成都:电子科技大学,2013.

[5]Texas Instruments.SysLink user guide [EB/OL].[2014-08-21].http://www.ti.com.[6]王帅,刘峰.基于TMS320DM368的高清视频采集系统设计与实现[J].电视技术,2013,37(7):43-45.

国常义(1990— ),硕士生,主研图像处理与多媒体通信;

李超群(1991— ),硕士生,主研图像处理与多媒体通信;

刘 峰(1964— ),博士,教授,博士生导师,主研图像处理与多媒体通信、高速DSP 与嵌入式系统。

责任编辑:闫雯雯

Research on Inter-processor Communication for DaVinci Heterogeneous Multi-core Processors

GUO Changyi, LI Chaoqun, LIU Feng

(JiangsuKeyLaboratoryofImageProcessing&Communication,NanjingUniversityofPostsandTelecommunications,Nanjing210003,China)

The communication mechanism of the cores covering ARM core, DSP core and co-processors in general DaVinci heterogeneous multi-core processors is researched in this paper.The basic principle of inter-processor communication(IPC for short) is analyzed and then the interconnection of cores and the implementation of the IPC software are delivered for TMS320DM816x series DaVinci multi-core processors.Finally, a multi-channel HD video and audio system based on SysLink is developed to verify the IPC.The system is efficient and the IPC works well.

heterogeneous multi-core; inter-processor communication; SysLink; TMS320DM816x

江苏省高校自然科学研究项目(13KJA510004;12KJB510019);广州市软件和信息服务业发展专项资金项目(2060404)

TN915.04

A

10.16280/j.videoe.2015.07.012

2014-09-18

【本文献信息】国常义,李超群,刘峰.达芬奇异构多核处理器核间通信技术研究[J].电视技术,2015,39(7).