纸币清分系统中光电图像实时采集方法

2015-04-10邹连英季辉周莹余尚仁

邹连英,季辉,周莹,余尚仁

武汉工程大学电气信息学院,湖北 武汉 430205

纸币清分系统中光电图像实时采集方法

邹连英,季辉,周莹,余尚仁

武汉工程大学电气信息学院,湖北 武汉 430205

纸币图像实时采集是纸币清分系统自动化工作的首要任务.利用现场可编程门阵列并行控制技术,实现了纸币图像光电转换、模数转换、数据缓存等功能,为纸币清分系统实现真伪辨别、纸币分类、残币识别、冠字号提取等功能提供实时清晰的纸币图像数据.选用三段式多光源接触式图像传感器采集纸币的光感电压信号,经过模数转换电路,每行三段数据同时拼接成一行,每张纸币采集500行,组成一幅完整的纸币图像送到高速存储器进行缓存.经仿真分析与实验板验证,采用本系统进行纸币图像采集可以实现1 min采集约1 382张纸币图像,具有很好的实时采集效果.

纸币清分;接触式图像传感器;实时采集;现场可编程门阵列

0 引言

随着制造技术的飞速发展,假币的制作水平越来越高,并且更加频繁的出现在市面上.为应对日新月异的假币制作技术,纸币的防伪特征数也在不断的增加.早期的验钞机只能辨别纸币的部分防伪特征,并仅辨别纸币的真伪,不能记录所识别的纸币更多信息.纸币清分系统不仅能实现纸币真伪的辨别,同时拥有纸币分类、残币识别、纸币冠字号提取等功能[1].纸币图像实时采集是纸币清分系统自动化工作的首要任务.

本文选用高效的光电传感器采集纸币图像数据,利用现场可编程门阵列(Field Programmable Gate Array,以下简称:FPGA)控制技术实现红、蓝、绿三基色及红外、紫外光照射的纸币图像实时采集.

1 纸币清分系统架构

纸币清分系统的机械结构如图1所示.纸币放入接钞位置时,位置传感器产生系统处理启动脉冲信号,系统从休眠状态进入数据采集处理状态[2].纸币进入采集检测部分,接触式图像传感器(Contact Image Sensor,以下简称:CIS)根据软件预设发出红色、蓝色、绿色或三基色混色光以及红外光、紫外光等对纸币进行光照,光照纸币的反射光经光电转换变成电压信号,经模拟/数字(Analog/Digital,以下简称:A/D)转换芯片将电压模拟信号转换成数字信号并送入FPGA控制芯片进行图像数据组合、重排与保存处理.

图1 纸币清分系统的机械结构图Fig.1 Mechanical structure diagram of banknote sorting system

FPGA控制模块采集到的纸币图像数据保存到外部同步动态随机存储器(Synchronous Dynamic Random Access Memory,以下简称:SDRAM)中,清分系统的后续纸币图像处理工作由数字信号处理器(Digital Signal Processor,以下简称:DSP)模块负责.FPGA采集模块与DSP图像处理模块共用高速SDRAM存储器,实现纸币图像数据的实时采集与高速处理.DSP处理模块的分析结果控制纸币的识别与分钞部分的机械动作.同时,纸币的原始采集图像可通过通用串行总线(Universal Serial Bus,以下简称:USB)接口传送给上位机进行更详细复杂的数据处理与保存[3].

因此,纸币清分系统主要包括:CIS传感器、A/D转换器、FPGA控制器、DSP处理器、SDRAM存储器、USB传输控制等模块,模块之间的关系框图如图2所示.

图2 系统总体设计框图Fig.2 The system architecture

2 光电CIS传感器控制

在纸币图像采集模块,选取合适的图像传感器十分重要.CIS接触式图像光电传感器采用一体化的模组设计,将光源、传感器、放大器集成为一体,具有尺寸小、重量轻、结构紧凑、抗震性能好等特点[4].CIS光电传感器采用单一的+5 V电源供电,功耗低,速度快.本文选用SML2R183NUV型三段式CIS传感器,其截面剖视图如图3所示.

图3 CIS传感器截面剖视图Fig.3 The cross section view of CIS sensor

SML2R183NUV型CIS传感器由发光二极管(Light Emitting Diode,以下简称:LED)光源阵列、微自聚焦棒状透镜阵列、光电传感器阵列及电路板、保护玻璃、接口、外壳等部分组成.LED光源能产生红色、蓝色、绿色及三基色混色光和红外光与紫外光,充分满足纸币防伪特征提取的多种光源需求.

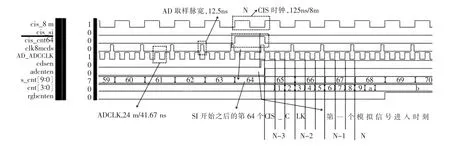

图4是SML2R183NUV型CIS传感器工作时序图.当纸币进入启动系统时,产生的系统唤醒脉冲信号可作为CIS开始工作的行启动控制SI信号.LEDr/g/b/ir/uv分别为红、绿、蓝光以及红外、紫外光的电流驱动信号,由电流驱动芯片输出控制光源的亮灭.本设计选用SCT2007芯片作为电流驱动芯片.当SI信号有效后,打开电流驱动芯片,产生指定的光源照射经过的纸币,被照射的纸币反射光经CIS传感器转换为电压信号SIG1、SIG2、SIG3输出.SIG1、SIG2、SIG3三段是将纸币长度分成三段同时进行扫描,通过并行采集纸币的三个部分,实现图像数据的高速实时采集.

图4 CIS采集时序图Fig.4 The acquisition timing diagram of CIS sensor

一旦行启动信号SI脉冲开始,三段并行信号都要等待63个时钟周期,信号从第64个时钟开始采集并转换成电压信号,第一段信号编号为1-432,第二段信号编号为433-864,第三段信号编号为865-1440.因此,每行有效像素为1440,前两段为432个有效像素,最后一段为576的有效像素.三段图像并行采集过程在CLK时钟信号的上升沿开始转换,在CLK时钟信号的下降沿形成较稳定的电压转换数据.

为实现图4的图像光电转换采集时序,需要FPGA提供精确的时钟节拍信号CLK、行启动信号SI以及SCT2007电流驱动芯片控制信号.这部分的逻辑设计关键是节拍的控制,可通过对时钟信号进行精确计数实现SI、LED信号的跳变时间.图5是CIS传感器的控制逻辑仿真时序图,图中s_cnt信号用来精确计数cis_8 m的时钟节拍,当s_cnt计数到64时,产生cdsen信号激活SCT2007电流驱动芯片开始工作,点亮指定光源.纸币反射光源的光信号在s_cnt等于65时开始转换成电压信号.

图5 CIS数据采集代码仿真波形Fig.5 The simulation waveform of CIS data acquisition

3 多路AD转换接口控制

SML2R183NUV型三段式CIS传感器采集转换的电压信号需要送到A/D转换电路进行模数转换,同时每行三段数据还需要进行数据拼接,重组成一幅正确完整的纸币图像进行缓存,便于后续数据处理算法进行一幅纸币图像数据的处理.SML2R183NUV型CIS传感器的工作频率最高可达8 MHz,且为三段式输出模式.因此,A/D转换器的并行采样时钟必须支持24 MHz或更高的频率.

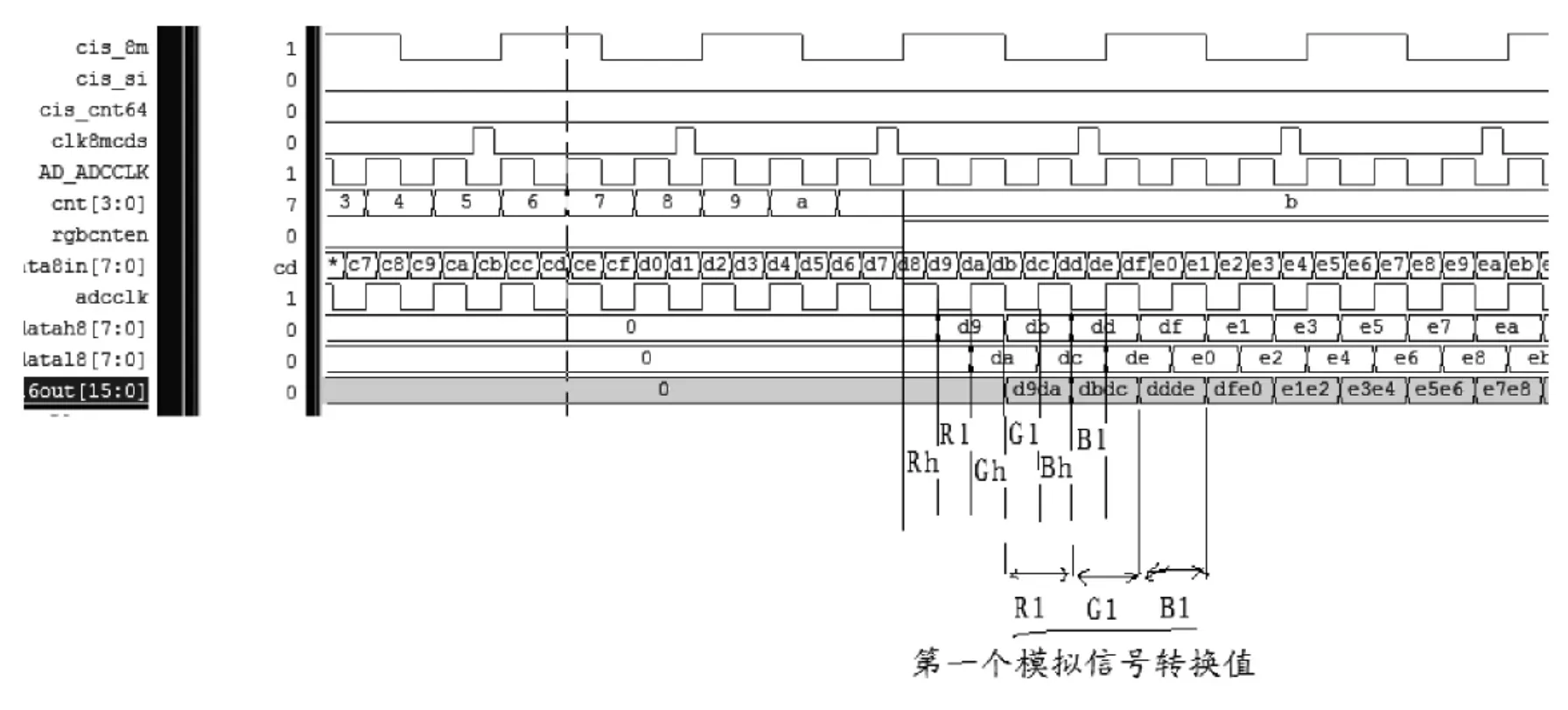

本系统选用HOLTEK公司的HT82V26芯片,最高工作时钟为30 MHz,可以配置选择3通道SHA模式,性能方面完全满足SML2R183NUV型号传感器对图像采集的要求.图6是HT82V26芯片的3通道SHA工作模式时序图.CIS传感器转换的电压信号SIG1/2/3与A/D转换芯片的VINR、VING、VINB模拟信号输入相连.CDSCLK2为8 MHz时钟信号,用来锁定模拟电压信号的电压稳定区间.ADCCLK是转换后的数字信号参考时钟,频率是24 MHz.模拟电压信号经A/D转换后的数字信号分时从D7~D0端送入FPGA控制接口.

图6 A/D转换芯片的3通道SHA模式时序图Fig.6 3-channel SHA mode timing diagram of A/D converter

这部分的控制逻辑主要是产生能锁定模拟电压信号的CDSCLK2时钟信号以及控制转换后数字数据节拍的ADCCLK信号.这两个信号的跳变沿要严格按照图6所示的时序参数要求设计.当第一个模拟信号开始采集时,一行纸币数据被被为R、G、B三段数据,这三段数据同时被A/D采集进入并且转换为数字信号,图7为三段数据按图6时序进行拼接的仿真.

图7 3段A/D数据拼接时序仿真图Fig.7 The joint timing simulation diagram of 3-section A/D data

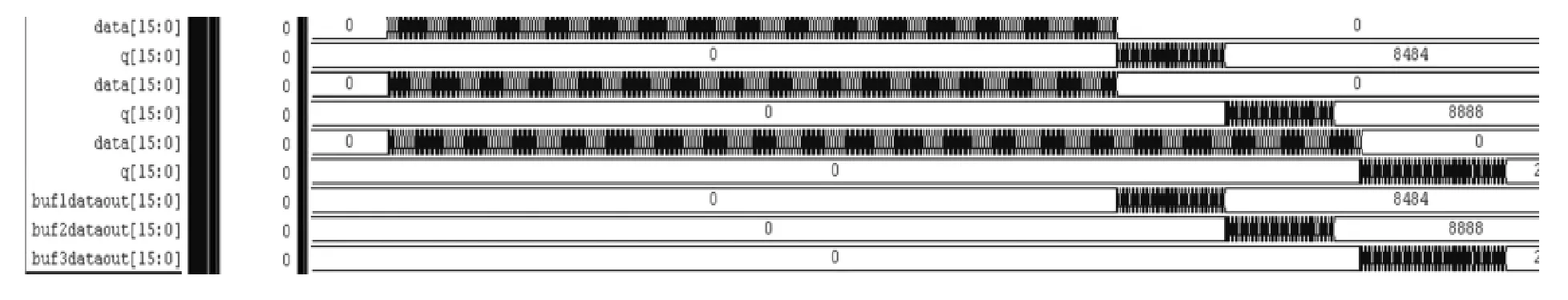

FPGA控制模块在完成了模数转换芯片控制的同时,还需要进行数字信号的数据重组与缓存工作.三段数据根据CIS分段长度分别为432字节、432字节、576字节,在FPGA内部创建3个SRAM缓冲区并行保存这三段数据.在三段数据采集完成后再由SDRAM控制逻辑从3个SRAM缓冲区依次读出每段图像转换数据,图8是3个SRAM分段数据拼接仿真图.

图8 三段SRAM分段数据拼接仿真图Fig.8 The joint timing simulation of 3-section data in SRAM

4 纸币图像采集实时性分析

以第五套100元人民币为例,每张纸币长15.5 cm,宽度7.7 cm.一张纸币图像采集每行1 440像素×500行的数据.CIS采集时序按图4实现.

一行1 440像素分为432、432、576三段,采用并行采集方式,每行正式光照转换在等待64个采样周期后开始,每个像素在一个周期内完成光电转换.CIS采集时钟频率为8 MHz,即周期为0.125μs,取最长一段所需采集时间作为一行的采集时间为:t1=64×0.125μs+576×0.125μs=8μs+72μs=80μs.

CIS采集的每一个像素数据被24 MHz的A/D转换器同时进行模数转换,并存放到FPGA内部的SRAM中,因A/D转换速度刚好是CIS采集速度的3倍,所以在CIS每个像素采集的同时可并行进行A/D模数转换,从图6可以看出转换延时只有3个CIS采样周期,即3×0.125μs=0.375μs.内部SRAM缓存数据由100 MHz的SDRAM控制器读走所需要的时间大约为0.01μs×1 440=14.4 μs.因此CIS采集之后每行数据的重组和缓存时间大约为0.375μs+14.4μs=14.775μs.

由于本系统采用FPGA技术实现CIS采集控制、A/D模数转换控制及SDRAM读写控制,模块之间的数据以并行的方式进行传递,每行数据的重组和缓存时间14.775 μs可在CIS光照等待时间8 μs中并行进行并将行等待适当延长,这样一行1 440像素数据的采集、A/D转换、重组、缓存时间为:t2=14.775μs+72μs=86.775μs.

一张纸币500行数据处理所需时间为t3=86.775μs×500=43 387.5μs≈43.39 ms.1 min能采集处理的纸币数量为N=60 000 ms/43.39 ms≈1 382张.

因此,采用本系统进行纸币图像采集可以实现1 min采集约1 382张纸币图像,具有很好的实时采集效果.

5 结语

采集方法在以CycloneII系列的EP2C35F484C8N芯片为FPGA控制芯片实验板上进行了实物验证,可以采集到清晰的纸币图像数据.

本文选用高效的CIS光电传感器采集纸币图像数据,利用FPGA并行控制技术实现了纸币图像采集与缓存功能,为纸币清分系统实现纸币真伪的辨别、纸币分类、残币识别、纸币冠字号提取等功能提供实时清晰的纸币图像数据.

致谢

国家自然科学基金委员会和湖北省教育厅为本研究提供资金资助,特此感谢!

[1]马继刚.新旧版第五套人民币防伪特征的比较研究[J].中国人民公安大学学报:自然科学版,2006,12(1):46-51.

MA Ji-gang.The security features comparison between new and old version of the fifth set of RMB[J].Journal of Chinese People’s Public Security University:Science and Technology,2006,12(1):46-51.(in Chinese)

[2]宋恩雨.基于CIS传感器的纸币鉴伪与清分系统研究[D].青岛:山东科技大学,2007.

SONG En-yu.Study of paper currency discrimination and sort system based on CIS sensor[D].Qingdao:Shandong University of Science and Technology,2007.(in Chinese)

[3]杨林楠,李红刚,张丽莲,等.基于FPGA的高速多路数据采集系统的设计[J].计算机工程,2007,33(7):246-248.

YANG Lin-nan,LI Hong-gang ZHANG Li-lian,et al.Design of high speed multichannel data gathering system based on FPGA[J].Computer Engineering,2007,33(7):246-248.(in Chinese)

[4]程开富.接触式图像传感器的发展与应用[J].国外电子元器件,2002,20(6):62-65.

CHENG Kai-fu.Development and application of contact image sensor[J].International Electronic Elements,2002,20(6):62-65.(in Chinese)

Real-time acquisition method of photoelectric images in banknote sorting system

ZOU Lian-ying,JI Hui,ZHOU Ying,YU Shang-ren

School of Electrical and Information Engineering,Wuhan Institute of Technology,Wuhan 430205,China

The functions of banknote photoelectric conversion,analog to digital conversion and data cache were performed by field programmable gate array parallel technology.According to the collected images,banknote sorting system can realize authenticity recognition,banknote classification,worn coin distinguish and crown font extraction.The voltage signals of banknote's light-sensing image were acquired with a threesection and multi-source contact image sensor.After analog to digital conversion,three-section data were spliced into one line,and 500 lines were spliced into a image saved in cache.Through the simulation and the experimental verification of banknote image acquisition board,about 1 382 pieces of banknote images are achieved in a minute.It proved that this method has a good effect of real-time acquisition.

banknote sorting system;contact image sensor;real-time acquisition;field programmable gate array

TP391.4

A

10.3969/j.issn.1674-2869.2015.05.013

1674-2869(2015)05-0065-05

本文编辑:苗变

2015-4-30

湖北省教育厅科学技术研究项目(D20131505);国家自然科学基金项目(61271363)

邹连英(1977-),女,湖北黄冈人,副教授,博士.研究方向:FPGA系统开发、嵌入式系统设计.