基于FPGA的数字频率计原理设计与实现

2015-03-27电子科技大学张一鸣

电子科技大学 张一鸣

引言

在电子技术领域内,频率是一个最基本的参数,是指电子器件单位时间内完成周期性变化的次数。因此,为了更好测试器件性能和信号的质量,频率测量就显得尤为重要。随着技术发展,对于频率测量的需求越发显著,测量技术也逐渐提升,市场上出现了具有多功能、高精度、高频率的数字频率计。在实际工程中,我们更加需要符合我们所要求测量精度的频率计。因此,本文提出了一种能满足一般测量精度要求(1Hz-100MHz),并且成本低廉的数字频率计的设计方案。本设计基于Xinl inx公司Spar t an3E系列的XC3S250E芯片,利用硬件描述语言VHDL 完成数字频率计的设计,通过仿真,分析,综合并最终下载到FPGA里面去实现。为了简化设计,我们忽略输入信号处理整形的部分,简化键输入部分,其余功能全部在一片FPGA芯片上实现。整个系统非常精简,而且具有现场可更改性和性能可提升性。

1 数字频率计的测量原理

1.1 频率测量

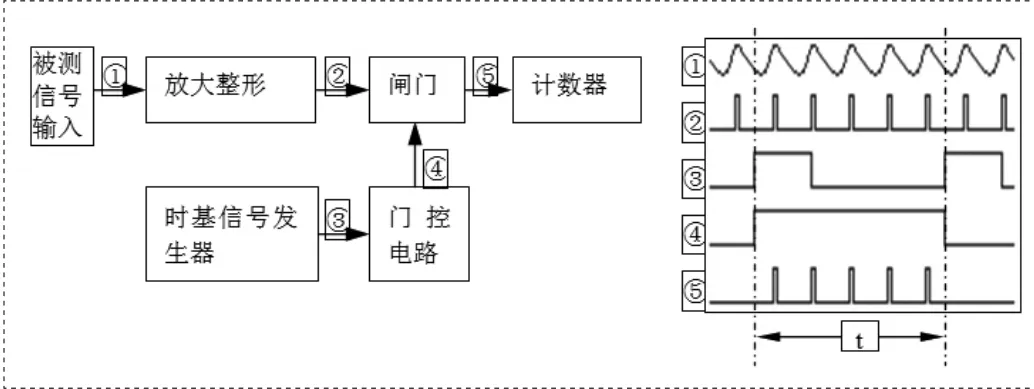

计数式数字频率计常采用直接测频法来测量被测信号的频率,频率计的基本原理利用一个具有高稳定度频率的时基信号对比所测量的输入信号。这里的对比通常指利用时基信号所控制的闸门开计量被测信号。通常情况下,我们计量每秒内待测信号的脉冲个数,此时我们称闸门时间为1S。闸门时间越长,得到的频率值就准确,但会影响频率显示的刷新速率。具体工作原理如图1所示。

首先,把被测信号①(以正弦波为例)通过放大整形模块转变成脉冲②(实际上变成方波即可)整形后方波频率等于被测频率,然后将它加到闸门输入端。门控电路输出信号④来控制闸门开、闭时间。通过十进制数字计数器,我们可以测量在闸门打开时间t内被计数的脉冲⑤的个数。门控信号的作用时间t 是非常准确的,以它作为时间基准(时基),它由时基发生器提供。通过一个高稳定的石英振荡器和数字分频器,我们可以利用输出的标准时间脉冲去控制门控电路形成门控信号。

图1 数字频率计频率测量原理图

1.2 周期测量

同样可以采用直接计数的方法测量被测信号的周期,基本原理是利用被放大整形的输入被测信号作为门控电路信号,控制闸门开闭的时间,计数在闸门打开时间内的时基信号。由于时基信号频率和周期已知,我们便可以推知被测信号的周期和频率。工作原理如下图2所示。

图2 数字频率计周期测量原理图

1.3 量程与精度问题

采用直接技术的方法测量被测信号的频率或周期时,量程和所选的测量精度是相关的。因为本文所采用设计方法中为六位数码管,在一定的闸门时间即测量精度限制下,其量程也有对应的范围。具体量程与精度的关系如图3所示。

图3 数字频率计周期测量量程与精度关系

1.4 数字频率计误差问题

由于本文所采用直接计数法设计数字频率计,其测量频率和测量周期的基础误差包括:时基误差、计数误差及触发误差。其中时基误差指用直接计数法测量被测信号频率或者周期时,因为作为标准量杆的时基信号并不能准确的反应时间基准而产生的误差。这是因为频率基准通常由晶振产生,因此时基误差由晶振决定。当晶振产生的时基信号较真实信号有较大误差时,其测量的频率将产生巨大误差。其次,计数误差指由于闸门与被计数的脉冲不同步即闸门时间不会刚好是被计数的脉冲周期的整数倍而产生的误差。从本质上讲,在闸门打开的时间内,其计数值N表示的是一个把精度量化为1的整数部分,N所没有包括的比值小数部分便成为计数误差。最后,触发误差指的是在实际情况下,由于噪声信号的干扰,会造成触发误差,使整形脉冲的位置发生变化。

综上所示,数字频率计的测量误差一方面取决于闸门时间T打开时间的准确程度,另一方面取决于计数器计数精确程度。根据误差合成方法可知:

对于计数误差,若闸门开启时间为T0而第一个计数脉冲出现在了Tx(如图4所示情况T0>Tx>0的情况(),这时计数器计N个数(图中N=6);现在再来看图4的情况,即趋近于0,我们可以想象又两种可能的计数结果:第一个脉冲和第七个脉冲同时通过闸门,则计数为7。若两个脉冲均未通过闸门则计数为5。因此计数误差为。

图4 计数误差原理图

因此可得:

式中T为闸门打开时间,fx为被测频率。由公式可知,其最大误差总是个计数单位,但是可以通过增加闸门时间T或者测量低频的信号来减少 误差对于频率测量的影响。

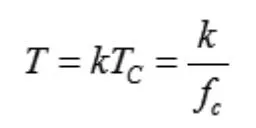

对于时基误差,取决于石英振荡器提供的时基信号频率的准确度来衡量闸门时间是否准确。若石英振荡器的频率为fc,分频系数为k,则:

图5 误差曲线

综上所述,可得如下结论:计数器直接测频的误差主要有两项:即计数误差和时基误差。一般,总误差可采用分项误差绝对值合成,即:

图7 实验板原理图

其合成曲线如图5所示。由图5可知,fx一定时,闸门时间T越长,测量精度越高。当T一定时候,测量频率fx越高,则计数误差越小,测量精度越高。但是随着计数误差的减小,时基误差将对影响测量结果精度,并且以为极限。

图6 设计原理框图

2 数字频率计设计方法

2.1 基本原理及框图

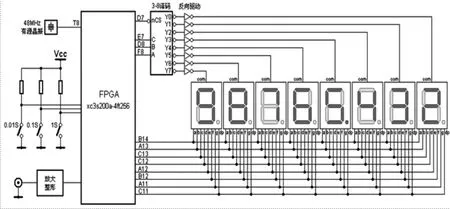

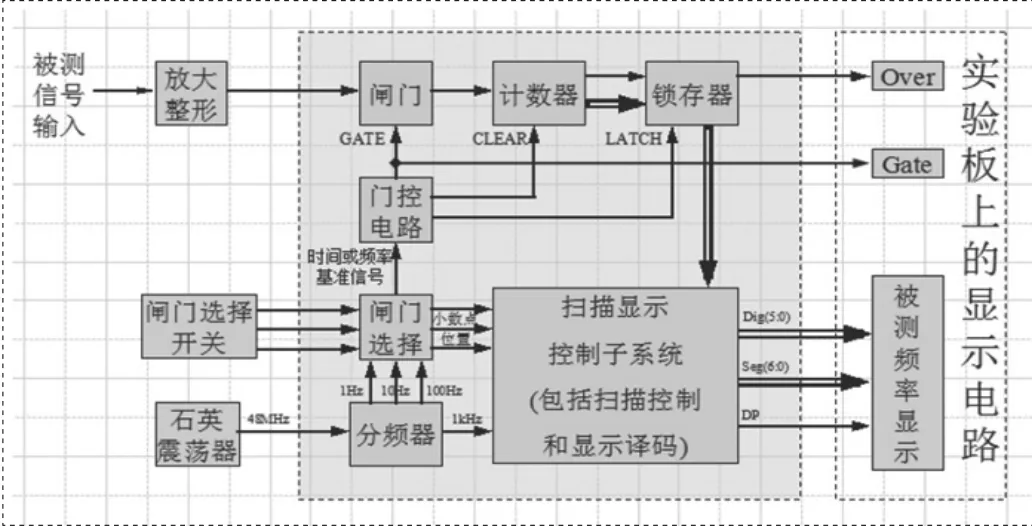

数字频率计的系统结构如图6所示,本设计选择了Xil inx Spar t an3E系列芯片,50MHz有源晶振、两个个发光二极管、三位DIP开关、六位七段数码管。为了满足系统化模块化设计的要求,我们在FPGA芯片中设计了10个模块,它们分别是对被测信号放大整形的模拟电路、由石英振荡器和数字分频器构成的时基信号发生器、3个开关和闸门时间选择电路以及小数点位置选择电路、门控电路、闸门、数据锁存器、扫面显示的控制电路(包括扫面控制和显示译码)、六位数码管扫频显示电路、两只LED指示闸门通断和计数器溢出。结合实际实验板的硬件条件,可以利用EDA软件和VHDL语言在EEC-FPGA实验板上完成频率计的数字部分的设计与实现。实验板原理图如图7所示。

根据基本设计原理框图,可知各部分框图功能,列举如下。放大整形电路:放大被测信号并将其整形为方波脉冲,该方波脉冲经过闸门后送计数器计数。石英振荡器:产生一个频率(50MHz)高度稳定的信号送给分频器分频。分频器:对石英振荡器产生的信号进行分频,得到1000Hz、100Hz 和10Hz三个基准频率;同时1KHz 的信号作为扫描显示译码模块的时钟,以产生扫描选择信号。门控电路:门控电路在时间基准信号的控制下产生10倍基准频率的门控信号GATE,门控信号有效时,闸门开通,计数器计数。当门控信号停止作用时,闸门关断。此时,为了使计数结果能够在显示器上稳定的显示,门控电路要产生一个锁存命令Lat ch 使锁存器锁存计数结果。在计数结果锁存以后,下一次计数开始以前,门控电路还要产生一个清零信号CLEAR 将计数器清零,以便重新计数。

2.2 ISE综合仿真电路图

该频率计利用ISE软件工作平台进行编译和综合仿真后, 将程序下载到FPGA芯片中, 同时在硬件开发平台上进行验证。经实验验证, 该数字频率计达到了设计要求。根据仿真模拟布线结果显示,得出仿真综合电路图如图8所示。

图8 综合仿真电路图

3 结语

本文主要介绍了通过运用VHDL数字逻辑语言,完成基于FPGA的数字频率计的设计与实现。同时阐述了频率计的工作原理,设计方案以及各模块的设计过程及其实现的功能对于信号的数字处理功能;利用硬件设计工具ISE和Model Sim 对方案进行了编译,仿真,分析,综合,并最终下载到FPGA芯片中,达到了频率测量的目的。通过ISE综合,Model Sim仿真,最终在XILINX EDA实验板上实现了1Hz—100MHz频率计数器的设计,其误差在0.01%数量级,能够较为精确的测量频率。在测量频率过程中我们应当选择适当的档位,使得测量结果更加精确,特别是溢出信号LED亮的时候,一定要选择更高档位来进行测量。

总之,本文所设计的基于FPGA芯片的简易数字频率计,具有体积小、重量轻、功耗低等特点并且具有很好的性能和可靠性和设计灵活性。

[1]John F.Wakerly.数字设计原理与实践[M].机械工业出版社.

[2]卢毅,赖杰.VHDL与数字电路设计[M].科学出版社.

[3]侯伯亨,刘凯,顾鑫.VHDL硬件描述语言与数字逻辑电路设计[M].西安电子科技大学出版社.

[4]唐续.现代电子技术综合实验教程[M].电子工业出版社.

[5]张兆莉,蔡永权,王钰.基于FPGA的数字频率计的设计与实现[J].自动化仪表,2006,11(11).

[6]杨守良.基于FPGA的数字频率计的设计和实现[J].电子技术.

[7]Volnei A. Pedroni.VHDL数字电路设计教程.