基于FPGA的继电保护装置内部IRIG-B同步系统

2015-03-15

1 继电保护装置内部同步概况

现代电力系统跨大区联网的实现,使得电力系统的规模越来越大,电网结构愈趋复杂,各种类型的电网故障要求继电保护设备能够快速准确的判断故障并做出相应动作。同时,随着新的保护原理和算法被不断应用,从而使继电保护装置的研究向更高的层次发展,继电保护技术未来趋势是向网络化,智能化,保护、控制、测量和数据通信一体化发展。基于以上背景,以往单一处理器工作的继电保护装置注定无法满足现代化智能电网的高要求,多处理器、多板卡分工协作是当前主流模式。

多板卡的继电保护装置内,各板卡之间需要进行大量的数据交互,信息共享,板卡间的同步对数据测量精度、电力参数计算精度、保护动作实时性有至关重要的影响。目前,多数继电保护装置板卡间的同步主要依赖于处理器的串行接口、CAN通信来实现,但由于嵌入式处理器以及嵌入式操作系统的局限性,其对时精度仅能达到毫秒级。

本文介绍了一种基于FPGA的继电保护装置内部对时系统。FPGA(Field Programmable Gate Array)是现场可编程门阵列的缩写。用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的逻辑。它具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编写程序来修改[1]。

FPGA作为硬件逻辑器件工作,具有极高的实时性,总延时仅包括线路传输延时及几个解码主频时钟周期,能够使得继电保护装置内部对时精度达到纳秒级。

2 IRIG-B概述

IRIG时间编码序列是由美国国防部下属的靶场仪器组(IRIG)提出的并被普遍应用的时间信息传输系统[2]。现广泛应用于军事、商业、工业等诸多领域。IRIG码共有4种并行二进制时间码格式和6种串行二进制时间码格式,串行时间码序列分为A、B、C、D、E、F共6种编码,其中最常见的是IRIG-B时间码格式。其以每秒1次的频率发送包括天、时、分、秒等时间信息[3]。

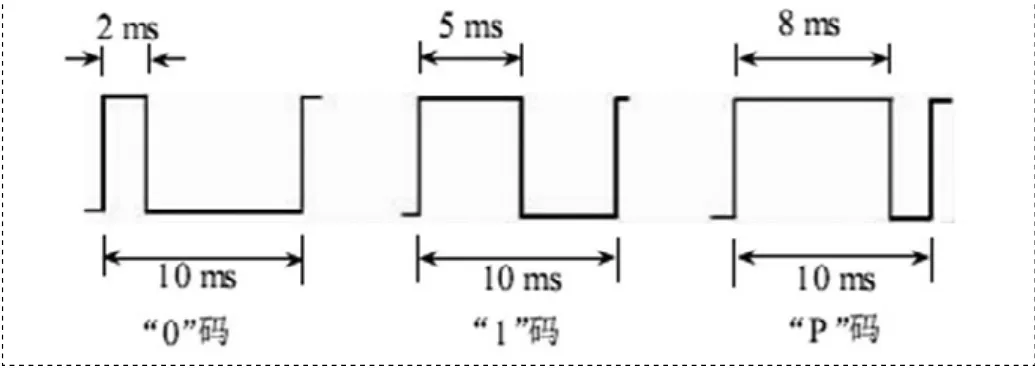

IRIG-B基本码元包括“0”码元、“1”码元和“P”码元,共100个码元,每个码元占用10ms时间。

“0”码元、“1”码元脉冲宽度分别为2ms和5ms,“P”码元为同步码元,脉宽为8ms。码元信息如图1所示:

图1 基本码元信息

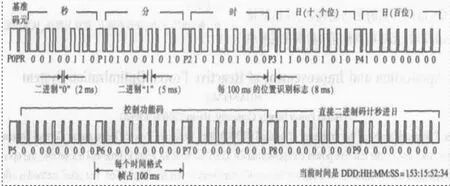

B码以10个基本码元为1组,每组传输一类信息,以P码开头。时分秒信息以十进制编码表示。第1组以连续2个“P”码开始,其中第2个“P”码的上升沿代表整秒时刻,定义为“Pr”,紧跟着的8个基本码元代表秒信息。第2组的第2-8码元传输分信息。接下来的各组码元如图2所示:

图2 IRIG-B码帧格式

3 同步系统的实现

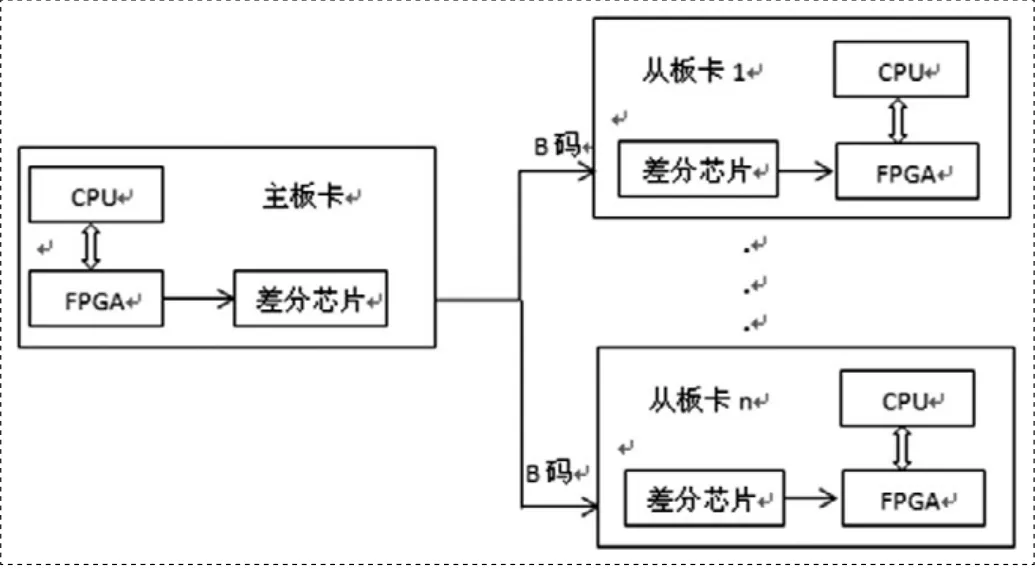

同步系统由主板卡、背板和多个从板卡组成。主板卡主要包括处理器、时间芯片、电池及FPGA,从板卡主要包括处理器及FPGA。首先,主板卡的处理器可以通过外部接口或者SNTP对时来设定时间,包括年月日时分秒,并存储在时间芯片中。当装置断电或者对时丢失时,由时间芯片来完成时间的更新。处理器每秒将当前时间通过数据总线接口写入FPGA寄存器,FPGA读取时间信息,编码成IRIG-B格式通过背板差分总线发送到各个从板卡。从板卡FPGA将IRIG-B码流解码出来,提供到处理器的数据总线上,完成同步。

整个同步系统的框架如图3所示。

图3 同步系统框架

图4 编码模块

本同步系统的FPGA使用Altera公司的Cyclone IV系列的EP4CE10芯片,编程采用VHDL语言。

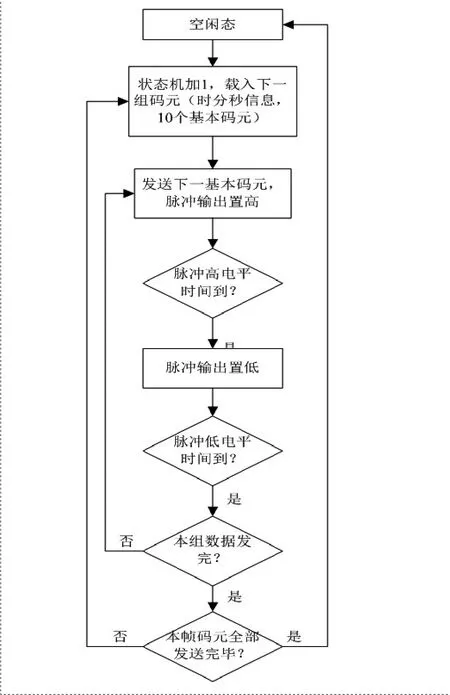

编码模块实现过程介绍如下:

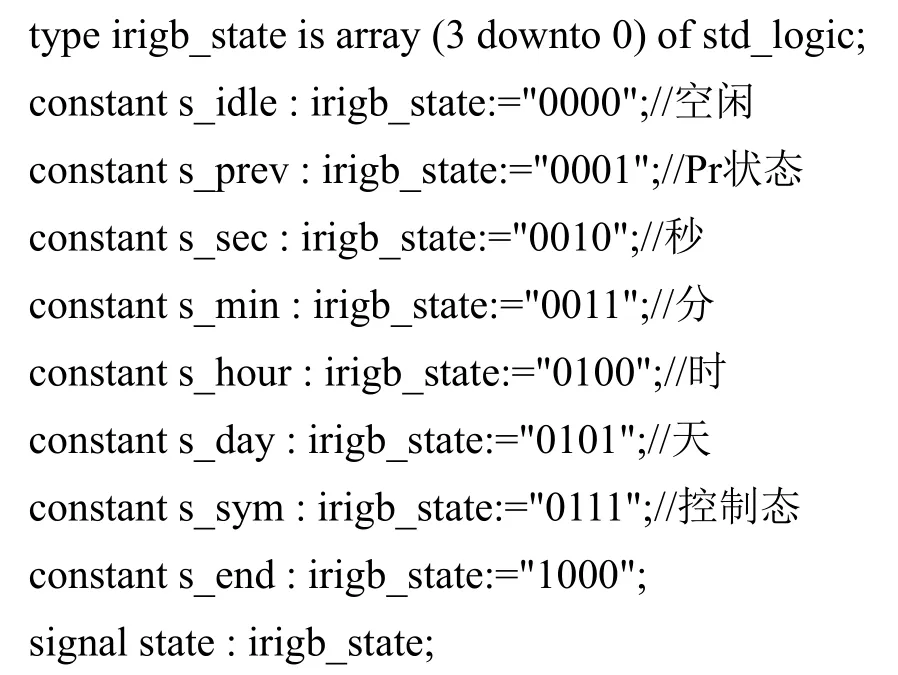

(1)首先定义状态机。

例如,s_prev代表进入“Pr”码编解码状态机,s_sec代表进入秒信息编解码状态机。

图5 解码模块

(2)编码模块的流程(如图4所示)。

根据图1中基本码元信息,首先将输出置为高电平,不同的码元,高电平持续的时间不同,例如“0”码元高电平持续2ms,高电平时间结束后,将输出置为低电平,“0”码元低电平持续时间为8ms。另外,从图2的B码帧格式看到,sec、min、hour这3组分别有10个基本码元,而day组共有30个基本码元,程序每个状态机中会根据本组基本码元数量判断本组码元是否发送完毕。

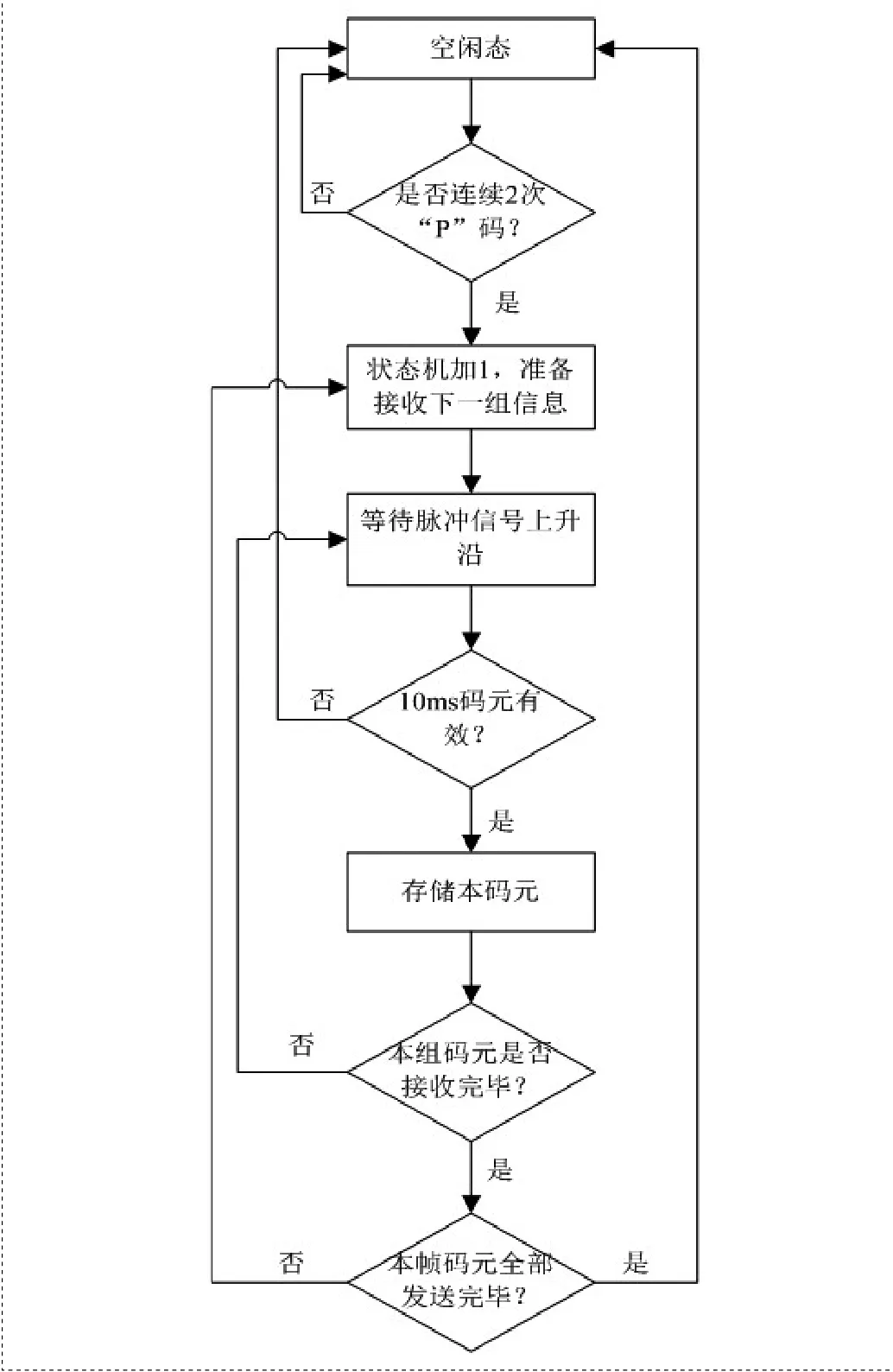

(3)解码模块的实现流程(如图5所示)。

解码逻辑首先检测“Pr”码,即整秒时刻,判断方法是检测连续2次“P”码,接收到“Pr”码之后,即可进入秒信息接收状态机。

判断基本码元有效性的逻辑中,设定高低电平时间的上下限,若码元脉冲高低电平任一值偏出上下限值,即判定该码元无效,同时状态机被复位,等待下一次帧起始,即整秒时刻。

4 结语

通过FPGA实现IRIG-B时间信息的传输,继电保护装置内部板卡间的时间同步精度达到纳秒级,大大提高了板卡间信息交互的同步性和实时性,使得装置处理大量复杂电力数据的能力得到显著提高,是一种高效可行的同步方法。

[1]EDA先锋工作室.Altera FPGA/CPLD设计(基础篇)(第2版)[M].人民邮电出版社,2011,2.

[2]李瑞生,张克元,冯秋芳.电力系统自动化GPS精确对时的方案[J].继电器,1999,27(5):31-32.

[3]周斌,黄国方,等.电力自动化设备,2005年9月.