实验用FPGA运动控制原型系统的设计与实现

2015-03-01林创华蔡晨晖

林创华,蔡晨晖

(佛山科学技术学院自动化系,广东佛山528000)

实验用FPGA运动控制原型系统的设计与实现

林创华,蔡晨晖

(佛山科学技术学院自动化系,广东佛山528000)

摘要:根据当前FPGA市场快速繁荣发展及其工业应用迅速普及的需求,设计了一种实验用基于FPGA的三轴运动控制原型系统。该系统采用Altera的cycloneIVE系列芯片,使用Verilog HDL语言,在DE2—115FPGA开发板上实现电机起停控制、电机正反转控制、调速控制、PWM产生、LCD显示等模块的功能,有助于学生掌握FPGA的设计与开发,并可作为运动控制实验课程的参考。

关键词:FPGA;运动控制;Verilog HDL

近年来,运动控制系统的设计与实验成为电子技术实验课程的一个重要内容[1-2]。FPGA作为一种灵活性好、功能强大、易于开发的可编程器件,在运动控制领域得到广泛应用。例如,文献[3-12]均采用FPGA作为其运动控制器的核心模块来实现运动控制。

面对工业领域普及和深入广泛的应用,在高校加强基于FPGA运动控制系统的实验与开发成为不可忽视的事情。为此,笔者适时地在电子技术实验中开展基于FPGA的运动控制系统设计与开发的研究,旨在提高学生对FPGA的认识和了解,并强化他们基于FPGA的设计与开发能力。

作为一种实验用原型系统,最主要的特征就是可展示性与示教性,这是实验系统区别于一般工业应用系统的根本。基于此设计了一个基于Altera公司cycloneIVE芯片的FPGA运动控制原型系统,该原型系统具备一般FPGA运动控制的全部要素并可完成各种示教工作。

软件系统是驱动硬件系统作业的核心,FPGA系统也如此。Altera的FPGA开发需要利用QuartusII综合环境,使用VHDL语言或者Verilog HDL语言编程。

本文主要介绍采用Verilog HDL编程实现所设计的实验用三轴运动控制原型系统的驱动和调试。主要包括在DE2—115FPGA开发板上电机起停控制、电机正反转控制、调速控制、PWM产生、LCD显示等模块的功能实现。

1 实验用运动控制原型系统设计概略

从硬件层面来看,一个运动控制系统必须具备几个核心模块:基本输入与输出模块、电机的驱动与控制模块、信号灯的控制模块、时钟模块与电源管理(PWM)模块。而根据自身需求选择合适的开发板、

芯片以及元器件,设计出硬件的驱动电路尤为重要。

从软件层面来看,必须首先做好开发环境的搭建,包括所选芯片的配置工作以及代码下载方式的选择;然后选择合适的编程语言,根据硬件层面的功能需求进行程序的编写。

1.1系统总体设计

根据硬件层面的需求,本文设计出了最简单的实验用运动控制原型系统,如图1所示。

图1 系统基本结构

图1中各组成的功能分别如下所述。

(1)驱动电路。驱动电路A、B及C融合了PWM功能。

(2)LED指示。LED实现信号灯控制。

(3)配置接口。配置接口用来配置FPGA,主要有AS和JTAG两种配置模式:1)AS主动配置,将程序配置到芯片EPCS64中;2)将JTAG配置到FPGA中。

(4)Key键。Key0到Key3按键是对跳变沿敏感加入施密特触发器消除抖动的按键。

(5)SW键。SW0到SW2为对电平敏感的拨动开关。

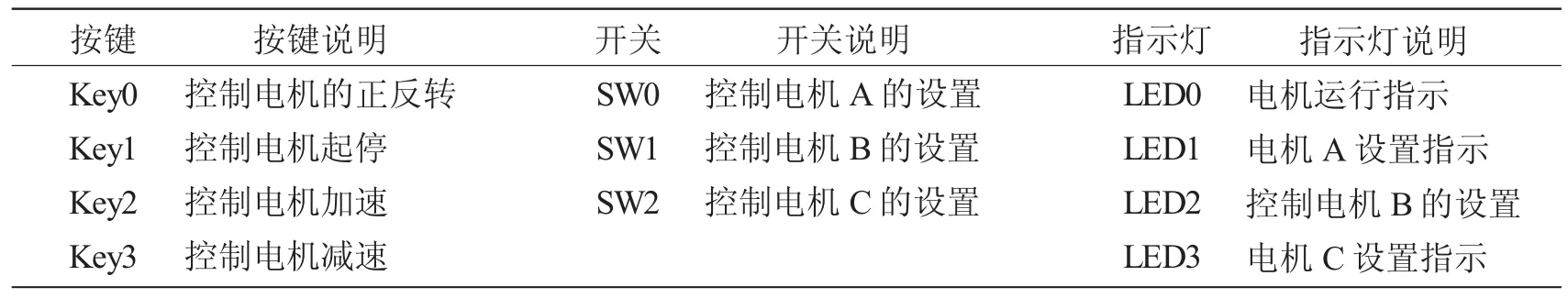

按键与开关主要实现对电机的控制,其功能定义如表1所示。

表1 按键、开关和指示灯说明

1.2开发板与电机的选择

1.2.1开发板与芯片的选择

根据FPGA的发展现状,目前有DE2-115实验板。该实验板采用Altera公司的cycloneIVE芯片,晶振的频率是50 MHz,芯片最高频率可达到240 MHz,具有速度快且生成的硬件电路各功能模块为并行状态,易于体现FPGA并行流水作业特征。

1.2.2电机的选择

选择直流行星齿轮电机,该电机转速计算公式为

式(1)中,n为电机转速,U为电枢端电压,I为电枢电流,R为电枢电路总电阻,φ为每极磁通量,K为电动机结构参数。

由式(1)可以看出,n与U、I有关,即可控量只有这两个。这样可以通过调节U、I这两个量来改变n。而I又与U有关,因此可通过调节U来改变电机n。

1.3硬件驱动电路设计

1.3.1PWM的设计与实现

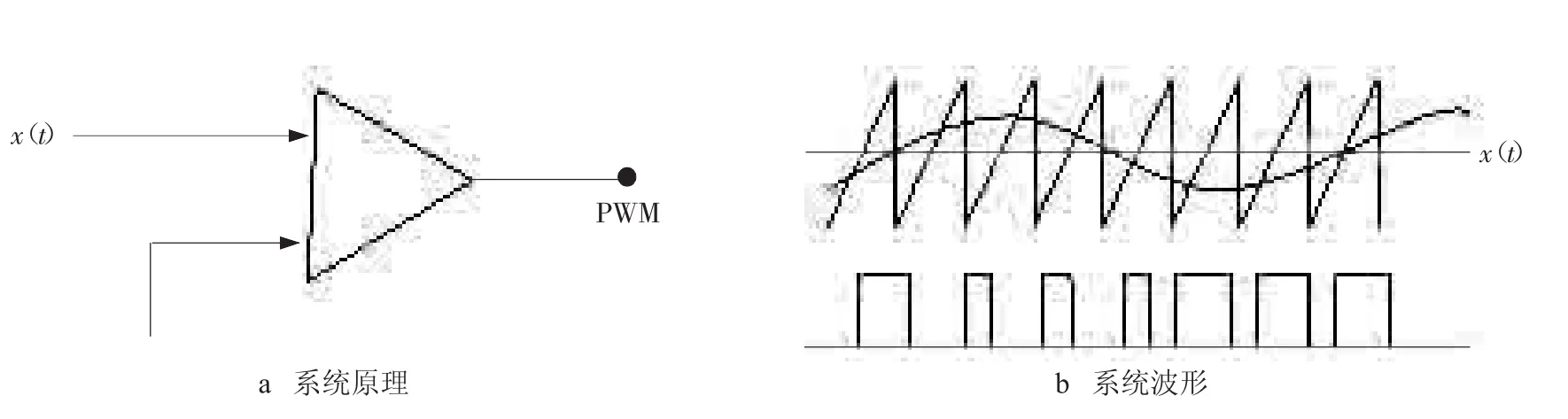

PWM可由模拟与数字两种模式实现。模拟方式主要采用比较器和锯齿波发生器产生脉冲宽度调制波实现PWM,系统原理和波形如图2所示。

图2 硬件PWM原理

从图2可看出,如输入信号如果大于锯齿波信号,比较器输出正常数A,否则输出0。因此比较器输出一列下降沿调制的脉冲宽度调制波。

数字PWM基本原理如图3所示。在时钟脉冲的作用下,循环计数器的输出逐次增大,数字调制信号用一个寄存器来控制,并不断与循环计数器的输出进行比较,当调制信号大于循环计数器的输出时,比较器输出高电平,否则输出低电平。通过改变控制寄存器的值,就可以控制高电平的大小,即改变在一个计数周期占空比,因而产生出不同的脉冲宽度调制波。用不同的脉冲宽度波,作为驱动器的输入,用来改变电机的电压,从而达到调速的目的。

硬件实现PWM需要额外的硬件资源,通过比较可知,数字PWM只需要调节控制器的数值,就可得到不同的脉冲宽度调制波形,因此本研究采用数字PWM技术。

1.3.2驱动电路简介

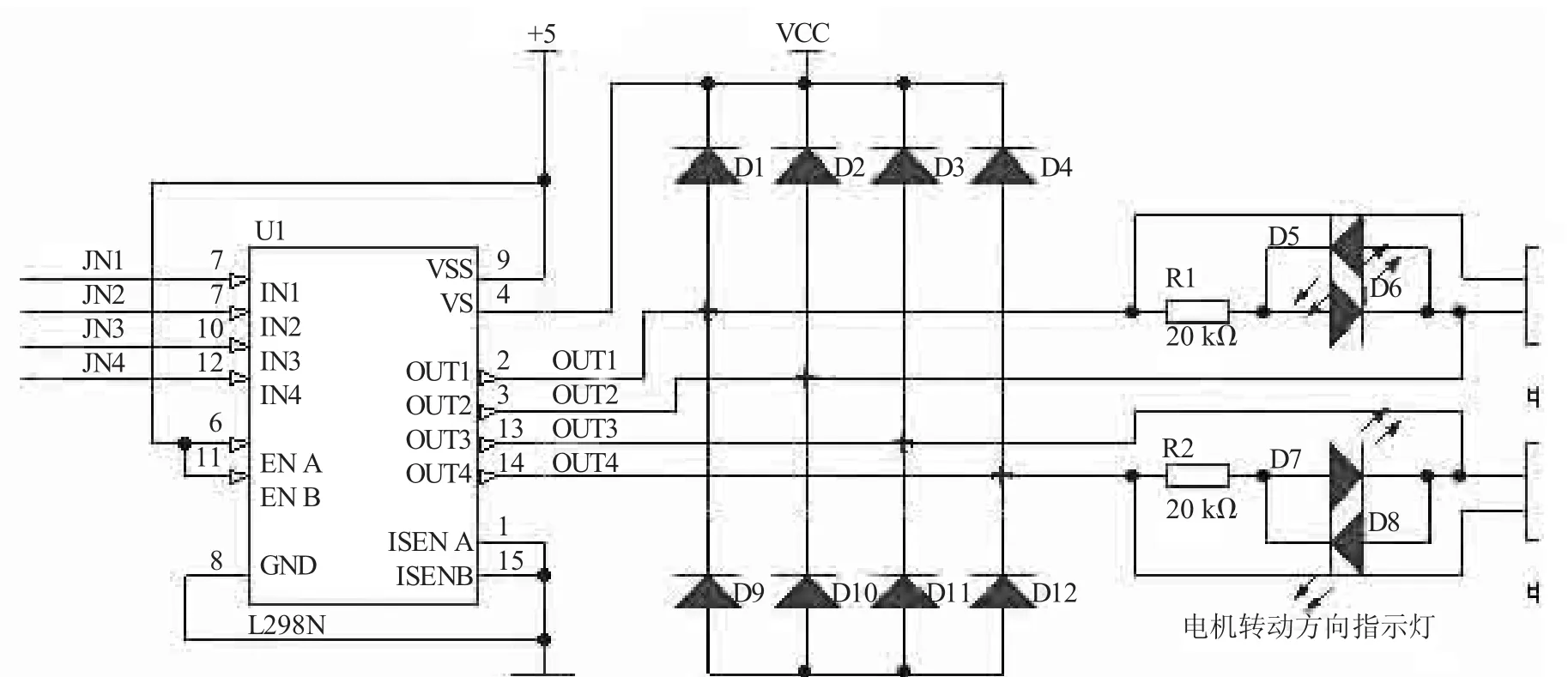

本研究采用H型电路,其原理如图4所示。

图4 驱动电路原理

由图1可以看出,当IN1与IN2之间有电压差时,经过L298N放大,输出OUT1和OUT2,把输出接在电机的两端就可以驱动电机。改变输入电压差的极性,就可以改变电机的正反转。这种设计的好处是,可以通过编程改变输出接口的电压以实现电机转速、正转与反转。

1.4软件开发

1.4.1编程语言的选择

硬件描述语言(HDL)是一种用形式化方法来描述数字电路和系统的语言。Verilog HDL和VHDL最大的差别在语法上,Verilog HDL是一种类C语言,而VHDL是一种ADA(Action Data Automation,行动数据自动化)语言。考虑到学生具有C语言基础,易于掌握Verilog HDL语言,本设计选用Verilog HDL语言编程。

1.4.2配置芯片

EPCS64属于Altera的串行配置器件系列,是可编程逻辑工业领域中最低成本的配置器件。EPCS64拥有包括在系统可编程(ISP)、Flash存储器访问接口、节省单板空间的小外形集成电路(SOIC)封装等高级特征,使得串行配置器件成为CycloneRII和Cyclone FPGA系列产品在大容量及价格敏感的应用环境下的完美补充。Altera的系列串行配置器件EPCS64也为StratixRII系列器件提供了一种低成本、小型化的解决方案。FPGA配置芯片选用EPCS64,具有64M的存储空间,可以支持FPGA的AS配置模式。为此,采用EPCS64配置方式。

1.4.3下载方式的选择

FPGA器件主要有3种配置下载方式:主动配置方式(AS)、被动配置方式(PS)和常用的(JTAG)配置方式,本设计主要使用的是AS和JTAG两种方式。

AS和JTAG是两种主要的FPGA配置方式,各有其特点,AS掉电可以储存数据,上电的时候FPGA从配置器件中读取程序;JTAG配置方式时间比较快,直接配置在FPGA中。由于FPGA是基于ARM结构,掉电失去数据,所以在测试和板级调试的时候采用JTAG配置方式,等确定程序完成好后采用AS配置方式。

2 运动控制系统软件设计

完成了硬件系统设计及软件配置后,关键一步就是软件编程。这是学生将来从事FPGA开发的基础。为此,下面重点介绍时钟分频、电机控制、PWM以及LED显示这几个模块。

2.1时钟分频模块

时钟分频模块主要产生一个分频时钟,定义了一个17位的寄存器,每当有一个时钟上升,计数器的值加1,当计数器的值大于48 000时,分频脉冲为高电平,小于48 000,则为低电平。FPGA的时钟为50 MHz,周期为20 μs,经过分频电路产生的分频时钟的周期约为2.6 ms,这样的分频时钟可以作为后来的按键检测和驱动LED的时钟信号。其代码如下:

always@(posedge clock)

begin

clk_1k=(counter>=17’d48000);

if(clk_1k)

counter<=17’d0;

else

counter<=counter+1’b1;

end

2.2电机按键控制模块

电机按键控制模块主要控制电机的起停,每当按键key1[2]按下时,PWM取反,从而用这个控制信号去控制PWM模块的输出,从而达到控制电机起停的目的。其代码如下:

always @(posedge clk_1k)

begin

if(key[3])

pwm_en=1;

else

pwm_en=0;

end

2.3电机调速

电机主要用于调速。如果按下启动开关,且按下应许设置开关,进入设置程序,按下key1[0],dutycycle寄存器的值加1,按下key1[1],duty-cycle寄存器的值减1,用duty-cycle寄存器值作为PWM的比较寄存器的值,每次按键按下改变寄存器的值,从而就可以改变PWM的占空比,达到调速的目的。

本设计中,duty-cycle寄存器为4为寄存器,有16个值,可以实现16个档位的调速,寄存器的位宽越宽,可以实现的调速等级越多,调速越平滑。在此选用那个16个档位的调速,是为了使调速效果更明显,便于调试和观察。设计有3台电机,必须设定3个调速寄存器与3个设定开关,这样打开相应的电机设置开关,进入设置,就可以实现各自的调速,互不影响。根据速度合成的原理,3个电机的速度不同,只要调节它们的速度,就可以在空间走出不同的轨迹。其代码如下:

always @(posedge clk_1k)

begin

if(key[0]&! key1[0])

begin

duty_cycle1 <= duty_cycle1 + 1’b1;

end

f(key[0]&! key1[1])

begin

duty_cycle1<= duty_cycle1 - 1’b1;

end

end

2.4正反转控制

当按下Key1[3]时,moto_dir电平反转,可以用moto_dir控制PWM的输出反转。当moto_dir为1时,motoa1端输出pwm,moto_b1输出低电平;当moto_dir为0时,motoa1输出为0,motob1输出为PWM,从而实现电平反转,电机实现正反转,其他两台电机原理相同。其代码如下:

always @(posedge key1[3])

begin

moto_dir<= ~moto_dir;

end

assign motoa1 = moto_dir ? pwm_in1: 1’b0;

assign motob1 = moto_dir? 1’b0 : pwm_in1;

assign motoa2 = moto_dir ? pwm_in2: 1’b0;

assign motob2 = moto_dir? 1’b0 : pwm_in2;

assign motoa3 = moto_dir ? pwm_in3: 1’b0;

assign motob3 = moto_dir? 1’b0 : pwm_in3-

2.5PWM产生模块

计数寄存器位宽为17位,计数周期约为2.6 ms,当计数器的高4位小于duty_cycle(比较寄存器)的时,输出高电平,或者就输出低电平。当duty_cycle值增大的时候,输出的高电平占空比增大,电机的

转速增加;当duty_cycle值减小的时候,输出高电平占空比减小,电机减速。其代码如下:

always @(posedge clock)

begin

if(pwm_en&(counter1[16:13]<=duty_cycle1))

pwm_out1 <= 1’b1;

else

pwm_out1 <= 1’b0;

end

2.6LED指示模块

LED指示模块用来控制LED灯的显示。其代码如下:

always @(posedge clk_1k)

begin

if(key[0])

led0=1;

if(key[1])

led1=1;

if(key[2])

led2=1;

end

3 效果

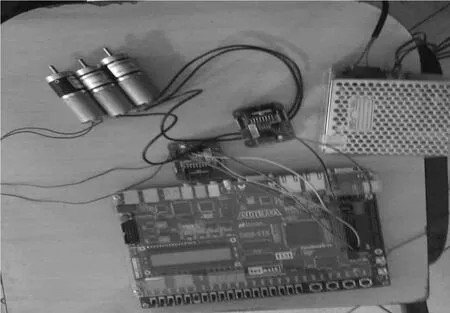

按照硬件设计原理,选配好所需器件、连接线,连接成基础硬件电路后,采用QuartusII进行开发,经综合粘贴后生成RTL文件上传到FPGA。让学生参与调试,最后实现所设计的各个功能。图5是最终实现的FPGA原型系统。

图5 实现的FPGA原型系统

4 小结

该是真正实现数控系统的基础,也是后续工作的参考。系统实现了预期的设计并且能够让学生亲身体验FPGA的开发,可达到预期的要求。当然,本设计还有值得改进的地方,例如增加一个速度反馈

实现闭环控制、LED速度与FPGA速度匹配、更好的软件控制界面等。为此,在试验中将这些作为问题提出,启发学生的探索求索思维。总之,通过这样的原型系统,让学生亲身参与方案制定、设计、调试,学生对FPGA实验与开发将收到事半功倍的效果。

参考文献:

[1]赵金.运动控制技术综合实验教程[M].武汉:华中科技大学出版社, 2010.

[2]李萍,厉虹,侯怀昌.电气工程及其自动化专业运动控制系统课程实验教学改革探讨[J].教育理论与实践, 2010(15): 61- 63.

[3]易德福,王小椿.基于FPGA与PC- 104的CNC多轴运动控制器设计[J].组合机床与自动化加工技术, 2006(1): 65- 68.

[4]尚雅层,雷兵丰,来跃深.基于DSP和FPGA的开放式数控系统运动控制的设计与仿真[J].西安工业大学学报, 2007 (2): 130- 134.

[5]闫华,左健民,汪木兰.采用FPGA技术实现DDA插补算法的研究[J].现代制造工程, 2007(9): 51- 53.

[6]章明,马伟,李济顺,等.基于DSP和FPGA的数控系统运动控制的设计[J].电工技术, 2008(10): 43- 45.

[7]魏立军.基于DSP和FPGA的数控系统研究与开发[D].南京:南京航空航天大学, 2008.

[8]摆银龙,赵方,郑小梅.基于DSP和FPGA的嵌入式同步控制器实现[J].现代电子技术, 2009(6): 28- 30.

[9]汪木兰.基于FPGA/CPLD数控系统插补智能芯片设计[J].中国制造业信息化, 2006, 35(21): 23- 37.

[10]刘海平.基于FPGA数控精插补芯片的设计[D].南京:南京理工大学, 2008.

[11]刘剑文,刘士荣,吴秋轩,等.基于FPGA的一种连续插补器的设计与实现[J].科技通报, 2010, 26(5): 42- 46.

[12]杨雪峰.基于FPGA的运动控制卡的研究与开发[D].南京:南京航空航天大学, 2010.

[13]陆俊,陈安明.基于FPGA技术的高速数控DDA插补器的设计与研究[J].组合机床与自动化加工技术, 2010(10): 15- 19.

【责任编辑:任小平renxp90@163.com】

Software design and development of three- axis motion control based on FPGA

LINChuang- hua, CAI Chen- hui

(Department of Automation Engineering, Foshan University, Foshan 528000, China)

Abstract:According to the rapid development of FPGA market and increasing requirements of industrial applications, a 3- axle FPGA motion- control system for school experiments is designed. The system uses Altera’s cycloneIVE chipsets and Verilog HDLlanguage torealize the function ofmanymodules on the DE2- 115FPGA development board, including motor’s start and stop control, motor’s reversing control and speed control, PWM generation, the LCD displayand soon. The systemis helpful for students toknowthe development of FPGA, and alsoprovides a good reference for motion control course.

Keywords:FPGA; motion control; Verilog HDL

作者简介:林创华(1970-),男,广东揭阳人,佛山科学技术学院实验师。

基金项目:国家星火计划资助项目(2013GA780052);广东省教育厅特色创新资助项目(2014KTSCX156);佛山市科技发展专项资金资助项目(2011AA100021);佛山市产学研资助项目(2012HC100131);佛山科技创新平台资助项目(2013AG10007);禅城区产学研资助项目(2012B1011,2013B1018);禅城区科技计划资助项目(2013A1021)

收稿日期:2014-12-10

中图分类号:TP332.3

文献标志码:A

文章编号:1008- 0171(2015)04- 0039- 07