基于FPGA的自适应像素分割算法设计与实现

2015-02-26丁倩雯

丁倩雯

(无锡科技职业学院,江苏无锡214028)

基于FPGA的自适应像素分割算法设计与实现

丁倩雯*

(无锡科技职业学院,江苏无锡214028)

摘要:为了解决运动目标前景检测的精度问题,提出了一种基于FPGA实现的自适应像素分割系统。该系统通过构建新的背景模型和前景分割检测技术优化检测结果,并对传统的自适应像素分割算法进行了调整和修改,以便在FPGA平台上进行硬件实现。在Xilinx virtex7 FPGA芯片上已完成了硬件测试。试验测试结果显示相比其他算法,本文提出设计的各项性能指标均表现良好,检测精度达到71.4%,平均功耗为6.452 W。能够实现以50 frame/s,实时处理分辨率为720×576的视频流。关键词:目标检测; FPGA;自适应;背景建模

前景目标检测和背景建模是现实世界中许多图像处理与分析系统的重要组成部分。比如:先进的自动化视频监控系统,远程病人监控视频,视频交通监控,自动导引车或语义图像分析。前景目标对象分割的目的是把图像中的所有像素分为两类:背景元素和前景对象。在现实世界,许多的应用背景元素可能不是静态的。流动的水或树枝在风中摇曳就是典型例子。在这样的场景中简单的将当前帧和背景图像相减取阈值,不足以获得良好的结果,很难将前景对象从背景元素中分离出来。另一方面,分析的主体对象(例如,人,车,等)可能会停止一段时间,这也会加入背景模型造成错误的判断。此外,当他们再次开始移动时,也会发生假的误报性错误[1]。

以上例子表明了问题的复杂性,因此许多文献都提出了相关研究,以进一步更好地实现背景建模和目标分割算法。其中最基本的是采用计算N-last缓冲帧的平均数/中值数。更复杂的采用多变量,如GMM(高斯混合模型)、分簇和编码本等,文献[2]对此做出了比较全面的概述。

文献[3]提出了通过小波变换对不同区域进行参数调整,实现了自适应阈值去除背景和噪声完成目标检测。文献[4]通过参数空间中累加器的无效累积,对比两次阈值结果,提出了改进的Hough圆形目标检测算法。文献[5]提出了一个基于像素的参数自适应目标检测方法PBAS (Pixel-Based Adaptive Segmenter),该算法的创新之处在于其背景模型包含N个样本,且样本间的临时关系跟传统算法相反,但算法复杂程度有所提高了。

FPGA可重构设备被证明是一个良好的平台用作硬件实现图像处理和分析算法。同时也可用于背景建模和前景目标检测。这主要是由于并行计算和管道数据处理,可用于有效的实现背景生成算法,而且在多变量方法中每个变体都可以并行计算。

在文献[3]中描述了一个GMM(高斯混合模型) 的FPGA实现。模块能够按照20 frame/s的帧率处理高清视频。虽然也是在FPGA设备进行模拟目标,但最后没有给出工作系统的参数说明。文献[4]提出了基于Horprasert的背景建模算法硬件实现。其目标平台为XilinxSpartan 3 FPGA系列。作者修改了原始算法通过添加阴影的检测机制,改善了分割结果。该系统是一个硬件软件合作设计方法的例子。部分计算和控制功能是由Microblaze嵌入式软核完成的。此外,使用两种不同的逻辑描述方法:C++语言(对象检测)和硬件描述语言(VHDL) (辅助模块)。但是其没有提出背景的更新机制设计。最初的模型是由Microblaze嵌入式软核基于第一个128帧的视频序列构造。同时最终的实现采用了一个前景对象模板标记机制。该系统能够处理每秒32帧1024×1024分辨率的视频。估计功耗为5.76 W。

本文提出了一种改进的基于FPGA实现的自适应像素分割系统,并在Xilinx Virtex 7 FPGA系列的VC707评估板上进行了设计验证。系统通过构建新的背景模型和减法技术优化检测结果,对传统的自适应像素分割算法进行了调整和修改,以便在FPGA平台上进行硬件实现。实验测试使用Changedetection.net数据库[4],采用了市面通用的能够实时显示处理720×576@50帧视频的摄像系统。

1 自适应像素分割算法原理

在自适应像素分割算法中[5],背景模型是基于分析视频序列中N个样本的缓冲区构建的。设xi表示一个特定的像素。根据模型B(xi)与当前帧I(xi)的对比结果,可以完成前景/背景分类。对于每一个像素,设置一个独特的决策阈值是R(xi)。按照指定的参数T(xi)对随机样本进行更新。对每个像素的R(xi),T(xi)分别进行调整,使得PBAS区别于其他方法。在下面的章节中对算法过程给出了详细描述。

1.1前景分割处理

在自适应像素分割算法中,需要根据当前像素模型的比较结果,对前景/背景进行分类。对于本文提出的方法,背景模型被定义为一个最近观察到的像素值数组N:

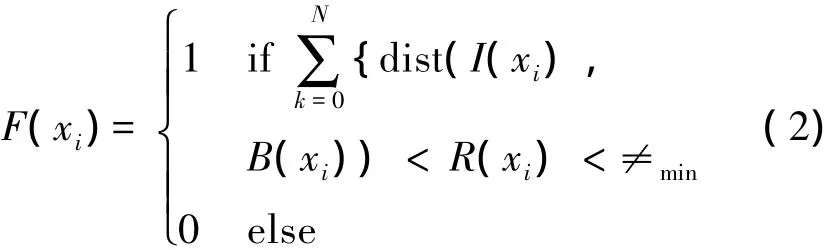

当I(xi)与背景模型中≠min采样点之间差值,小于阀值R(xi)时,像素点xi属于背景。因此,目标模板可由以下公式计算:

式中:F=1表示前景,F=0表示背景,且dist表示差值测量:

1.2参数更新

以前打仗一样15分钟就结束战斗的晚饭竟吃了一个半小时,两个人说说笑笑的样子让宝宝都觉得不适应了。小家伙来拉林蓝的手,吃醋地说:“妈妈,不要陪爸爸说话了,陪宝宝去搭积木。”

背景模型更新的补偿是补偿光照微小变化的必要途径,如在显示场景的一些不可避免的变化(晃动的树木,流水和停车场中汽车的出现和消失)[6]。

一个背景建模方法可以被区分两种更新策略[7]:自由派和保守派。对于第一种情况,所有的像素都被更新,第二种只更新被分类为背景的像素。这两种方法都有一定的独特性,自由策略的主要缺点是对于在背景模型中快速移动的前景目标,会导致分割错误,因此只适用于物体移动很慢的情况。保守的方法避免了上述的现象,但也存在一个缺点,即使用前景对象模板作为更新条件会导致“死锁”[8],这主要是由小的分割误差和运动的物体引起。此外,一旦一个错误出现将永远不能将其忽略。因此需要设计一些专有机制来避免这种情况的发生。一个可行的解决方案是计算一个像素被分类为目标对象的次数。当计数器的值超过阈值,则强制其更新。自适应像素分割算法使用了保守的策略,即使用一个额外的机制更新相邻像素,从而防止不可挽回的分割错误。

只有当像素被分类为背景时,才可能会更新(F=0)。具体操作是使用当前像素值I(xi)替换从背景模型Bk(xi)中随机选择的样本。更新的概率为p=1/T(xi)。同样,从3×3的局部内容中随机选择一个模型,再从选择的模型中随机选择一个样本,并用当前值I(yi)对其进行替换。其中yi表示选择内容的一个像素。

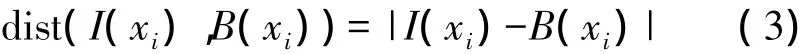

在自适应像素分割算法中,提出了一种R(xi)更新机制。首先,当前像素和模型采样之间的最小差值为:D={ D1(xi),…,DN(xi) },如果一个像素更新最小差值:

D(xi)的平均值是背景动态变化的指标,用于R(xi)的更新:

式中:Rinc/dec表示更新率常量,Rinc/dec=0.5。Rsc表示换算系数,Rsc=5。另外,判决阀值有一个下界Rlower=18。

学习速率更新过程如下:

在实际中,视频序列都基本处在RGB颜色空间。因此文献[6]提出单独处理每个颜色组件,并使用或运算比较结果分割模板(例如,F (xi) = FR(xi) ORFG(xi) ORFB(xi) )。

在原始算法中,背景模型进行了边缘信息补充(使用Sobel梯度值)。然而,分析[5]中所描述的结果,却得到的以下结论:增加边缘信息,对分割只是略有改善,却会导致背景模型的大小增加,并使得当前像素和背景之间差值计算变得更复杂。因此,在本文描述的硬件实现中没有使用这一机制。

2 提出的硬件实现设计

在可编程器件FPGA上实现背景建模算法的一个主要的问题,是需要为连接外部存储器资源提供较高的传输速率,其中背景模型存储参考文献[9-10]。在使用自适应像素分割算法的情况下,要确保以下的传输速

式中:noCC表示色彩分量序号(1-灰度,3-RGB),bR表示更新速率T(xi)位数,N表示像素样本的数量,bB表示单个样本Bk(xi)的位数。bD表示最小差值Dk(xi)的位数。乘以2是因为数据的读取和写入。使用的硬件平台(VC707)的最大可用传输速率为2 048 bit/像素时钟周期(720像素×576像素在50 frame/s时,像素时钟频率为25 MHz)。具体参数[11]设置如下:

式中:bR=bT=16 bit,bB=bD=8 bit。16 bit由8 bit整数位和8 bit小数位组成。

在这种情况下,最大样本数量数量N = 17 (RGB),N=19(grey)。R(xi)和T(xi)的精度可通过以下参数设置。上下界的限制值为一个8 bit的整数(R(xi)的最大值为255,因为更大的数量对阀值dist没有任何影响)[12]。此外,在使用的FPGA设备中单个乘法器DSP48可以处理整个16 bit数字。

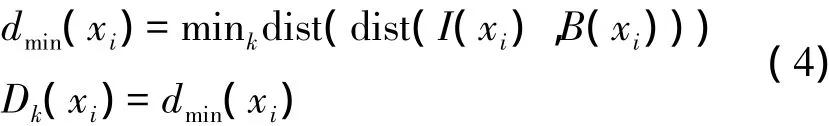

图1显示了本文提出的FPGA硬件实现系统的结构图。通过Avnet DVIIO FMC模块(FPGA Mezzanine Card)的HDMI接口接收视频数据,能够高频率的串行信号转换成并行格式。3个颜色通道随之分离,并通往3个独立的主处理单元实体。模型存储在外部存储器。在以前的文献[6]中,使用特殊的控制器来执行背景模型的序列读取和写入。伪随机数的产生(RNG)过程参照文献[5]中的描述。

图1 本文提出的FPGA硬件实现系统的结构图

从外部RAM内存,每一个颜色分量处理单元载入先前的算法产生的背景模型。第1步,按照式(3)计算当前像素值与所有先前产生的样本之间的差值,并与阀值R(xi)进行比较。这些信息被传递给两个模块。第1个模块是一个求和模块。将超过R(xi)差值的和与阀值进行比较,并通过式(2)进行前景/背景分类。每个颜色分量RGB的前景模板使用OR进行运算处理,最后经过一个9×9的中值滤波器。第2步计算最小差值,并使用二进制比较数计算机其对应的索引。

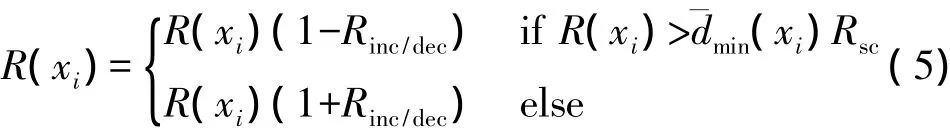

虽然分割结果是计算得到的,但是在下次迭代前,背景模型必须更新。为了实现这个任务,创建了一个三维的context模型,它拥有基本的3×3滑动布局窗口,但是每个单一的元素由当前像素值I(xi),N背景模型样本Bk(xi),N最小差值DK(xi)和参数(R(xi),T(xi) )组成。图2显示了自适应像素分割软件流程。

图2 自适应像素分割软件流程框图

通过RNG模块产生4个随机数,并发送给更新控制器模块。第1个被用于决定是否执行一个更新处理。如果执行,像素中心的一个随机样本,一个随机相邻模型和该模型的一个随机样本被挑选出来替换相应的当前像素值。

最后,计算出像素中心的一个平均最小差值珔dmin(xi),这需要使用求和树和分频器。然后使用得到信息来更新决策阈值(式(5) )和学习速率参数(式(6) )。所有这些信息被组合起来,然后用于更新图像制定像素的背景模型。数值存储在一个FIFO中(内存控制器使用与图像处理模块不同的时钟)。在背景模型初始化时,所有的参数设置为默认值,使用从3×3context中随机挑选的像素填充样本缓冲。然后按下一个按钮,系统进入正常运转模式。

通过在MATLAB中编写脚本,会自动生成了VHDL文件。该VHDL文件描述了主要的处理模块,以及子模块:求和树,二进制比较树、context等。这能够方便的修改参数,特别是样本的数目N。使用一个类似的方法产生了均值模块。这样的设计具有较高的灵活性,容易在其他硬件平台进行实现。

该系统项目使用了VHDL和Verilog硬件描述描述语言,硬件平台采用一个Virtex 7(XC7VX485T) FPGA开发板配合Xilinx ISE 14.4仿真套件。选取了带有Avnet DVI I/O FMC模块的Xilinx VC707评估板。在ISim软件中的仿真模拟结果显示提出的硬件模块完全符合在C++中实现的软件模型。显示的最大工作频率为124 MHz,足够实现以50 frame/s的速率实时处理720×576彩色视频数据。根据Xilinx XPower Analyzer上显示的数据,功耗大概为4.228 W。综合分析得出,本文提出的FPGA系统的功耗约为(6.452 W)。资源使用情况如表1所示。

表1 系统资源利用率

图3给出了实验评估使用的Xilinx virtex 7 FPGA开发板实物图。

图3 使用的Xilinx virtex 7 FPGA开发板系统分辨率720×576,50 frame/s,RGB,N=17,中值滤波9×9) (

3 系统测试评估

为了评估本文提出系统的性能,使用OpenCV库和IEEEchangedetection.net数据库编写了一个C++程序,实现算法的软件模型。数据集包含的序列可分为6类:基本的,动态背景,相机抖动,间歇运动对象,阴影,目标运动。该数据库包含了背景建模算法所需的大部分图像。图4给出了样本图像和获得的目标模板图像。

图4 背景模型包含19个样本,使用RGB颜色空间

实验所用方法的具体描述如下:

(1)将通过算法计算得到的目标模板与参考模板比较,因为自适应像素分割算法不包含一个内置的阴影检测程序,只考虑前景和背景分类。其中TP (True Positive)表示像素属于前景对象,分类为前景像素。TN(True Negative)表示像素属于前景对象,分类为前景像素。FP(false positive)表示像素属于前景对象,分类为前景像素。FN(false negative)表示像素属于前景对象,分类为前景像素。

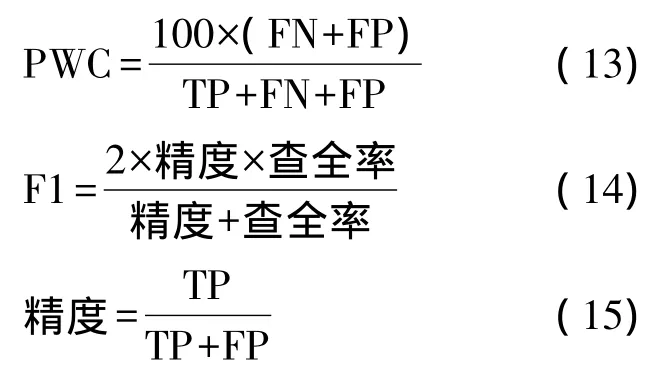

(2)然后按照以下方法计算其他参数:

最终获得结果如表2所示。可见本文提出的硬件实现的查全率,特征值,FNR(漏报率)和FPR(误判率)与文献[5]数据(即传统的软件实现自适应像素分割算法)很接近。错误分类比值高于传统软件实现方法,但是接近GMM结果。其中相比其他方法,硬件实现的FPR比较高,这是由于硬件实现和软件实现之间存在不同:(1)更少的背景模型样本数量(NFPGA=17,NSOFT=35); (2)固定的参数点计算(特别是R(xi),T(xi) )。值得注意的是,本文提出的FPGA实现以50帧/s速率,实时处理分辨率为720×576的视频流,优于在i7 3.5 GHz多线程处理器上的软件实现[5]且更节能。

表2 系统资源利用率

4 结论

本文给出了自适应像素背景建模和前景分割算法的FPGA硬件设计,将原算法转变成固定点计算,且用并行计算方式进行了实现。在changedetection.net数据库上的测试结果表明了该设计的有效性和先进性。在合适硬件平台上,可以实现以50帧/s速率,实时处理分辨率为720×576的视频流。

参考文献:

[1]戚世乐,王美清.自适应分割弱边缘的活动轮廓模型[J].山东大学学报:工学版,2013(6) :17-20,33.

[2]强振平,刘辉,尚振宏,等.改进的基于统计模型的前景检测方法[J].计算机应用,2013(6) :1682-1685,1694.

[3]王艳华,刘伟宁,陈爱华.基于小波变换的海空背景下小目标检测研究[J].电子器件,2007,30(3) :992-994,998.

[4]张道德,胡新宇,杨光友.一种改进的随机Hough变换圆形检测算法[J].电子器件,2009,32(3) :721-724.

[5]Genovese M,Napoli E.FPGA-Based Architecture for Real Time Segmentation Adenoising of HD Video[J].Journal of Real-Time ImageProcessing,2011,11(2) :1-13.

[6]Rodriguez-Gomez R,Fernandez-Sanchez E J,Diaz J,et al.FPGA Implementation for Real-Time Background Subtraction Based on Horprasertmodel[J].Sensors,2012,12(1) :585-611.

[7]Hofmann M,Tiefenbacher P,Rigoll G.Background Segmentation with Feedback:The Pixel-Based Adaptive Segmenter[C]/ /Computer Visionand Pattern Recognition Workshops(CVPRW),2012 IEEE ComputerSociety Conference on,June,2012:38-43.

[8]李鸿生,薛月菊,黄晓琳,等.改进的自适应混合高斯前景检测方法[J].计算机应用,2013(9) :2610-2613.

[9]揭展明,段文迪,曹雨.基于OpenCV前景检测的循迹算法[J].计算机光盘软件与应用,2013,19:99-101.

[10]祝贵,杨恢先,岳许要,等.自适应的最大散度差图像阈值分割法[J].计算机工程与应用,2013,15:188-191.

[11]李拥军,曾标,徐克付,等.复杂背景下基于贝叶斯-全概率联合估计的前景检测[J].电子与信息学报,2012(2) :388-392.

[12]杨涛,李静,潘泉,程咏梅.一种基于多层背景模型的前景检测算法[J].中国图象图形学报,2008(7) :1303-1308.

丁倩雯(1983-),女,汉族,江苏无锡市人,无锡科技职业学院讲师,硕士,研究方向为电子技术,电路设计,自动控制技术,dingqw1983@ 163.com。

Design of a Low-Jitter Charge Pump Phase-Locked Loop*

BAI Yang,ZHANG Wanrong*,JIANG Zhiyun,HU Ruixin,ZHUO Huihan,CHEN Changlin,ZHAO Feiyi

(College of Electronic Information and Control Engineering,Beijing University of Technology,Beijing 100124,China)

Abstract:A low-jitter charge pump phase-locked loop(CPPLL) was proposed to resolve the problems of jitter of conventional CPPLL.The CPPLL consists of a dynamic phase frequency detector,a charge pump based on constantgm rail-to-rail operational amplifier,a differential ring VCO.Based on SMIC 0.18-μm CMOS process,the novel CPPLL was designed and verified by Cadence.The results indicated the dynamic PFD effectively eliminated the dead zone to reduce the jitter of CPPLL.The current mismatch of novel CP was less than 2% when the output voltage ranged from 0.5 V to 1.5 V.The output phase noise of VCO was-94.87 dB at 1 MHz when the frequency was 1 MHz.The tuning range of VCO was 0.8 GHz~1.8 GHz.Output voltage fluctuation of locking CPPLL was 2.45 mV.Peak-peak jitter of output clock was 12.5 ps.

Key words:charge pump phase-locked loop; low jitter; constant-gm rail-to-rail operational amplifier; VCO

中图分类号:

文献标识码:A

文章编号:1005-9490(2015) 03-0510-06

收稿日期:2014-07-17修改日期:2014-10-21

doi:EEACC:125010.3969/j.issn.1005-9490.2015.03.009