基于混沌复合映射算法的150 MHz高速码发生器设计*

2015-02-26钱莹晶张仁民

钱莹晶,张仁民

(怀化学院物理与信息工程系,湖南怀化418008)

基于混沌复合映射算法的150 MHz高速码发生器设计*

钱莹晶,张仁民*

(怀化学院物理与信息工程系,湖南怀化418008)

摘要:为提高脉冲编码雷达测距分辨率和脉压信噪比等性能指标,介绍一种基于logistics和tent混沌复合映射算法的150 MHz高速混沌(Chaos)码发生器。该码发生器采用混沌复合映射算法,经定点化后用VHDL语言在FPGA内实现,最后通过LVDS(高速差分标准)输出。实验结果表明,通过该种方法生成的Chaos序列具有良好的自相关、互相关特性,在保证动态时间不超过码宽度20%的前提下速率高达150 MHz,用于脉冲编码雷达中可以获得距离分辨率为1 m的性能指标。

关键词:脉冲编码雷达;混沌复合映射; LVDS低电压差分标准; Logistics; Tent

项目来源:湖南省教育厅科学技术研究项目(12C0835);湖南省科技计划项目(2013GK3145)

随机码脉冲编码雷达广泛应用于航天航空、军事、交通等领域。目前采用的随机码序列主要是m及其优选对Gold序列。m序列由于其产生原理简单成为一种最基本也是最成熟的伪随机序列,广泛的应用于CDMA移动通信系统、GPS定位系统、测距雷达等扩频系统中,但是非周期自相关性和互相关性不理想,非周期自相关性不理想会导致雷达信号处理系统进行相关运算后出现较大的旁瓣[1-2],互相关性不好会导致相同体制的不同雷达系统间存在相互干扰的不利结果;为了解决m序列中互相关性不好带来的雷达间的干扰问题,可以采用m序列的优先对——Gold序列。Gold序列有很好的互相关性所以可以有效的解决同体制雷达的干扰问题,但是m序列非周期自相关性不理想的问题还是没有得到解决,同时要想找得到长序列优选对很困难进而导致测量距离范围受到限制[3-5]。

由于目前成熟的m序列、Gold序列等测距码存在上述问题,近些年来很多学者和工程技术人员将测距码的研究转向了基于混沌理论的随机序列[6-8]。这种序列利用了混沌算法的非线性和对初值敏感等优良特性,能产生理论上无限长的序列,该序列具有良好的相关性、游离性和平衡性,而且由于其对初值敏感所以安全性也很高,可以用于保密通信、门禁等其他领域。在这些研究中,采用单一的混沌映射算法产生混沌码是最为常见的。但是有关研究结果证明,单一的映射可以通过足够的样本进行相空间重构得以攻破。所以,现在很多学者寻求将多个混沌映射算法进行复合映射以加强算法的复杂性进而提高安全性。同时为提高测距的分辨率,需要尽可能的提高码速率。

本文介绍一种基于logistics和tent复合映射的150 MHz高速混沌码发生器,在自制的以Altera公司Cyclone系列FPGA为核心的平台上设计并实现了150 MHz高速混沌码。

1 混沌码算法原理

为满足测距范围与非周期性要求,文献[9]论证了一种采用基于Tent映射和Logistic映射的组合混沌映射,其构造方法如下:

Logistic映射:

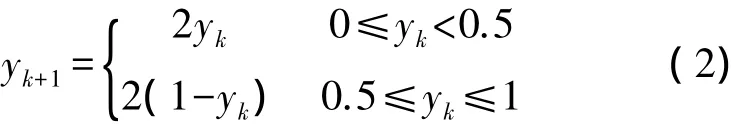

Tent映射:

先由Tent算法产生一组码序列设为x00至xm-1 0共m个值,以此序列中的每一个值作为Logistic映射的初值来产生新的序列组,每组n个值共计m组,设为x00~x0 n-1,x10~x1 n-1,…,xm-10~xm-1 n-1,将以上m组序列首尾相接组合成一个m×n的混沌码序列,即构成新的输出序列。

2 混沌码的硬件实现

2.1混沌码定点实现原理

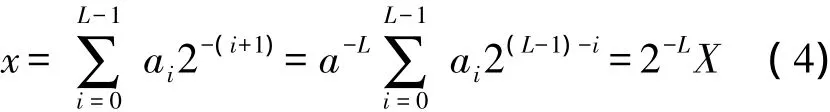

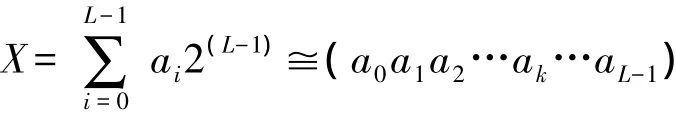

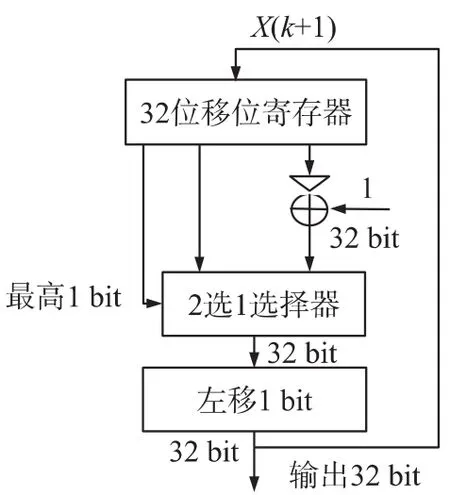

为了提高测距的分辨率,必须提高码速率。如要想获得1m的测距分辨率,码速率必须为150 MHz,而且为了保证脉冲压缩时足够的信噪比而抑制不必要的旁瓣需要保证码的动态时间不大于码宽的20%,如此严格的要求是无法用DSP平台和FPGA/CPLD常规的设计方法。只能利用FPGA实现逻辑然后通过LVDS高速差分标准来输出[10-11]。故此,上述算法需要用VHDL硬件描述语言在FPGA芯片上实现,我们对0~1范围内的小数作如下变换:

取前L位表示x,舍弃后面的位(当然这里存在舍入误差),则

式中:

是一个由L位二进制数表示的整数,它与小数x是一一对应的。将以上变换方法用于Tent序列与Logistic映射,变换为:

由于序列中的值为32 bit,(232-Yk)就是对其求补,即求反加一的运算,这样Tent序列与Logistic序列就分解成为由简单的比较大小、移位、取反加一以及乘加运算等适于数字信号处理芯片快速完成的运算的组合实现。理论与仿真结果证明这一组合序列在数字实现后仍具有良好的混沌特性,且序列长度达到了应用要求。

2.2混沌码的VHDL描述

根据上述算法的原理和定点处理的思路,可以得到如图1、图2所示算法流程:

图1 Logistic映射数字实现

图2 Tent映射数字实现流程

3 实现平台及高速PCB板设计

3.1实现平台

由于混沌码的速率为150 MHz而且需要保证动态时间,普通和低电压的TTL/COMS标准无法实现,需要采用LVDS差分电压标准。因此,设计并制作一块以Altera公司Cyclone系列FPGA为核心支持LVDS标准的高速基带码发生器板,并以此为平台进行混沌码逻辑设计和验证。

根据cyclone芯片手册,该系列的FPGA一共有4个I/O bank,每个IO块支持独立的IO标准,只要有合适的IO电源供电即可。在此将bank4作为高速IO口,采用2.5 V电源单独为该bank的LVDS标准IO脚供电。差分输出管脚配置为168脚和169脚。需要说明的是:这些差分对信号是成对出现的,不能随意指定,这样才能保证差分信号的对称性和相应的优良性能。

3.2高速PCB板设计

高速混沌码发生器的码速率为150 MHz,完全属于高速系统设计。在高速电路板的设计过程有些问题是要特别注意的。否则,不但会影响系统性能,还会导致逻辑错误,更有甚者是电路完全无法工作。事实上,就是需要考虑信号的完整性问题(SI)。所谓信号完整性,就是要使信号具有良好的物理特性(高低电平的阈值以及跳变沿的特性),防止其产生信号的畸变,导致接收端无法识别[12]。

实际系统中,关于信号完整性问题的现象很多,如:反射、振铃、开关噪声、地弹、衰减、串扰、容性负载等。在进行高速电路板设计时,通过合理的布局布线在一定程度上可以有效地预防和减少SI的影响。下面只给出在此高速板设计中的基本原则:

(1)布成多层板,有高速信号的印制板一般都要布成多层板。在密度不很大的板子上,如物理空间条件允许的情况下,将LVDS信号与其他信号分别放在不同的层。由于LVDS信号属于高速信号,为减少此高速信号与电源层和其他信号层信号的干扰,在此LVDS信号层相邻层设置成为地层,这样可以对LVDS信号进行有效地屏蔽以防止干扰。例如:此处的高速电路板就采用4层板,按如下顺序进行布层: LVDS信号层、地层、电源层、其他信号层。

(2)紧耦合原则。LVDS差分线对的线宽和间距必须遵守紧耦合的原则,即平行走线的差分对线的间距要小于或等于线宽。这样可以保证当两条差分信号线距离很近时,由于电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。

(3)减少高速电路器件管脚的弯折。高频电路布线的引线最好采用直线,但实际布线时需要弯折,这时最好采用圆弧形走线。这样,可以减少高频信号对外的发射和相互间的耦合,同时阻抗连续可以尽可能减少反射。当然,高频电路器件管脚的引线也应尽量缩短。

4 实验数据

本文所采用的32位乘法器大大增强了混沌迭代算法的鲁棒性。而且算法不用对32位的算法进行16位的替换,这大大简化了算法的复杂度和运算速度。先用VHDL语言描述了该定点算法,在Quartusii9.0上编译综合适配,生成了用于第三方仿真软件Modelsim仿真的VHO网表文件和SDO的时延文件,然后再该仿真软件中加入测试文件Testbench,仿真后得到响应以txt的形式保存,最后用MATLAB读出这些数据,并对其性能进行了分析。

(1)混沌码的游程相关特性测试:

图3和图4分别为混沌码的互相关特性和自相关特性测试图,该仿真结果显示:这一组合算法的互相关性与自相关性均比较理想。

图3 混沌码互相关特性

图4 混沌码自相关特性

(2)混沌码的游程特性测试:

表1对混沌码的游程特性进行了测试,由统计结果可以看出系统满足平衡特性和对称特性,当码元充分大时,接近理想游程特性1/2n。

(3)混沌码电特性测试

为测量混沌码的电特性,包括码速率和动态时间。在此,输出的波形采用泰克公司的MSO4104,其3dD带宽为1 GHz,采样率为5 Gsample/s,探头有两种:一种是普通无源探头P6139A,其带宽为500 MHz;另一种是有源探头TAP1500,其带宽为1.5G。根据这些性能指标可知采用该示波器配合有源探头可以满足测量码电特性的需要。

表1 混沌码游程分析图

图5为混沌码码速率测量示波器上的截图,标尺a、b间的时间宽度约为6.67 ns,说明其速率为150 MHz。

图6为混沌码动态时间(上升时间)测量时示波器上的截图,标尺a、b间的时间宽度约为946 ps,完全满足小于码元宽带20%的要求(6670 ps×20% = 1 334 ps)。

图5 混沌码码速率测量

图6 混沌码动态时间(上升时间)测量

5 结束语

本文介绍了一种基于logistics和tent混沌复合映射算法的150 MHz高速混沌码发生器设计和实现方法,并在自制的硬件平台上对所产生的混沌码的性能(包括相关特性、游离特性和电特性)进行了测试和验证。实验结果表明,通过该种方法生成的Chaos序列具有如下优点: (1)相比m序列和其优选对GOLD序列,在产生长随机码上具有更明显的优势; (2)由于采用复合映射,产生的随机码具有更好的保密性; (3)良好的自相关和互相关特性能保证了雷达具有理想的主旁瓣比和抗干扰特性;(4)良好的游离性和平衡性保证了码的随机性和功率特性; (5)采用FPGA平台发生150 MHz随机码可以获得高达1 m的分辨率; (6)采用低电压差分信号LVDS输出后使得码片具有良好的动态特性,保证在脉冲压缩时将具有优良的信噪比。

参考文献:

[1]Lewis B L.Range-Time-Sidelobe Reduction Technique for FM-Derived Polyphase PC Codes[J].IEEE Transactions on Aerospace and Electronics Systems,1993,29(3) : 834-863.

[2]Varschney L R,Thomas D.Sidelobe Reduction for Matched Range Processing[C].2003 IEEE Radar Conference,2003: 446-451.

[3]Merrill I,Skolnik.Radar Handbook[M].3rd ed.New York: McGraw-Hill,2008: 401-410.

[4]Levanon N,Mozeson E.Radar Signals[M].New York: IEEE Press,2004:106,145.

[5]Felhauer T.Design and Analysis of New P(n,k) Polyphase Pulse Compression Codes[J].IEEE Transactions on Aerospace and Electronics Systems,1994,30(3) :865-874.

[6]秦新峰,郭倩颖,王光义.基于ARM的混沌序列的产生及其性能分析[J].电子器件,2011,34(3) :346-349.

[7]杜斌峰,王智敏,孙跃.基于FPGA的数字混沌序列的实现及性能分析[J].电子器件,2011,34(4) : 477-481.

[8]闫海煜.一种新的TDCS基函数随机相位产生方法及性能分析[J].电子器件,2014,37(3) : 574-578.

[9]王光义,袁方.级联混沌及其动力学特性研究[J].物理学报,2013,62(2) : 111-120.

[10]张仁民,钱莹晶,伍清.高分辨率测距雷达系统宽带调制解调器[J].电子器件,2013,36(3) : 344-348.

[11]赵秋明,王龙飞,翟江辉.基于LVDS技术的高速数据传输系统设计[J].计算机测量与控制,2012,20(11) : 3035-3037.

[12]郭桂林,李文钧.RFID系统的串扰分析及消除[J].电子器件,2012,35(1) : 99-102.

钱莹晶(1983-),女,汉族,湖南溆浦人,湖南怀化学院讲师,硕士研究生,主要研究方向为实时信号处理、高性能电路,17204506@ qq.com;

张仁民(1981-),男,汉族,湖南冷水江人,湖南怀化学院副教授,博士研究生,主要研究方向为实时信号处理、嵌入式仪器仪表,zrm@ pku.edu.cn。

Design of Low-Power 11-bit ADC Based on the Hybrid Architecture*

TIAN Deyong1*,HUANG Weichao2

(1.GuizhouVocational and Technical Institute,Guiyang 550000,China; 2.Guizhou University,College of Big Data and Information Engineering,Guiyang 550025,China)

Abstract:This paper presents a new type of low power 11-bit ADC based on Flash architecture and delay line architecture.The new hybrid ADC architecture is composed of two modules,respectively is 4 bit Flash ADC framework and 7 delay line ADC architecture,therefore also has the accuracy of Flash ADC and efficiency of the delay line ADC.In order to reduce power the first phase of Flash ADC,the energy saving technology will DC tail current preamplifier by biasing the DC tail current of the preamplifiers at 5 μA instead of the operational current,47 μA(in stand-by mode).Through the use of industrial 65 nm technology,design and Simulation of a hybrid ADC is proposed in this paper.The simulation results show that,with 1.1 V supply and 100 Msample/s,hybrid ADC signal-to-noise distortion ratio (SNDR) is 60dB,the power consumption is 1.6 mW.Without any calibration technique,the quality factor of hybrid ADC generation(FOM) into 19.4 fJ/classification.In addition,this paper uses the Monte Carlo simulation test,using the 3 device does not match the results show that,SNDR value is lower than the ADC architecture.

Key words:Hybrid ADC; delay line architecture; Flash; subtracter

中图分类号:TN958.3

文献标识码:A

文章编号:1005-9490(2015) 03-0558-04

收稿日期:2014-07-30修改日期:2014-09-23

doi:EEACC: 1270F; 1290B10.3969/j.issn.1005-9490.2015.03.018