超高压BCD工艺中多晶硅电阻的可靠性分析及实现

2015-02-26包飞军葛艳辉石艳玲华东师范大学信息科技与技术学院上海004上海华虹宏力半导体制造有限公司上海006

包飞军,曹 刚,葛艳辉,石艳玲*,陈 滔,(.华东师范大学信息科技与技术学院,上海004; .上海华虹宏力半导体制造有限公司,上海006)

超高压BCD工艺中多晶硅电阻的可靠性分析及实现

包飞军1,曹刚2,葛艳辉2,石艳玲1*,陈滔1,2

(1.华东师范大学信息科技与技术学院,上海200241; 2.上海华虹宏力半导体制造有限公司,上海201206)

摘要:多晶硅电阻由于其独特的温度特性及电迁移效应,阻值受温度和电流的影响很大,针对应用于超高压BCD工艺中的多晶硅电阻,其可靠性需进行特别分析和设计。通过对0.18 μm 700 V BCD工艺中不同掺杂浓度多晶硅电阻的测试与分析,结合多晶硅结构、导电机制、焦耳热效应及电迁移理论,分析了焦耳热和电迁移对多晶硅电阻的影响,并实现了高压BCD工艺中高可靠性的多晶硅电阻。

关键词:超高压BCD;多晶硅电阻;可靠性;焦耳热效应;电迁移

多晶硅是广泛用于实现MOSFET多晶硅栅电极、局部互连线、传感器、高值电阻等[1],制作超大规模集成电路非常重要的一种材料,同时在太阳能电池和薄膜晶体管中也有很重要的应用[2-3]。采用多晶硅实现的高值电阻具有许多优点,如面积小、线性好、电阻值宽范围可调等。

BCD工艺是将高速强负载驱动能力Bipolar器件、高集成低功耗CMOS器件及高压DMOS功率器件相结合的单片集成电路制造工艺,可实现高速器件与低功耗器件、高压器件与低压器件的结合[4-5]。在BCD工艺中,可考虑采用多晶硅实现电阻,起到调节电流,承载分压,实现器件间不同电压转换的作用。但电阻稳定性将影响到电路中电压的稳定与电路功耗,因此,高可靠性的多晶硅电阻设计对实现稳定的超高压BCD电路尤为重要[6]。

1 焦耳热效应对多晶硅电阻的影响

1.1多晶硅电阻温度特性的理论分析

根据1975年Seto提出的多晶硅物理模型[7],多晶硅由许多小单晶硅晶粒组成的,晶粒间界处有大量的悬挂键和缺陷,形成能俘获载流子的陷阱。陷阱俘获载流子后带电,形成势垒,阻止载流子的迁移,使迁移率下降。其后,Mandurah等人[8]和Lu等人[9]也提出过类似的多晶硅电阻模型,且指出多晶硅晶粒边界处悬挂键和缺陷形成的载流子俘获态的数量是恒定的。因此,多晶硅电阻R(T)由小单晶硅粒电阻Rg(T)和晶粒间界电阻Rgb(T)共同决定,

式中:Wg为单个小单晶硅粒的宽度,Wgb为单个晶粒间界宽度,W等于Wg与Wgb之和。

对于高掺杂浓度多晶硅电阻,小晶粒中载流子数远大于晶粒间界俘获的载流子数,阻值主要由Rg(T)决定。随着温度的升高,晶格震动散射增强,载流子迁移率下降,Rg(T)增大,多晶硅电阻增大,具有正的电阻温度特性。对于低掺杂浓度的多晶硅,晶粒间界处俘获的载流子数远大于小晶粒中载流子数,Rgb(T)影响占据主导地位。随着温度升高,载流子获得的能量增大,晶粒间界处俘获的载流子更易克服势垒的束缚,成为自由载流子,参与导电,Rgb(T)随温度升高而减小,多晶硅电阻随温度升高而变小,表现出负的电阻温度特性。

1.2多晶硅电阻焦耳热对阻值的影响

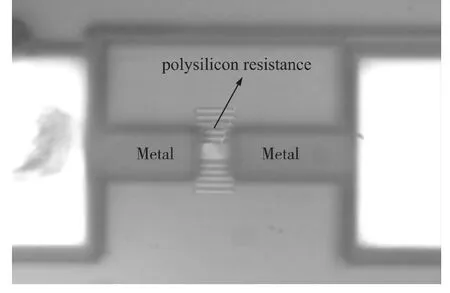

实验中,根据0.18 μm 700 V BCD工艺,制作了形状、长宽相同,掺杂浓度不同的3种多晶硅电阻,其位置如图1显微镜照片所示,各电阻掺杂浓度及常温方块电阻值如表1所示。

图1 BCD工艺中多晶硅电阻的显微镜照片

表1 三种多晶硅电阻及其对应掺杂浓度的设计

Qualita Mira EM可用于测试焦耳热效应对多晶硅电阻阻值的影响,通过在多晶硅电阻的两端通快速变大的电流,电流产生的焦耳热效应会使多晶硅电阻温度升高,从而阻值发生变化。

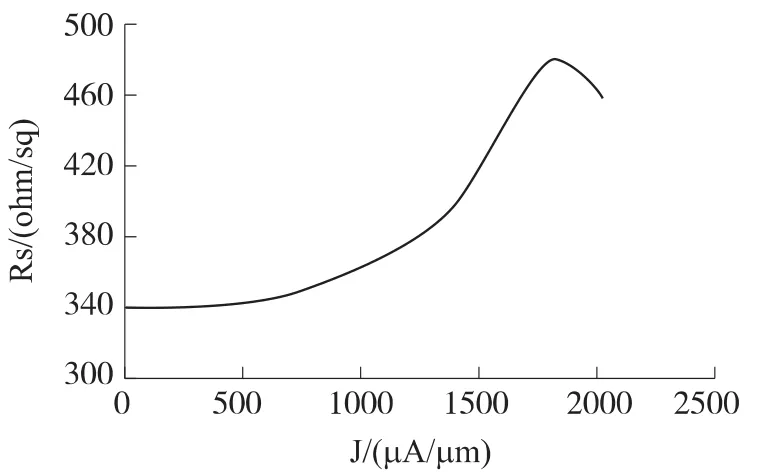

低值多晶硅电阻阻值随电流密度变化的测试曲线如图2所示。首先随着电流密度的快速增大,焦耳热效应使多晶硅电阻温度升高,阻值随之增大,表现出正的温度特性。随后,低值多晶硅电阻值随电流增大到一定值后,出现了随电流增大而变小的现象,这是因为此时多晶硅内的热激发激烈,随着温度升高,本征载流子急剧增多,对多晶硅电阻起主导作用,导致电阻率减小。

图2 低值多晶硅阻值随电流密度的变化

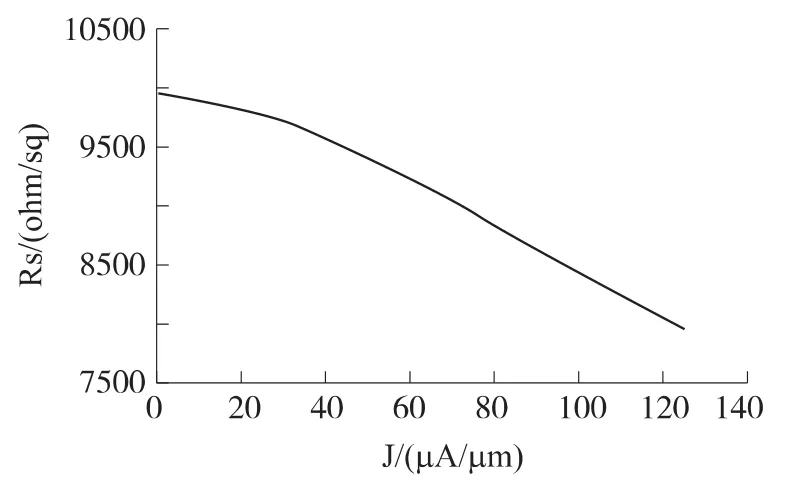

图3和图4分别是中值和高值多晶硅电阻阻值随电流变化的测试曲线,阻值均随着电流密度的增大而减小,且高值多晶硅电阻阻值随电流密度增大而减小的斜率绝对值大于中值多晶硅电阻。这是因为掺杂浓度低于一定值后,多晶硅电阻具有负温度特性,且掺杂浓度越低、负温度特性越明显。

图3 中值多晶硅阻值随电流密度的变化

图4 高值多晶硅阻值随电流密度的变化

2 电迁移对多晶硅电阻的影响

2.1电迁移原理

对电迁移Electromigration的研究始于金属互连线,是指互连线在电流和温度作用下产生的电子流碰撞原子,发生的原子迁移的现象[10]。常用电迁移中值失效时间(MTF)来描述电迁移引起的失效。中值失效时间指同样的直流电流试验条件下,50%的互连引线失效所用的时间,失效判据为引线电阻增加10%。直流模型下描述电迁移失效中值时间的经典公式是Block公式[11]

式中:A为常数; J为电流密度; n为电流密度指数; Ea为扩散激活能; k为玻耳兹曼常数; T为绝对温度。MTF与电流密度和温度密切相关。

2.2多晶硅电迁移现象及分析

可用Qualita Mira电迁移采用高温加速测试的方法测试多晶硅电阻的电迁移,保持温度不变在多晶硅电阻的两端通恒定的电流,测试多晶硅电阻阻值随时间的变化。实验采用了若干形状、长宽均相同,掺杂浓度为3.8×1014/cm3的中值电阻(如表1所示)。

图5是温度为250℃时,在多晶硅两端分别加2 mA、4 mA、6 mA恒定电流、多晶硅电阻阻值随时间变化的关系。如图5所示,通电流一定的时间后,多晶硅阻值均出现随着时间的增加而逐渐增大的现象,即出现了电迁移,且所通电流越大,电阻值增大越快,电迁移越严重,失效时间越短。

图5 恒温恒流条件下多晶硅阻值随时间的变化

根据式(2) Block方程,可得:

式中:B、C为常数。

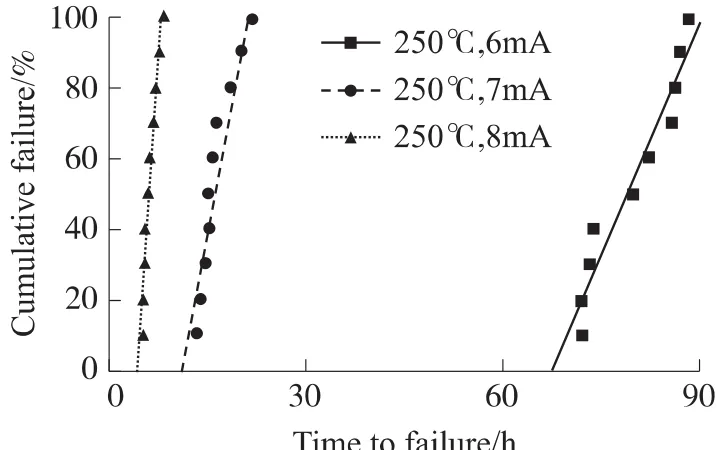

在相同的温度下测试3组不同电流密度下多晶硅电阻的MTF(图6),根据式(3)即可计算出多晶硅电阻的n值。计算等到n为9.23,去除焦耳热影响后n为5.96。同理,在相同的电流密度下测试三组不同温度下多晶硅电阻的MTF (图7),根据式(4)即可计算出多晶硅电阻的Ea值,Ea为0.61。

图6 250℃,7/6/8 mA多晶硅电阻累计失效率

图7 7 mA,200/225/250℃多晶硅电阻累计失效率

Ea和n的大小被认为反映了电迁移失效的物理机制。如果电迁移失效过程以晶界扩散为主,则n一般小于2,若n大于3,则认为电流导致的拥挤效应或焦耳热效应已经在电迁移过程中起了很大作用。多晶硅电阻的n值高达9.23,去除焦耳热影响后,n值也高达5.96,这说明电流密度对多晶硅电迁移的影响很大,分析认为由于多晶硅是由小晶粒组成的,因此晶粒间界处电流拥挤效应强烈,且晶粒间界处原子键合力弱,在大电流的作用下更容易出现电迁移,产生空洞,因而使得电阻率剧增。

3 高可靠性多晶硅电阻的实现

焦耳热效应和电迁移效应是影响多晶硅电阻可靠性的两个主要因素,特别是在超高压BCD工艺中,容易在接入高压的多晶硅电阻上产生较大的电流,从而产生失效。

结合表1数据,比较图2和图3的实验结果可知,随着掺杂浓度的增加,多晶硅电阻的温度特性会由正变为负,因此存在某一特定掺杂浓度的多晶硅电阻,其电阻温度系数为0,这和多晶硅的制造工艺有关;电迁移效应是长时间通电流产生的效应,因此对于有高精度要求、非长时间工作电阻的应用,可采用这一特定掺杂浓度的多晶硅电阻。利用不同掺杂浓度的多晶硅电阻温度特性可正可负的特性,对于误差允许稍偏正电阻的应用可采用温度特性为正的重掺杂多晶硅电阻;而对于误差允许稍偏小电阻的应用可采用温度特性为负的轻掺杂多晶硅电阻。

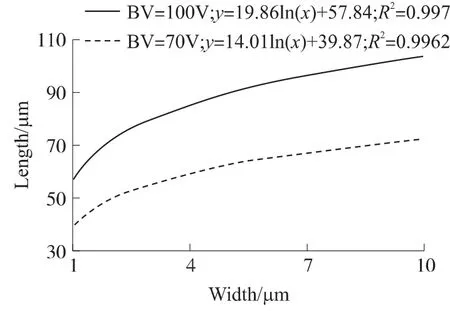

通过调节多晶硅电阻宽长比可设计高可靠性电阻。图8是方块电阻为2 kΩ/sq多晶硅电阻击穿电压BV(BV定义为多晶硅电阻值变化10%所能承受的电压,单位为伏特V)随长宽变化的测试及采用最小二乘方法拟合的结果。测试结果表明,BV随W的减大而减小,随L的增大而增大;拟合结果表明,BV与多晶硅电阻的长度成严格的正比关系(线性拟合相关系数R2均大于0.999),但斜率随着宽度的增大而减小。因此可根据电阻击穿电压的要求来挑选电阻尺寸,根据宽长关系获得合适阻值的多晶硅电阻。图9为根据图8线条尺寸选择设计的BV分别为70 V和100 V的2 kΩ/sq多晶硅电阻。

图8 多晶硅电阻BV(V)与结构尺寸的关系

图9 BV为70 V和100 V时2 kΩ/sq多晶硅电阻长宽关系

4 总结

本文分析了影响多晶硅电阻可靠性的两个主要因素焦耳热效应和电迁移效应对多晶硅电阻阻值的影响;开展了0.18 μm 700 V BCD工艺中多晶硅电阻可靠性的研究,提出了超高压BCD工艺中高可靠性多晶硅电阻的设计方法,对该工艺中多晶硅电阻的设计具有指导作用。

参考文献:

[1]Adari R B R,Suresh S,Prabhu R D.Hardware Validated TCAD Simulation of Polysilicon Resistor Including Trap Physics and Self-Heating[J].IEEE Electron Devices and Solid State Circuit (EDSSC) International Conference,Dec 2012:1-4.

[2]Bwcker C,Amkreutz D,Sontheime R T,et al.Polycrystalline Silicon Thin Film Solar Cells:Status and Perspectives[J].Solar Energy Materials and Solar Cells,2013:122-123.

[3]Green M A.Polycrystalline Silicon on Glass for Thin-Film Solar Cells[J].Applied Physics:A,2009,96(1) :153-159.

[4]Boulais E,Fantoni J,Chateauneuf A,et al.Laser-Induced Resistance Fine Tuning of Integrated Polysilicon Thin-Film Resistors[J].IEEE Transactions On Electron Devices,2011,58(2) :572-575.

[5]孙伟锋,张波,肖胜安,等.功率半导体器件与功率集成技术的发展现状与展望[J].中国科学,2012,42(12) :1616-1630.

[6]Venturato M,Cantone G,Ronchi F,et al.A Novel 0.35 μm 800 V BCD Technology Platformfor Offline Application[C]/ / Proceedings of the 2012 24th International Symposium on power Semiconductor Devices and ICs[s.l.]:IEEE,2012:397-400.

[7]Seto John Y W.The Electrical Properties of Polycrystalline Silicon Films[J].Applied Physics,1975,46(12) :5247-5254.

[8]Mandurah M M,Saraswat K C,Kamins T I,et al.A Model for Conduction in Polycrystalline Silicon—PartⅠ:Theory[J].IEEE Transactions on Electron Devices,1981,28(10) :1163-1171.

[9]Lu N C C,Gerzberg L,Lu C Y,et al.A Conduction Model for Semiconductor-Grain-Boundary-Semiconductor Barriers in Polycrystalline-Silicon Films[J].IEEE Transactions on Electron Devices,1983,30(2) :137-149.

[10]Wu K,Bradley R M.Theory of Electromigration Failure in Polycrystalline Metal Films[J].Phys Rev B,1994,50(17) :12468-12487.

[11]Black J R,Electromigration Failure Models in Aluminum Metallization for Semiconductor Devices[J].Proc of the IEEE,1969,57(9) :1587-1594.

石艳玲(1969-),女,汉族,华东师范大学微电子专业教授、博导,主要从事VLSI技术核心器件、模型及应用研究。承担国家及上海市研究课题近10项,在国内外核心刊物上发表论文逾40篇,SCI检索5篇,ylshi@ee.ecnu.edu.cn。

Research of MEMS Bionic Vector Hydrophone Vibration Control

YANG Jiangtao1,2,MA Xihong1,2*,WU Qi3

(1.Science and Technology on Electronic Test and Measurement Laboratory,North University of China,Taiyuan 030051,China; 2.Key Laboratory of Instrumentation Science and Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China 3.School of Computer Science and Control Engineering,North University of China,Taiyuan 030051,China; )

Abstract:One kind of anti-shock packaging model for the bionic vector acoustic hydrophone in the acoustic sensor system have been built by using of anti-shock principle.A new package model has been designed by adding a new rubber damper package.The modal analyses have been made to study on the structure and dimension effects on the anti-shock performance of the model so as to select the optimum packaging structure,and the optimum packaging model with the lowest natural frequencies has been gained by optimizing the dimension of the model and material parameters of the rubber by using ANSYS.In the end,the anti-shock performance of the optimum model has been tested and evaluated.Experimental results show that the designed rubber damping structure has a certain damping effect and Isolated a certain level of external vibration disturbances outside the core device.Moreover,it improved the detection sensitivity of original packaging structure vector hydrophone.The verified MEMS silicon micro-bionic underwater acoustic vector sensor is not only small size,light weight,simple structure,and has a low frequency and high sensitivity.Key words:MEMS bionic vector hydrophone; finite element analysis; anti-shock packaging; packaging system

中图分类号:TN36

文献标识码:A

文章编号:1005-9490(2015) 03-0495-04

收稿日期:2014-07-09修改日期:2014-08-03

doi:EEACC:0170J; 782010.3969/j.issn.1005-9490.2015.03.006