一种低功耗高精度带隙基准的设计*

2015-02-23冯全源

李 睿,冯全源

(西南交通大学 微电子研究所,四川 成都611756)

一种低功耗高精度带隙基准的设计*

李 睿,冯全源

(西南交通大学 微电子研究所,四川 成都611756)

基于UMC 0.25 μm BCD工艺,在传统带隙基准结构的基础上,设计了一种具有低功耗、高精度的基准,同时利用NMOS管工作在亚阈值区域时漏电流和栅极电压的指数特性,对基准温度特性曲线进行二阶补偿。仿真结果表明,电源电压5 V时,静态电流功耗为3.16 μA;电源电压2.5 V~5.5 V,基准电压变化 53 μV;温度在-40℃~130℃内,电路的温度系数为 0.86×10-6/℃;三种工艺角下,低频时电路电源抑制比都小于-95 dB。

带隙基准;功耗;曲率补偿;低温漂

0 引言

近年来,随着电子产品特别是智能电子产品硬件的不断普及,对芯片的功耗和性能提出了越来越苛刻的要求[1]。

基准源(简称基准)是模拟芯片所必不可少的基本部件,它为电路提供高质量、高稳定性的电流和电压偏置,而且它的性能会直接影响到电路的性能[2]。传统基准存在精度低、温漂大、功耗高和失调电压高等缺点[3-4]。本文基于传统基准提出了一种低功耗基准,以期克服这些缺点。

1 带隙基准的基本原理分析

对于一个双极型晶体管(BJT)的基极-发射极电压(VBE),更一般的是 pn结二极管的正向电压,具有负温度系数[5]。BJT的 VBE、集电极电流 IC和饱和电流 IS有以下关系:

其中,k为玻尔兹曼常数,T表示热力学温度,q为电荷,μ为少数载流子的迁移率,ni为硅的本征载流子浓度[6]。

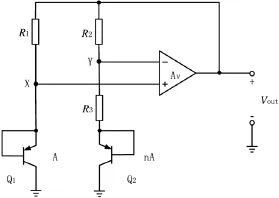

两个双极型晶体管工作在不同的电流密度下,它们之间的基极-发射极电压之差(ΔVBE)具有正温度系数[7]。将以上两个具有相反温度系数的变量加以适当的权重,就可以得到满意的零温度系数基准[8]。图1是传统的带隙基准电路,这里,运算放大器AV以VX和VY为输入,AV输出用于驱动 R1和 R2(R1=R2)的顶端,使得 X点和 Y点稳定在近似相等的电压。基准电压可以在运算放大器的输出端得到(不是Y点)[9]。三极管基极-发射极电压VBE具有负温度系数。三极管Q2和Q1发射极有效面积比例为n:1,流过两者的饱和电流和集电极电流存在以下关系:

图1 传统带隙基准

三极管Q2和Q1的基极-发射极电压之差:

ΔVBE作用在电阻 R3上,产生PTAT电流,使得 R1上产生PTAT电压[10],此电压和VBE相叠加,得到输出电压:

VT具有正温度系数,通过调节 R2、R3和三极管面积比例得到零温度系数电压,实际电路中基准电压温度系数是一个开口向下的曲线。VBE具有高阶的温度分量,所以需要对VBE进行高阶补偿。

针对传统带隙基准启动失调电压大、精度低的特点,本文提出了具有低功耗高精度的电压基准。电路由两个部分组成,分别为启动偏置电路、基准核心电路(基准电压产生和补偿结构、基准运放),实际原理图如图2所示。

图2 低功耗高精度带隙基准

2 新型带隙基准电压源设计

2.1 启动电路和PTAT偏置电路

为了摆脱电源上电时电路的简并偏置点,启动电路是不可缺少的。本设计中启动电路由 R2、C1、NM0、NM1、NM4组成。电路正常上电时,VDD通过R2向电容C1充电,NM0的栅极电压升高,使 NM0和 NM4导通,PM1、PM4的栅极电压拉低,偏置电路源开始正常工作;随着NM2栅电压逐渐升高,NM1导通,NM0和 NM4栅极电压被拉低,NM0和 NM4截止,此时关闭启动电路。

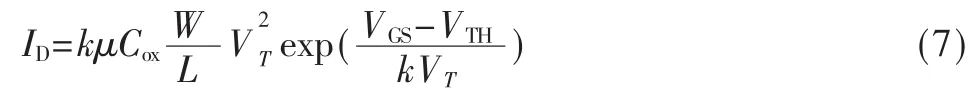

偏置电路为整个电路提供一个与电源无关的PTAT偏置电流。如图2,偏置电路是由PM1、PM2、PM3、PM4、NM2、NM3和R1构成的自偏置峰值电流源。PM1~PM4的宽长比相同,构成了 Cascode电流镜,形成自偏置机制,同时增加整体电路的电源抑制比。利用NM2和NM3工作在亚阈值区域时的栅源电压之差作用在电阻R1产生正温度系数的电流。在亚阈值区域时,MOS管漏电流ID为:

式中k为亚阈值斜率修正因子,VTH为MOS管阈值电压[11]。漏源电压 VGS远大于 VT,式(6)可简化为:

可以推导出PTAT偏置电流为:

式中m为NM3和NM2宽长比之比。从式(8)可以看出,VT具有正温度系数,所得偏置电流与温度成正比和电源电压无关。

2.2 带隙基准核心电路

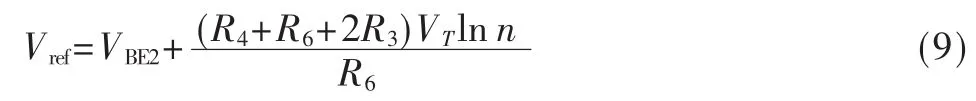

本文设计的基准产生电路由 Q1、Q2、R3~R6、PM12和PM13组成。Q2和 Q1的有效发射极面积之比为 n:1,电阻R4和R5的阻值相等。根据上文式(1)~(5)的推导,可以得出基准电压 Vref的表达式:

晶体管的VBE并不是与温度呈线性关系:

式中,VBG0是带隙电压,约为 1.12 V;T是绝对温度;T0是参考温度;VBE0是在温度为 T0时的发射结电压;η是与工艺有关且与温度无关的常数;α的值与集电极电流的温度特性有关。调节三极管和电阻选取的大小,能很好地对式(10)中的第一项进行补偿。为了得到更低的温度系数,必须对式(10)中的第二项进行补偿。

本设计提出了一种简单且效果明显的补偿方式,利用NMOS管工作在亚阈值区域时漏电流和栅极电压的指数特性,对基准电压进行二阶曲率补偿。补偿电路由NM8、R7、R8、PM14、PM15组成,补偿基准在高温下的温度特性曲线。PM14和PM15镜像PTAT电流,作用在电阻 R7上,产生PTAT电压,该电压使NM8工作在亚阈值状态,随着温度的增加,补偿电流逐渐增大。由式(6)和式(7),可得:

忽略 R8上的压降,补偿电流:

式中ρ是 PM14和 PM15的镜像比例因子。加上二阶曲率补偿电流后,式(9)可改写为:

运算放大器由PM5~PM11、NM5~NM7和C2组成。本设计采用两级运放结构,具有较大的开环增益。同时运用PM11输出跟随器,减小输出电阻。为了减小运放的失调电压,加大了PM9和 PM10的宽长比,并保证了一级运放和二级运放之间的对称性。电容C1作为补偿电容,得到一个低频极点,增加电路的稳定性。

3 仿真结果

本文设计电路采用 UMC 0.25 μm BCD工艺模型,电路中n=8,m=2。利用Hspice仿真软件,对电路进行了仿真。

在TT工艺角下。温度为25℃时,基准电压线性调整率如图3所示。仿真结果表明,基准电压的典型值为1.203 V。供电电压VDD在2.5 V~5.5 V范围内,基准电压变化了53 μV,线性调整率为0.001 8%。供电电压VDD为5 V,在-40℃~130℃的温度范围内,基准电压的温度特性仿真结果如图4所示。仿真结果表明,基准电压的平均值为1.203 V,基准电压的波动范围为175 μV,温度系数为 0.86×10-6/℃。

图3 基准电压线性调整率

图4 基准电压温度特性曲线

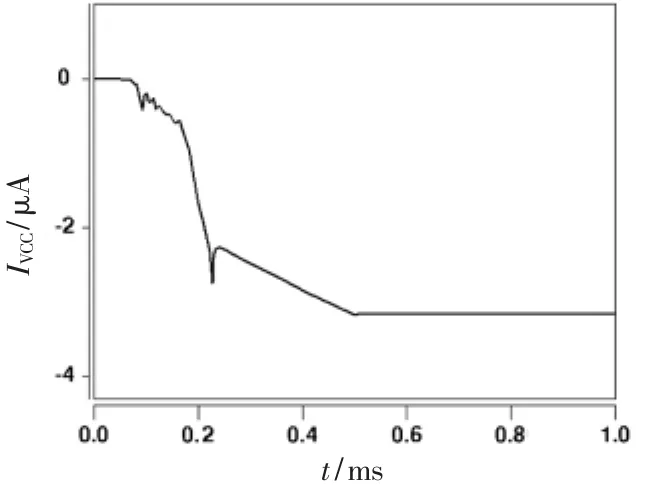

如图5为电源电压VDD为5 V,温度为25℃,在三种工艺角下的电源抑制比(PSRR)仿真结果,在三种工艺角下低频 PSRR都小于-95 dB,具有很好的电源抑制能力。图6为瞬态仿真下的电流功耗大小,从仿真结果可以看出,电路的静态电流功耗为3.16 μA。

图5 基准电压电源抑制比

图6 基准静态功耗电流

表1为本文和文献[2]、[8]和[9]的性能参数比较。本文提出的结构具有明显优势。

4 结论

提出了一种基于传统结构的低功耗、高精度的带隙基准电压源。本设计采用Cascode结构来提高整体电路的电源抑制比。通过增加运放输入差分对管的尺寸,添加输出缓冲级结构以及保证运放的对称性来减小失调电压。并运用二阶曲率补偿来对基准电压进行温度补偿。采用UMC 0.25 μm BCD工艺,仿真结果表明,基准电压源在2.5 V~5 V的电压范围内提供 1.203 V的基准电压,线性调整率为 0.001 8%,静态功耗只有 3.16 μA,在-40℃~130℃温度范围内的温度系数为0.86 ppm,低频电源抑制比为-95 dB。

表1 带隙基准性能比较

[1]Chen Junda,Ye Chengkai.Design of a CMOS bandgap reference circuit with a wide temperature range,high precision and low temperature coefficient[J].Journal of Circuits,System,and Computers,2014,23(8):1450107.

[2]朱龙飞,莫太山,叶甜春.高电源抑制比低温漂带隙基准源设计[J].集成电路应用,2013,39(5):35-38.

[3]Lu Shibi.A 19-ppm/℃bandgap voltage reference source[C]. Networks Security Wireless Communications and Trusted Computing,Wuhan:IEEE,2010:409-411.

[4]杨晓春.一种采用斩波调制的高精度带隙基准源的设计[J].微电子学与计算机,2013,30(1):86-89.

[5]GRAY P R.Analysis and design of analog integrated circuits[M].America:Lehigh Press,2001.

[6]Feng Chao,Wang Jinhui,Wu Wei.CMOS 1.2 V Bandgap Voltage Reference Design[C].IEEE 10th International Conference on ASIC,Shenzhen:IEEE,2013:1-4.

[7]RAZAVI B.模拟 CMOS集成电路设计[M].陈贵灿,程军,译.西安:西安交通大学出版社,2002.

[8]唐宇.一种低温漂低功耗带隙基准的设计[J].电子元件与材料,2014,33(2):35-38.

[9]Zhang Kun.A high performance bandgap voltage reference design[C].Information Science and Engineering(ICISE),2010 2nd International Conference on,Hangzhou:IEEE,2010:4838-4841.

[10]魏廷存,陈莹梅,胡正飞.模拟 CMOS集成电路设计[M].北京:清华大学出版社,2010.

[11]林少波.高精度高电源电压抑制比CMOS带隙基准源设计[D].西安:西安电子科技大学,2012.

表2 整个芯片的性能

参考文献

[1]LEE C F,MOK P K T.A monolithic current-model cmos DC-DC converter with on chip current-sensing technique[J]. IEEE Journal of Solid-State Circuits,2004,39(1):3-14.

[2]Deng Haifei.Monolithically integrated boost converter based on 0.5 μm cmos process[C].IEEE Int.Symp.On Power Semiconductor Devices&ICs,2004:169-172.

[3]MORROW P,GAALAAS E.A 20-W stereo class-D audio output power stage in 0.6 μm BCDMOS technology[J]. IEEE Journal of Solid-State Circuits,2004,39(11):1948-1958.

[4]HOWER P L.Safe operating area-a new frontier in LDMOS design[C].Proc.14th Int.Symposium on Power Semiconductor Devices and ICs,2002:1-8.

[5]BERKHOUT M.An integrated 200-W class-D audio amplifier[J].IEEE Journal of Solid-State Circuits,2003,38(7):1198-1206.

[6]FORGHANI-Z H P,RINCON-M G A.Current-sensing techniques for DC-DC converters[C].Proc.of IEEE MWSCAS.2002:557-580.

(收稿日期:2014-10-19)

作者简介:

郑浩(1979-),男,硕士,讲师,主要研究方向:集成电路设计与研究。

Design of a bandgap reference voltage with low power consumption and high-accuracy

Li Rui,Feng Quanyuan

(Institute of Microelectronics,Southwest Jiaotong University,Chengdu 611756,China)

A new bandgap reference voltage with low consumption and high-accuracy performance,which is based on UMC 0.25 μm BCD process and the traditional bandgap reference construct.It uses the exponential response curve between leakage current and grid voltage when the N type MOS-FET is working in the sub-threshold region to compensate the temperature characteristic curve.The simulation shows that quiescent current is 3.16 μA when power supply is 5 V.The change amplitude of reference voltage is 53 μV when the power supply is from 2.5 V to 5.5 V.The temperature coefficient is 0.86×10-6/℃ from-40℃ to 130℃. The PSRR is lower than-60 dB at the three process corner.

bandgap reference;power consumption;curvature-compensation;low temperature drift

TN433

:A

:0258-7998(2015)03-0051-04

10.16157/j.issn.0258-7998.2015.03.012

2014-11-07)

李睿(1990-),男,硕士研究生,主要研究方向:模拟集成电路设计。

冯全源(1963-),通信作者,男,博士,教授,博士生导师,主要研究方向:数字、模拟及射频集成电路设计,Email:fengquanyuan@163.com。

国家自然科学基金重大项目(60990323);国家自然科学基金面上项目(61271090)