12V,3A电流模同步Buck DC-DC转换器功率级设计

2015-02-23王道平

郑 浩,刘 岩,王道平,姚 鹏

(第二炮兵工程大学,陕西 西安710025)

12V,3A电流模同步Buck DC-DC转换器功率级设计

郑 浩,刘 岩,王道平,姚 鹏

(第二炮兵工程大学,陕西 西安710025)

采用0.35 μm 18 V DPTM BCD工艺技术给出电流模降压型DC-DC转换器的功率级设计,该功率级可以输出3 A负载电流,转换效率可达到94.5%。主要针对转换器中核心部分功率级进行设计,其中包括同步开关功率晶体管设计、片上电感电流检测电路、功率晶体管驱动电路设计以及功率级的版图设计考虑,最后给出了该功率级设计的测试结果。

电流模;同步DC-DC转换器;功率级;BCD

0 引言

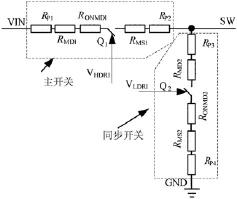

当前,数字多媒体、视频广播设备、个人导航设备(PND)、车载电源设备的使用越来越广泛,为这些设备提供电源管理,常需要具有高压大电流高转换率效的DC-DC转换器。为了减小设备体积和重量,电源模块必须最小化,因此,实现转换器的高转换效率以及高集成度成为一种趋势[1-2]。考虑到电压控制模式和非同步转换器的一些缺点,更多的系统选择使用同步电流模式DC-DC转换器;图1为典型电流模同步 BUCK转换器的电路框图,图中阴影部分为转换器的功率级,而电流控制模式BUCK DC-DC转换器中功率级的设计是最重要的功能模块之一,亦是转换器设计的难点所在,原因在于:功率级中作为开关的功率晶体管导通电阻会影响系统转换器的效率,在大负载电流条件下,功率开关晶体管的导通电阻还会影响芯片的热设计,一般来讲,功率开关的导通电阻与其宽长比成反比,但大尺寸器件会导致更大的芯片面积,增加芯片的成本,缺少市场的竞争力,怎样能够在减小导通电阻和芯片面积之间找到合适的折中点是功率晶体管设计的关键;其次,功率晶体管在版图设计时的寄生效应也会影响转换器的性能,功率晶体管的版图优化是功率级设计的一个重要部分;最后,电流模转换器需要对电感电流进行检测,设计合适的低功耗电感电流检测电路亦是功率级设计的难点。

图1 电流模同步BUCK DC-DC转换器电路框图

基于上面的考虑,本文将以电流模式控制同步降压型DC-DC转换器为例,设计输入电压最大为 18 V、典型输出电压为5 V、能够提供3 A负载电流的功率级。

1 同步功率晶体管设计

对于单片高压大电流集成DC-DC转换器,功率级设计极具挑战性,特别是高压功率开关采用LDMOS晶体管,在大电流下需要考虑以下几个方面:DMOS晶体管会寄生双极性晶体管,当晶体管流过一定的电流,晶体管的漏极和源极电压会增加到击穿电压,然后漏源电压将回跳到一定的低值[3-4];其次,在负载电流比较大时,芯片封装时引线产生的寄生电阻[5]将不能忽略不计,如图 2所示,RP1~RP4为芯片封装引线产生的寄生电阻,为了能够减小其寄生电阻,在芯片封装时,PAD与封装管脚之间引线要避免过长;图 2中,RONMD1为主功率开关导通电阻,RONMD2为同步开关的导通电阻;Q1和 Q2是由驱动电路控制的理想开关。

图2 同步转换器功率开关等效电路

主开关的等效直流导通电阻RHS如下式所示:

其中:RMD1和RMS1分别为主开关功率晶体管版图设计时漏极和源极金属连线产生的寄生电阻,该电阻主要由金属连线的物理设计决定。

同步开关的等效直流导通电阻RLS如下式所示:

其中:RMD2和RMS2分别为同步开关功率晶体管版图设计时漏极和源极金属连线产生的寄生电阻,该电阻主要由晶体管的物理设计决定。

主功率开关和同步开关晶体管一般选用N沟道LDMOS晶体管,原因在于N沟道LDMOS晶体管的电子迁移率大于P沟道LDMOS晶体管空穴迁移率,对于相同大小的导通电阻,LDNMOS晶体管的面积仅为 LDPMOS晶体管面积的 1/2~1/3[3],本文设计主开关和同步开关等效直流导通电阻RHS和RLS约为88 mΩ。

2 电感电流检测电路

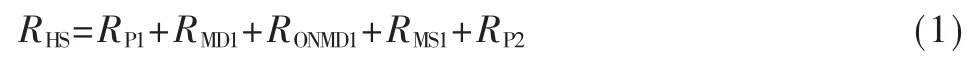

电流模式DC-DC转换器中,电感电流的检测是智能功率芯片非常重要的功能之一,因此也衍生了多种电感电流检测的方式[6]。

本文对电感电流检测的方式采用间接检测方式,图 3给出电路结构,当主开关功率(MD1)晶体管导通时,MD1的漏极电流等于电感流过的电流,为了避免直接检测MD1电流会导致消耗更大的功耗,不利于系统的效率提高,本设计采用等比例检测主开关MD1的漏极电流,然后通过在比例晶体管MD2的漏极连接一个较小的电阻将比例电流转换成电压 VSENS,这样的优点在于:采样电流的功耗较低,由于采样电阻连接在晶体管的漏极,电流的比例系数精确。下面给出 VSENS的计算公式:

图3 片上电感电流检测电路

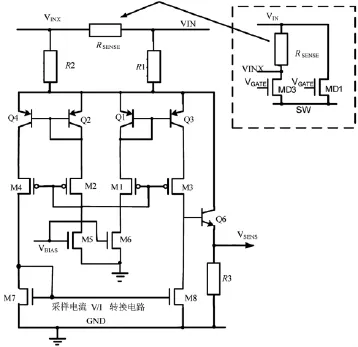

3 同步功率晶体管驱动电路设计

在降压型DC-DC转换器中,主开关晶体管使用N沟道LDMOS晶体管,为了能够驱动该功率开关晶体管,需要集成片上自举电路才能驱动LDNMOS功率晶体管。

由于转换器采用同步工作模式,主开关和同步整流开关交替导通,为避免主开关和整流开关同时导通可能造成的功率晶体管的损坏,以及损失转换器的效率,同步驱动电路还需要采用死区时间控制逻辑电路,详细电路图如图4所示。当同步整流开关关闭时,同步整流开关管的寄生二极管导通,但死区时间不能太大,否则会导致由于寄生二极管导通时间过长,造成转换效率降低。

图4 同步功率开关晶体管驱动电路

功率级的输入电源电压范围为5~18 V,功率开关晶体管的栅源电压为5 V。由于信号 PWM为0~VDD(低电平为 0 V,高电平为 5 V)的脉冲宽度调制信号,为了对主开关MD1的驱动,脉冲宽度调制信号的电平需要转换为 SW~VBOOT;为了能够把 0~VDD电平转换成低电平为SW,高电平为 VBOOT,必须使用电平移位器(图 4中 level shift1);为了能够实现死区时间的控制,还需要把 SW~VBOOT转换为 0~5 V电平,使用图 4中 level shift2。另外,功率器件LDNMOS有比较大的栅电容,因此,LDNMOS前级反相器采用反相器链进行驱动。

4 转换器功率级版图设计考虑

由于降压型DC-DC转换器的主开关MD1位于电源和输出之间,故MD1的背栅与源极相连,而不与衬底电位相连,因此,在版图设计时,该LDNMOS背栅下面需要N型埋层(NBL)作为隔离。功率晶体管的版图设计还需要考虑以下几个方面:

首先,确定功率晶体管面积,根据前面转换器负载电流对功率晶体管的需求,采用SMIC 0.35 μm DPTM BCDMOS工艺技术,其LDNMOS的导通电阻每平方毫米为16.5 mΩ(常温25℃),本文设计的功率晶体管的面积:MD1为0.5 mm2,MD2为0.5 mm2。

其次,尽可能减小功率晶体管的金属连线和封装引线所产生的寄生电阻,下面分别考虑如下:根据所选用的工艺,采用顶层加厚铝线来减小金属连线寄生电阻,同时对顶层金属精心布线来优化功率晶体管的寄生电阻;一般来讲,对于设计负载电流大于1 A以上的DC-DC转换器,PAD与封装管脚一般采用多根金丝,设计经验1根金丝(1密尔直径)能够承受约1 A电流,不同金丝直径其电阻亦不一样,特别是设计负载电流大于2 A以上的转换器,由于导通电阻很小,引线寄生电阻在式(1)、(2)中占有的分量不能忽略不计,本设计采用4根1密尔金丝作为封装引线。当前,封装引线采用铜线技术趋于成熟,而铜线的电阻率比金线电阻率小,而且还有价格优势,因此采用铜线封装越来越受欢迎。本设计采用上述设计思想,计算得到的功率管的理论值如表1所示。

最后,对主开关和同步开关需要良好的隔离,避免互相干扰;在芯片版图中,功率器件和模拟电路需要隔离环,衰减开关噪声对内部模拟电路的影响。

表1 功率开关晶体管等效电阻理论计算

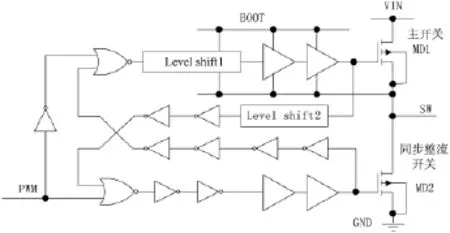

5 功率级测试结果

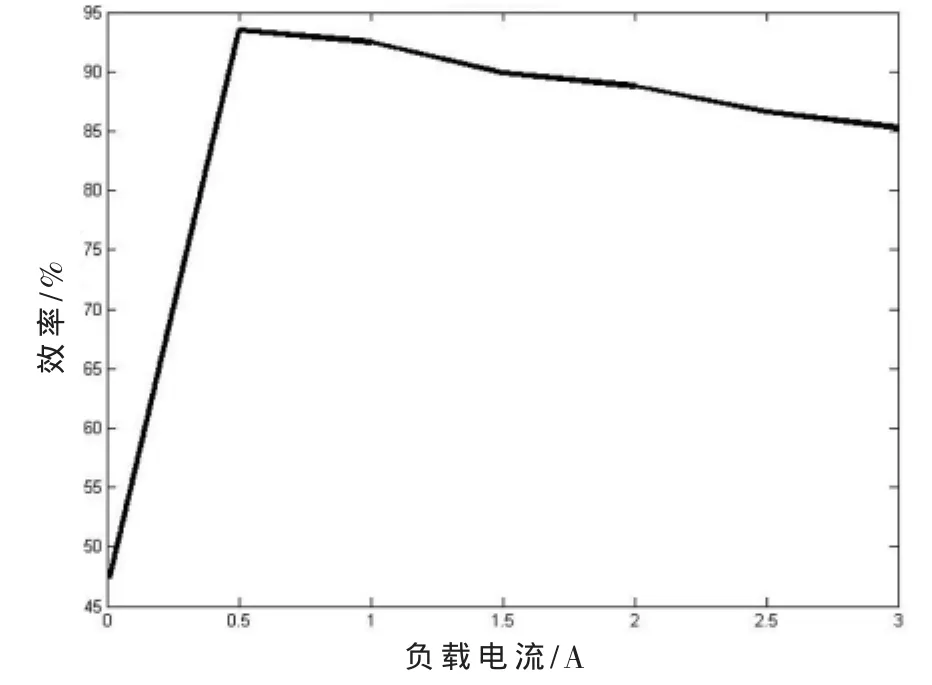

对前面所述功率级设计,应用到电流模降压型DC-DC转换器,采用SMIC 0.35 μm DPTM BCD工艺流片,芯片面积为1.6 mm×1.7 mm,电流模降压型DC-DC版图结构如图5所示。通过对芯片进行电气测试,测试条件:外接电感 4.7 μH,输出电容采用 22 μF陶瓷电容,输入电源电压为12 V,转换器开关频率为500 kHz,输出电压设置为5.0 V,输出能够提供3 A负载电流;图6给出了输出为5.0 V,在输入电源电压为12 V,不同负载条件下的效率曲线;表2给出功率级测试的结果,测试结果发现,功率开关导通电阻均大于表1的理论设计值,原因在于:表1给出的导通电阻为常温计算值,而实际测试时,由于在大电流条件下,芯片温度的上升导致导通电阻增加。

图5 电流模降压型DC-DC版图结构

图6 输出电压为5.0 V时转换器的效率曲线

6 结论

本文采用 0.35 μm DPTM 18 V BCDMOS工艺技术设计电流模降压型DC-DC转换器功率级,该功率级设计包括功率晶体管设计,并给出了功率晶体管的等效导通电阻,电流检测电路设计以及功率晶体管的驱动电路设计,最后给出了DC-DC转换器功率级的版图设计考虑。该功率级电路已经应用于DC-DC转换器中,测试结果表明:在转换器输入电压为 12 V、输出5.0 V时,输出电流为3 A;其转换效率最大可以达到94.5%。

Design of a 12V,3A current mode synchronous buck DC-DC converter power stage

Zheng Hao,Liu Yan,Wang Daoping,Yao Peng

(The Second Artillery Engineering University,Xi′an 710025,China)

A power stage design of the current mode buck DC-DC converter in 0.35 μm 18 V DPTM BCD process is proposed in this paper,the power stage can supply 3 A load current,and has a peak power efficiency of94.5%.The paper proposes the power stage design that is most important block in the buck converter,including design synchronous switch power transistors, on-chip inductor current sensor,synchronous driver circuits of the power transistors,and the layout considers of the power stage in the converter.The results of the work are also presented.

current mode;synchronous buck DC-DC converter;power stage;BCD

TN433

:A

:0258-7998(2015)03-0048-03

10.16157/j.issn.0258-7998.2015.03.011