基于RapidIO控制符产生单元设计与实现

2015-02-20冯龙辉张兴明杨镇西李沛杰

冯龙辉,张兴明,杨镇西,李沛杰,汪 欣

(1.国家数字交换系统工程技术研究中心,河南 郑州 450002;2.珠海高凌有限公司,河南 郑州 450002)

基于RapidIO控制符产生单元设计与实现

冯龙辉1,张兴明1,杨镇西1,李沛杰1,汪 欣2

(1.国家数字交换系统工程技术研究中心,河南 郑州 450002;2.珠海高凌有限公司,河南 郑州 450002)

针对RapidIO_2.2协议进行开发,设计并实现了该协议的控制符产生单元。本设计将控制符根据不同的功能字段拆分,采用流水线设计的方法将各个字段内部分别流水产生,最终并行实现。仿真结果表明,本设计在RapidIO_2.2规范下,可以实现正确快速产生控制符的功能,并且能够连续产生不同的控制符。

RapidIO;控制符;流水线;并行

0 引言

RapidIO是一种高性能、低引脚数、基于包交换的互连架构,是为满足未来高性能嵌入式系统需求而设计的一种开放式互连技术标准,同时也是国际标准组织(ISO)唯一授权的嵌入式互连技术标准。RapidIO互连接口延时小、吞吐量高,在电子对抗、声纳以及雷达等军用设备中应用广泛[1]。控制符作为协议的重要组成部分,主要用于链路维护,包定界,错误报告以及错误恢复等,是进行正常通信必不可少的信息单元,在RapidIO端点设备和交换设备中均发挥不可替代作用,占据重要的地位[2]。本文针对RapidIO_2.2规范,提出一种快速正确产生控制符的设计实现方法[3]。仿真结果表明,在满足控制条件的情况下,下一周期即可产生正确的控制符,达到了设计的预期目的。

1 控制符格式的介绍

控制符分为长控制符和短控制符,长短控制符的格式分别如图 1所示,其中(a)为短控制符格式,(b)为长控制符格式。控制符有两个字段,一个是stype0字段,一个是stype1字段。stype0与parameter0和 parameter1配合工作,构成信息字段,表明端口传递各种类型控制符的状态,其编码如表 1[2]所示。stype1则与 cmd配合工作,构成功能字段,用于链路维护或者传输定界的请求等,其编码如表 2[2]所示。短控制符有 24位,长控制符有 48位,长控制符与短控制符相似,其对应字段的名称、功能和编码都相同,唯一不同的是某些字段的位宽不同,这里不再赘述。

图1 控制符格式

2 控制符产生的设计

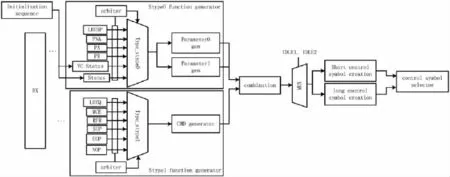

综上可知,控制符主要由三个部分构成,分别为stype0、stype1和 CRC,其中 CRC为链路检错机制[2],这里不予讨论,stype0和 stype1分别为控制符的两个域。parameter0和 parameter1配合 stype0一起工作,根据stype0的功能产生对应的字段,用于指示链路的各种状态信息;cmd则配合stype1一起工作,根据stype1的功能产生对应的cmd字段,用于链路各种控制功能。基于此,本设计将 stype0和 stype1两个域拆分为 stype0 function generator和stype1 function generator,两个域分别设计分别产生对应的控制符。对于 stype0 function generator来说,首先根据链路控制信号产生 stype0的类型,然后根据 stype0的类型选择并产生对应的 parameter0字段和parameter1字段[4],stype1 function generator工作机制与此相同。值得说明的是:status控制符是 stype0默认的也是常用的控制符,同时也是链路初始化时使用的控制符;NOP则是 stype1默认的控制符[2]。控制符是由stype0和stype1的任意组合共同构成,例如,当stype0要发送一个包接收控制符PA,stype1不需要产生特定的控制符时,则产生 NOP,由 PA和NOP共同构成控制符。形成的各个控制信号在一定的控制条件下产生对应的字段,然后根据链路 IDLE的使用情况产生长控制符或短控制符[5],最后通过控制符选择模块发送出去。本设计结构框图如图 2所示[6],下面对框图中每个模块的作用进行阐述。

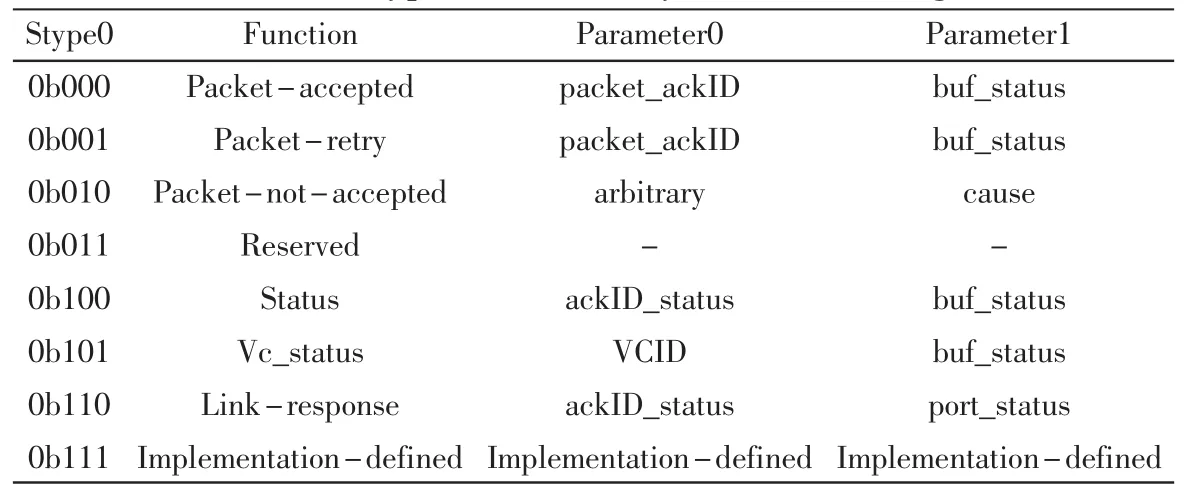

表1 Stype0 Control Symbol Encoding

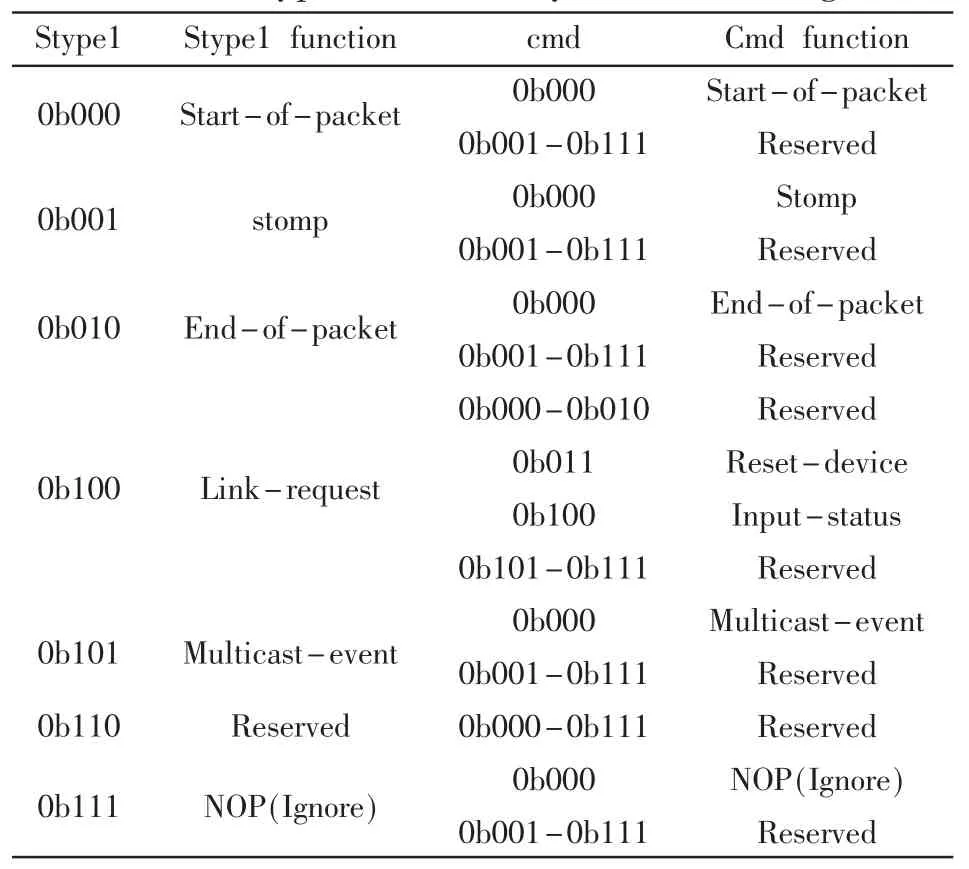

表2 Stype1 Control Symbol Encoding

图2 控制符产生设计框图

(1)Initialization sequence:初始化序列模块用于初始化序列及初始化链路。当端口完成初始化以后要对链路进行初始化,当端口收到连续的指定数量无错误的状态控制符以后,则表明链路初始化已经完成。

(2)Stype0 function generator:此模块用于产生 stype0的状态信息并且根据状态信息产生对应的parameter0字段和parameter1字段。若控制信号无效,即不需要产生特定的控制符时,status即为默认的stype0控制符。

(3)Stype1 function generator:Stype1是功能字段,此模块用于产生 stype1功能字段并且根据功能字段产生对应的cmd字段。若控制信号无效,即不需要产生特定的控制符时,NOP为默认的stype1控制符。

(4)Short control symbol creation:在 IDLE1(短空闲序列)置位的情况下,根据控制信号产生对应的短控制符。

(5)Long control symbol creation:在 IDLE2(长空闲序列)置位的情况下,根据控制信号产生对应的长控制符。

(6)Control symbol selector:根据链路上IDLE1和IDLE2的使用情况,选择合适的控制符。长短控制符在链路上的使用情况是依据 IDLE(空闲序列)的使用情况而定的。当链路使用IDLE1时,此时传输控制符为短控制符,当链路使用IDLE2时,传输控制符为长控制符。而IDLE的使用情况主要依据链路速率而定,当链路小于5.5 GB并且收发两端不使用自适应均衡(Adaptive Equalization,AE)的情况下,链路使用IDLE1;而链路速率大于 5.5 GB并且收发两端具有 AE功能的情况下链路使用 IDLE2[2]。若链路双方都支持 IDLE2且链路速率小于 5.5 GB时,也可通过链路协商进而使用IDLE2。

综上所述,本设计采用流水线设计的思想将控制符根据其不同功能、不同字段进行拆分,拆分后根据控制条件分别设计产生对应字段,最后将设计的结果拼接、选择进而发送,可以达到快速正确产生控制符的目的,并且可以连续地产生不同的控制符。

3 仿真测试

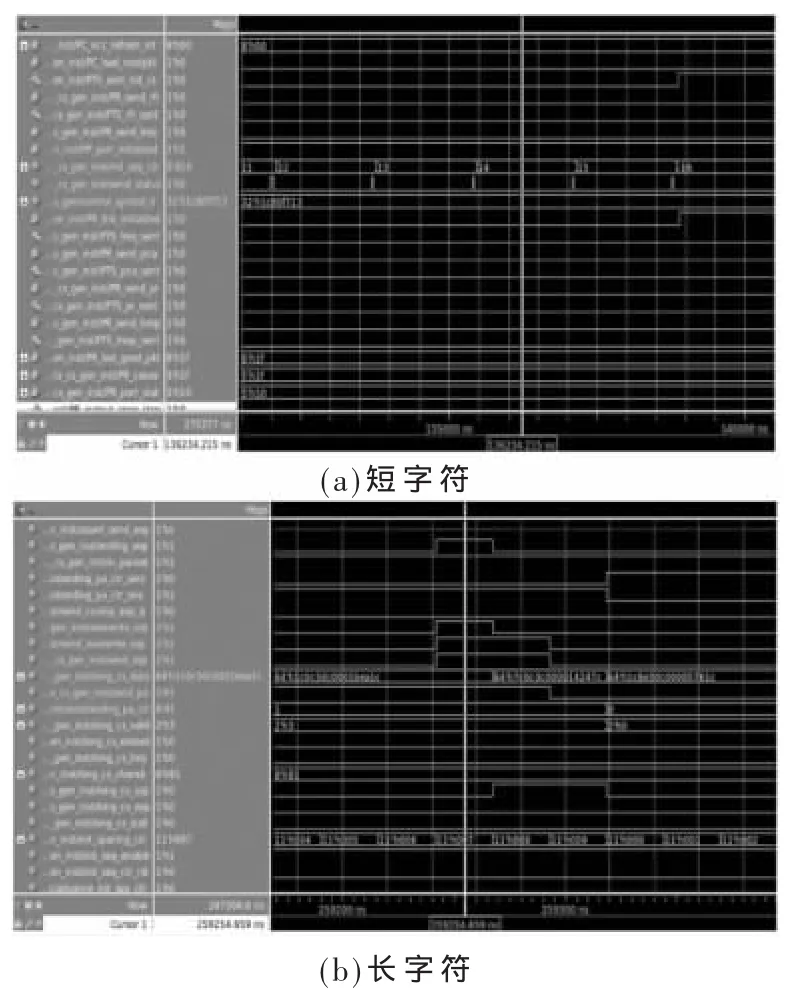

将本文中控制符产生的设计进行仿真测试,仿真结果如图3所示。其中图3(a)所示为短控制符的产生。协议规定当端口初始化完成以后,在VC=0的情况下,要连续发送16个status控制符以使链路初始化;若VC=1,则要连续发送15个 status控制符和1个vcstatus控制符来完成链路初始化[2]。本次仿真以VC=0为例,从图中信号可以看出,在端口初始化完成以后,连续发送了16个status控制符,从而使得链路初始化完成。

图3 控制符设计仿真图

图3 (b)为产生长控制符仿真测试图。stype0产生的是 PA,stype1产生的是 sop。产生 PA的情况有多种,有一个计数器 outstanding_pa_ctr专门计数未能及时处理发送的PA的数目,当链路初始化完成以后,只要 outstanding_pa_ctr的值不为零则发送 PA控制符;或者当PA的数目太多超过一定值之后,亦或buf的状态已经过期,都要产生PA控制符,本仿真图以第一种情况为例。对于 sop的产生也有多种情况,若 sop信号有效,同时配置模块允许其 advance,此时会产生 sop控制符;若上个周期 eop有效,但是下个周期即将到来 sop,此时要把 eop重写为sop,产生 sop控制符。本文以第二种情况为例。本设计短控制符为32位,其中头部包含8位的包定界符;长控制符为64位,其中头部和尾部各自包含一个包定界符。

4 结论

本文针对 RapidIO_2.2协议进行开发,设计并且实现了控制符的产生。根据控制符的特点,对其不同的功能字段进行拆分,采用流水线的设计思想,流水产生各个字段最后拼接发送。仿真结果表明,本设计可以快速正确地产生对应功能的长短控制符,满足预期目标,为器件的正常通信提供了有力的保障。

[1]陈程.串行RapidIO总线在存储系统中的应用研究[D].西安:西安电子科技大学,2013.

[2]ASSOCIATION R T.RapidIOTM Interconnect Specification Part 6:LP-Serial Physical Layer Specification[D].2011.

[3]杨卿.RapidIO高速互联接口的设计研究与应用[D].成都:电子科技大学,2009.

[4]陈宏铭,李蕾,姚益武,等.基于 AXI总线串行 RapidIO端点控制器的 FPGA实现[J].北京大学学报,2014,50(4).

[5]吴峰锋.一种低时延的串行 RapidIO端点设计方案[J].北京大学学报(自然科学版),2013,49(4).

[6]张强.串行RapidIO互连系统的设计与实现[D].南京:南京理工大学,2013.

Design and realization of the control symbols module based on RapidIO specification

Feng Longhui1,Zhang Xingming1,Yang Zhenxi1,Li Peijie1,Wang Xin2

(National Digital Switching System Engineering Technological Research Center,Zhengzhou 450002,China)

This paper designs and realizes the control symbols module based on the RapidIO_2.2 specification.Using the method of pipeline,the control symbol is decomposed and created according to the functions of different fields,which can be combined parallelly in the end.The simulation results show that under the RapidIO_2.2 specification our design can create the right control symbols rapidly,and can also create different control symbols continuously.

RapidIO;control symbols;pipeline;parallel

TN911

A

10.16157/j.issn.0258-7998.2015.11.013

冯龙辉,张兴明,杨镇西,等.基于 RapidIO控制符产生单元设计与实现[J].电子技术应用,2015,41 (11):48-50.

英文引用格式:Feng Longhui,Zhang Xingming,Yang Zhenxi,et al.Design and realization of the control symbols module based on RapidIO specification[J].Application of Electronic Technique,2015,41(11):48-50.

2015-05-01)

冯龙辉(1988-),通信作者,男,硕士研究生,主要研究方向:高速串行 RapidIO,E-mail:flhcherish@163.com。

张兴明(1963-),男,硕士生导师,教授,主要研究方向:SOC片上网络体系结构,高性能计算。

杨镇西(1971-),男,硕士,副研究员,主要研究方向:系统级芯片设计。