低温锗量子点缓冲层技术生长硅锗弛豫衬底研究

2015-02-06周志文叶剑锋李世国

周志文,叶剑锋,李世国

(深圳信息职业技术学院 电子与通信学院,广东 深圳 518172)

低温锗量子点缓冲层技术生长硅锗弛豫衬底研究

周志文,叶剑锋,李世国

(深圳信息职业技术学院 电子与通信学院,广东 深圳 518172)

为了提高生长在硅衬底上的硅锗弛豫衬底的质量,提出了低温锗量子点缓冲层技术,分析了该技术在应变弛豫的促进,表面形貌的改善,位错密度的降低等方面的作用机理。基于低温锗量子点缓冲层技术,利用超高真空化学气相淀积系统,在硅衬底上生长出高质量的硅锗弛豫衬底。锗组份为0.28,厚度不足380 nm的硅锗弛豫衬底,应变弛豫度达到99%,表面没有Cross-hatch形貌,表面粗糙度小于2 nm,位错密度低于105 cm-2。

硅锗弛豫衬底;低温锗量子点缓冲层;生长

硅锗(SiGe)材料具有优越的光、电、热等性能,并且与成熟的硅(Si)微电子工艺兼容,使得它们在硅基器件如发光器件、光电探测器、光电调制器、晶体管等中得到研究和应用[1,2]。高性能器件的研制离不开高质量材料的生长。高质量SiGe弛豫衬底的性能参数为:高的应变弛豫度、小的表面粗糙度、低的位错密度、薄的缓冲层厚度,等等。SiGe和Si之间存在热失配和晶格失配,在Si衬底上直接生长SiGe弛豫衬底,通常会使得表面粗糙度过大,位错密度过高。为此,多种缓冲层技术被提出,包括:组份变化缓冲层[3,4]、插入Si[5]和SiGe/ SiGeC超晶格[6]、低温Si[7]和低温SiGe[8]以及离子注入[9]等。这些技术在SiGe弛豫衬底的某些性能方面取得了优异的结果,但也存在不足之处:(1)SiGe弛豫衬底的应变弛豫度不高[10]。其原因是应变弛豫的主要机制是失配位错,其产生和运动受到热动力学的限制。通常,采用高温退火或者增加厚度的方法来提高应变弛豫度,这样额外增加了工艺集成的难度。(2)SiGe弛豫衬底的表面出现Cross-hatch形貌[11,12]。Cross-hatch形貌不仅使表面粗糙度增加,而且使应力场呈周期性分布,不利于后续材料生长和器件制作[13]。

为了提高应变弛豫度,改善表面Cross-hatch形貌,提高生长在Si衬底上的SiGe弛豫衬底的质量,提出了低温锗量子点缓冲层技术,从理论上分析并从实验上证实了该技术在生长SiGe弛豫衬底的优越性。

1 低温锗量子点缓冲层技术

图1为低温Ge量子点缓冲层技术的生长结构示意图。在体Si衬底上,先以较低温度(300oC左右)生长低温Ge量子点缓冲层,再升高温度(500oC左右)生长SiGe弛豫衬底。下面将分别分析该技术在应变弛豫的促进,表面形貌的改善,位错密度的降低等方面的作用机理。

图1 生长结构示意图Fig.1 Schematic cross section of LT-Ge islands buffer

在SiGe合金中,晶格失配度最大的是Ge和Si,达到4.2%,共度生长在Si衬底上的Ge,临界厚度只有几纳米,使得SiGe/Si之间的失配应变较容易通过产生表面起伏(形成量子点)和(或)形成失配位错来弛豫(释放),不再需要增加弛豫衬底的厚度或者高温退火来处理。

研究表明,Cross-hatch形貌是由周期性失配位错的产生导致的原子错位,以及非均匀应变分布导致的生长速率局部增强所引起的,与应变弛豫的Freak-Read源位错的增殖、运动相关联[11,12]。Ge量子点的产生释放了部分失配应变,而分布的随机性打破了失配位错成核的周期性,从而改善了表面Cross-hatch形貌和应变分布。同时,在较低温度下生长的Ge量子点,其尺寸较小,容易被后续生长的SiGe弛豫衬底所掩埋,使生长表面逐渐变平整,从而降低表面粗糙度。

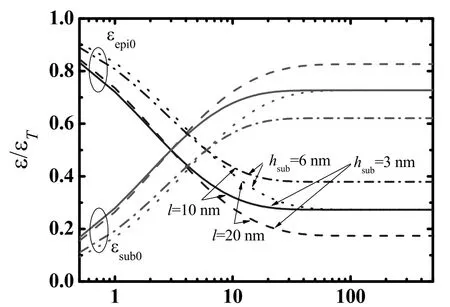

失配应变的大小和分布决定着位错的产生和运动。SiGe弛豫衬底和低温Ge量子点缓冲层的应变分量分别表示为[14]:

根据公式1计算了SiGe弛豫衬底和Ge量子点的应变分量与SiGe弛豫衬底厚度的关系。由于SiGe/ Si材料的杨氏模量、泊松比的值几乎相同,假设K=1。Ge量子点的厚度hsub为3nm或6nm,直径2l为20nm或40nm,计算结果如图2所示。当SiGe弛豫衬底的厚度远小于Ge量子点缓冲层的厚度时,失配应变主要分布在SiGe弛豫衬底内,使位错向弛豫衬底内移动,增加了弛豫衬底的位错密度;当SiGe弛豫衬底的厚度远大于缓冲层的厚度时,失配应变主要分布在缓冲层内,使位错向缓冲层内移动,降低了弛豫衬底的位错密度。低温Ge量子点缓冲层可以调节应变,将位错限制在缓冲层内,极大地降低了弛豫衬底中的位错密度。

图2 应变分布图2 Strain distribution

以上理论分析表明,低温Ge量子点缓冲层在促进应变释放的同时改善了表面形貌,而其应变调节作用又降低了位错密度。

2 实验

SiGe/Si弛豫衬底的生长设备是超高真空化学气相沉积系统,该系统装配有反射高能电子衍射仪(RHEED),可以原位监控生长过程,高纯乙硅烷和锗烷为生长气源[15]。生长过程简述如下:

图3 生长结构和参数Fig.3 Growth structure and parameters

四英寸,电阻率为0.1~1 Ω·cm的N型Si(100)衬底,经过标准RCA清洗后传入生长室。生长室内衬底温度在900℃保持30 min,以去除水汽、氧杂质等。随后设定合时的温度,通入气源,开始生长。图3为生长结构和参数。首先在750℃生长Si缓冲层,厚度为300nm;然后降低温度到~300℃生长Ge量子点,厚度小于5nm;最后缓慢升高温度到~500℃生长SiGe,厚度为350nm。为了抑制升温过程中Ge量子点的起伏,在低温300℃和高温500℃之间的中温400℃,增加生长了一层30nm厚的SiGe[16]。

采用英国Bede公司的高精度X射线衍射仪(HRXRD,X射线源为Cu κα1,波长λ=0.15406nm)和英国Renishaw公司的拉曼光谱仪(UV-1000x,Ar+激光器,波长λ=514.5 nm)检测样品的组份、应变弛豫度和晶体质量;采用日本SⅡNano Technology公司的原子力显微镜(AFM,SPI4000-SPA400,轻敲模式)和光学显微镜分析样品的表面形貌;采用化学腐蚀位错坑[17]的方法分析位错的分布和密度,腐蚀溶液为Secco溶液,SiGe弛豫衬底被腐蚀掉的厚度为~80 nm。

3 结果和讨论

3.1 表面形貌

图4为SiGe弛豫衬底生长过程中的原位RHEED衍射花斑。生长完Si缓冲层后,出现清晰明亮的2×1条纹,见图(a),说明表面十分平整;生长完低温Ge缓冲层后,点状出现,并且条纹变模糊,见图(b),表明有Ge量子点的形成。生长完中温SiGe后,点状变模糊,条纹变清晰,见图(c),说明生长的SiGe覆盖了Ge量子点;生长完高温SiGe后,与Si缓冲层的相似,条纹恢复清晰明亮,点状消失,见图(d),表明表面的平整性好。

图4 原位RHEED图案Fig.4 In-situ RHEED patterns

表面形貌AFM测试的结果如图5所示。图(a)和(b)分别为低温Ge量子点和SiGe弛豫衬底的表面形貌。图(a)中,观察到密集的、小型的量子点,量子点的直径为20-50nm,高度为2-6nm,密度为~7×1010cm-2。图(b)中,SiGe弛豫衬底的表面无Cross-hatch形貌,表面十分平整,粗糙度约为1.9nm。AFM测试结果与RHEED监测结果相一致。Ge量子点的形成改善了表面的Cross-hatch形貌,而SiGe的生长又将Ge量子点掩埋。

图5 表面形貌AFM图Fig.5 AFM images

3.2 应变弛豫

图6为SiGe弛豫衬底的HRXRD摇摆曲线,包括两条曲线:(004)对称面的和(224)非对称面的。每条曲线有两个衍射峰,其中,Si衬底的衍射峰较窄,SiGe弛豫衬底的衍射峰较宽。HRXRD没有检测到Ge量子点的衍射信号。SiGe弛豫衬底(004)面和(224)面的衍射峰具有较好的对称性,说明应变被均匀地弛豫。根据(004)面和(224)面的峰位,计算SiGe弛豫衬底的Ge组份为0.28,弛豫度为99%。

图6 HRXRD摇摆曲线Fig.6 HRXRD rocking curves

由于HRXRD没有检测到Ge量子点缓冲层的衍射信号,又进行了拉曼散射实验,结果如图7所示。图(a)和(b)分别为低温Ge量子点和SiGe弛豫衬底的散射谱。图(a)的散射峰仅有来自Si衬底的Si-Si模和来自Ge量子点的Ge-Ge模。图(b)的散射峰比较多,从高波数到低波数,峰位及其来源依次为:

520.6 cm-1 Si衬底的Si-Si模

500 cm-1左右 SiGe弛豫衬底的Si-Si模

435 cm-1左右 局域化的Si-Si模

400 cm-1左右 SiGe弛豫衬底的Si-Ge模

306 cm-1低温 Ge量子点的Ge-Ge模

290 cm-1左右 SiGe弛豫衬底的Ge-Ge模

根据SiGe弛豫衬底的Si-Si模和Si-Ge模,计算得到SiGe弛豫衬底中Ge的组份为0.26,应变弛豫度为~100%。在实验误差范围内,拉曼散射实验与HRXRD实验结果近乎完全吻合,均证实SiGe弛豫衬底具有高的弛豫度。Si0.72Ge0.28弛豫衬底的厚度仅有380 nm,弛豫度却达到100%,说明低温Ge量子点缓冲层极其利于SiGe/Si之间应变的弛豫。

图7 拉曼散射光谱Fig.7 Raman spectra

Ge和Si之间最大的晶格失配度,为应变弛豫提供了便利的条件:起伏表面和(或)产生位错,使得在仅生长Ge量子点时,应变弛豫度就很高。图(a)中, Ge量子点Ge-Ge模的峰位为304 cm-1,接近体Ge的300.2 cm-1。根据峰位计算Ge量子点的应变弛豫度为77%。在应变弛豫了的Ge量子点上后续生长SiGe,极易弛豫SiGe的压应变。由于体Ge的晶格常数比SiGe的大,SiGe甚至可能受到张应变。实际测量结果是SiGe完全无应变。主要原因是Ge量子点具有应变调制作用,为了与SiGe的晶格相匹配,弛豫了的Ge晶格又被压缩了,导致Ge的压应变增加。图(a)中,Ge量子点Ge-Ge模的峰位为304 cm-1,而图(b)中的为306 cm-1。由于压应变的增加,Ge-Ge模的峰位移动了2 cm-1。生长SiGe弛豫衬底后,Ge量子点的压应变从0.95%增加到1.45%。另外,图(a)中Ge量子点Ge-Ge模的峰值半高宽为17cm-1,比图(b)中的7 cm-1大,说明低温Ge缓冲层中的缺陷较多,结晶质量较差。

晶格调制过程如图8所示。体SiGe的晶格常数随着Ge组份的增加而增大,见图(a),在Si衬底上生长低温Ge量子点缓冲层,由于大的失配应变,Ge的晶格很快完全弛豫,几乎达到体Ge,见图(b)。但是,在其上后续生长SiGe,Ge的晶格又被压缩,几乎与体SiGe的相同,见图(c)。应变大小的改变,以及外延层厚度的增加,Ge的晶格随之相应地被调制。这是因为Ge量子点较薄,分布着大部份的失配应变(见图2的计算结果),并且Ge量子点是在低温下生长的,结晶质量变差,机械强度减弱(见图7的测试结果),具有被调制的可能。

图8 晶格结构变化示意图Fig.8 Schematic of lattice structure

3.3 位错

图9为化学腐蚀后SiGe弛豫衬底的表面形貌光学显微镜图。图9中穿透位错露头较少,位错密度少于105 cm-2。位错密度低的原因有两点:一是应变在生长Ge量子点时已经释放,生长SiGe弛豫衬底时不再需要产生新的失配位错;二是Ge量子点能够调节应变(见图8),大部份位错被限制在低温Ge缓冲层和Si衬底的界面,SiGe弛豫衬底的位错被减少。

图9 表面光学显微镜图Fig.9 Optical view of SiGe surface

3.4 比较

将我们的实验结果与文献报道的列于表1。综合比较,我们的Si0.72Ge0.28弛豫衬底,厚度薄,弛豫度高,表面平整,位错密度低,表明低温Ge量子点缓冲层技术在生长SiGe弛豫衬底中具有明显的优势。

表1 SiGe弛豫衬底的性能比较Tab.1 Properties of SiGe virtual substrates grown by various methods

4 结论

为了提高生长在硅衬底上的硅锗弛豫衬底的晶体质量,提出了低温Ge量子点缓冲层技术,从实验上验证了该技术的优越性:提高应变弛豫度,改善表面Cross-hatch形貌,降低位错密度。厚度仅为380nm的Si0.72Ge0.28弛豫衬底,应变弛豫度达到99%,表面无Cross-hatch形貌,表面粗糙度小于2nm,位错密度低于105cm-2。

[1][王兴军,苏昭棠,周治平.硅基光电子学的最新进展[J].中国科学:物理学 力学 天文学,2015,45(1):014201-1-31.]Wang X,Su Z,Zhou Z.Recent progress of silicon photonics [J].SCIENTIA SINICA Physica,Mechanica &Astronomica,2015,45(1):014201-1-31.(in Chinese)

[2]Fu Q,Zhang,Jin D,et al.Collector optimization for improving the product of the breakdown voltage-cutoff frequency in SiGe HBT [J].Journal of Semiconductors,2015,36(4):044005-1-4.

[3]Bogumilowicz Y,Hartmann J,Laugier F,et al.High germanium content SiGe virtual substrates grown at high temperatures [J].J.Cryst.Growth,2005,283(3-4):346-355.

[4]Liu J,Wong L,Sohn D,et al.A Novel Thin Buffer Concept for Epitaxial Growth of Relaxed SiGe Layers with Low Threading Dislocation Density [J].Electrochem.Solid-State Lett.,2005,8(2):G60-G62.

[5]Chen P,Lee L,Lee M,et al.Growth of high-quality relaxed SiGe films with an intermediate Si layer for strained Si n-MOSFETs [J].Semicond.Sci.Technol.2006,21(4):479-482.

[6]Wong L,Liu J,Ferraris C et al,Low-dislocation-density strain relaxation of SiGe on a SiGe/SiGeC buffer layer [J].Appl.Phys.Lett.,2006,88(4):041915-1-3.

[7]Li J,Peng C,Wu Y,et al.Relaxed Si0.7Ge0.3 layers grown on low-temperature Si buffers with low threading dislocation density [J].Appl.Phys.Lett.,1997,71(21):3132-3134.

[8]Peng C,Zhao Z,Chen H,et al.Relaxed Si0.1Ge0.9 alloy layers with low threading dislocation densities grown on low-temperature Si buffers [J].Appl.Phys.Lett.,1998,72(34):3160-3162.

[9]Sawano K,Koh S,Shiraki Y,et al.Fabrication of highquality strain-relaxed thin SiGe layers on ion-implanted Si substrates [J].Appl.Phys.Lett.,2004,85(13):2514-2516.

[10]Bolkhovityanov Y,Pchelyakov O,Sokolov L,et al.Artificial GeSi substrates for heteroepitaxy:Achievements and problems [J].Semiconductors,2003,37(5):493-518.

[11]Hsu J,Fitzgerald E,Xie Y,et al.Surface morphology of related GexSi1-x films [J].Appl.Phys.Lett.,1992,61(11):1293-1295.

[12]Chen H,Li Y,Peng C,et al.Crosshatching on a SiGe film grown on a Si(001) substrate studied by Raman mapping and atomic force microscopy [J].Phys.Rev.B,2002,65(23):233303-1-4.

[13]Sawano K,Koh S,Shiraki Y,et al.In-plane strain fluctuation in strained-Si/SiGe heterostructures [J].Appl.Phys.Lett.,2003,83(13):4339-4341.

[14]Zubia D,Hersee S.Nanoheteroepitaxy:The Application of nanostructuring and substrate compliance to the heteroepitaxy of mismatched semiconductor materials [J].J.Appl.Phys.,1999,85(9):6492-6496.

[15]周志文,叶剑锋.UHV/CVD生长SiGe/Si材料分析及应用研究[J].深圳信息职业技术学院学报,2011,11:29-32.]Zhou Z,Ye J.Growth of SiGe/Si Heterostructures by UHV/CVD[J].J.Shenzhen Institute of Information Technology,2011,11:29-32.(in Chinese)

[16]Sakai A,Sugimoto K,Yamamoto T,et al.Reduction of threading dislocation density in SiGe layers on Si(001) using a two-step strain-relaxation procedure [J].Appl.Phys.Lett.,2001,79(21):3398-3400.

[17]D'Aragona F.Secco.Dislocation Etch for(100) Planes in Silicon [J].J.Electrochem.Soc.,1972,119(7):948-951.

Growth of SiGe virtual substrate on Si(100) by low temperature Ge islands buffer

ZHOU Zhiwen,YE Jianfeng,LI Shiguo

(School of Electronic Communication Technology,Shenzhen Institute of Information Technology,Guangdong Shenzhen 518172,P.R.China)

A method for the growth of strain-relaxed SiGe virtual substrate(VS) on Si substrate with low temperature Ge(LT-Ge) islands buffer was proposed and studied.The role of LT-Ge islands buffer played in the mechanism of strain adjustment,surface modification and dislocation annihilation was analyzed.High-quality strain-relaxed SiGe VS was grown on Si(100) substrate in an ultra-high vacuum chemical vapor deposition system by LT-Ge islands buffer.Si0.72Ge0.28 VS with a thickness of only 380 nm had a strain relaxation degree of 99%.No cross-hatch pattern was observed on the SiGe VS surface and the surface root-mean-square roughness was less than 2 nm.The threading dislocation density was lower than 105 cm-2.

SiGe virtual substrate;low temperature Ge islands buffer;growth

TM23

A

1672-6332(2015)03-0005-06

【责任编辑:高潮】

2015-09-28

深圳市科技计划项目(No.JCYJ20120821162230170);广东省高等学校优秀青年教师项目(Yq2014123)

周志文(1982— ),男(汉),湖北汉川人,博士,副教授,研究方向为半导体材料和器件。E-mail:zhouzw@sziit.com.cn;35518062@qq.com.cn