基于FPGA的液晶显示控制器的设计与实现

2015-02-05长江大学电子信息学院盛象飞

长江大学电子信息学院 盛象飞

基于FPGA的液晶显示控制器的设计与实现

长江大学电子信息学院 盛象飞

介绍一种基于FPGA的液晶显示控制器的设计与实现。该设计采用Verilog HDL硬件描述语言,以Alter公司的Cyclone 系列的EP1C6Q240C8芯片为载体,实现了对1602字符型液晶显示器的控制。该方法可靠性高,移植性好,便于调试与升级。文章给出了FPGA对1602字符型液晶显示器的测试结果,表明了该设计的可实现性和可靠性。

FPGA;1602字符型液晶显示器;Verilog HDL;Cyclone EP1C6Q240C8

引言

在小型智能化电子产品中,普通的7段LED数码管只能用来显示数字。若遇到要显示英文字母、图像或汉字时,则必须选择使用液晶显示器(简称LCD)。LCD显示器的应用很广,如复印机和传真机,以及一些娱乐器材、医疗仪器上,常常可看见LCD的足迹[1]。随着人机界面(GUI)在医疗、工业以及消费电子各应用领域需求的日益增长,高集成度、高性能的TFT液晶显示方案成为电子产品设计开发的重要组成部分[2]。为此本文提出了一种基于FPGA对字符型液晶显示器的控制方案。该方案不仅操作简单方便,而且占用资源少。

1 总体结构

本设计中的液晶显示控制器以EP1C6Q240C8芯片作为控制芯片,用Verilog HDL硬件描述语言编程,通过JTAG下载器下载,并利用Quartus II软件进行调试,实现了FPGA对1602字符型液晶显示模块的控制。

图1为总体结构。本设计是基于FPGA的LCD显示模块的控制。LCD显示模块接收来自于FPGA的控制信号和数据,FPGA同时读取LCD显示模块中的相关信息,这样才能实现对LCD显示模块的控制。FPGA的最小系统包括电源、复位、时钟、SDRAM、JTAG。FPGA一般先通过PC机使用JTAG下载器把程序烧写到FPGA芯片上,不过这种方式在断电以后程序会丢失,但是充分利用了FPGA的无限擦写性。而通过AS(Active Serial Programming)模式下载,这样便不会断电丢失。所不同的是用AS模式下载时,需先编程配置芯片(如EPCS1),然后再配置FPGA,这种模式适合于待产品开发成熟时选用[3]。

2 系统设计及实现

2.1 FPGA选型

FPGA(Field—Programmable Gate Array),即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、通用阵列逻辑GAL(Generic Array Logic)、复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)等可编程器件的基础上进一步发展的产物。

本设计采用的是Altera公司的Cyclone低成本系列FPGA——EP1C6Q240C8,其工作电压为3.3V,内核电压1.5V,内部有2个锁相环,20个内嵌乘法器,5980个逻辑单元(LEs),185个用户I/O口,8个全局时钟,资源丰富,可很好地满足设计需要。

2.2 LCD显示模块

以深圳市创显达电子有限公司的5V 1602字符型液晶显示器作为本设计中的LCD显示模块。1602 LCD显示模块是指可以显示两行,每行16个字符的液晶显示模块。模块内置有显示数据的DDRAM、字符发生存储器CGROM和CGRAM。CGROM已经存储了160个不同的点阵字符图,每一个字符都有一个固定的代码。只需要向DDRAM输入相应字符的地址,就能从CGROM中读取数据,液晶屏就会输出显示相应的字符[4]。

2.3 软件设计

本设计是PC机通过JTAG下载器向FPGA发送指令来控制LCD显示模块。该设计的软件部分采用Verilog HDL硬件描述语言。与之前较为熟悉的C语言相比,该语言的最大优点是:它是一种非常容易掌握的硬件描述语言,语法与C语言类似。用Verilog HDL建模的最大优点就是与工艺没有关系,便于设计人员的修改设计,极大地提高了设计效率。

1602字符型液晶显示器是低频显示器件。一般51单片机控制该显示器没有问题,因为单片机的时钟频率较低。该板卡用的晶振是50MHz,假如用它控制1602字符型液晶显示器的话,那晶振频率过高,由于液晶显示器控制时序由于需要较长的建立时间,假如不进行分频的话,显示器则不能正常显示。该软件设计把FPGA系统50MHz分频为500Hz作为LCD显示模块的控制时钟。

本软件设计主要分为两大模块:时钟分频模块CLK50M_500、显示驱动模块LCD_show。其中时钟分频模块CLK50M_500解决了FPGA驱动LCD显示模块的时钟频率匹配问题。显示驱动模块LCD_show解决的是LCD显示模块第一行、第二行字符以及汉字的显示问题,为LCD显示模块的正常显示提供了核心软件支持。

本文采用有限状态机来实现显示驱动的核心逻辑[5]。有限状态机是建立系统模型最为有效的手段,有着广泛的应用。综合工具可以非常有效地将HDL语言描述的状态机行为转换成门级电路[6]。

状态转换如图2所示。各状态分别是:空闲模式、清屏、显示开关设置、输入方式设置、功能设置、写数据模式状态。初始状态为空闲模式,开始写数据时首先对LCD清屏,然后设置LCD的显示开关以及输入方式设置,再然后进行功能设置,最后再写入数据。在写数据的同时检测数据是否已写完,若未写完继续写数据,若数据已写完则进入显示开关设置状态,等待下一轮的数据读写。

图2 状态转换图

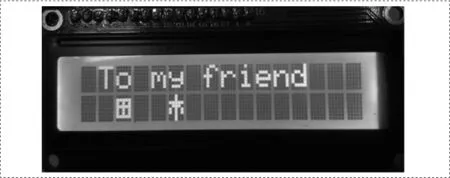

3 验证及分析

在该实验板上功能和时序验证成功之后,需要把编程之后的文件通过专用JTAG下载器烧写至FPGA板卡。本设计在该实验板上输出了“To my friend 田木”其中第一行是“To my friend”,第二行是“田木”,包括了英文字母和中文,达到了预期理论目标。实际效果如图3所示。

通过修改该Verilog程序可以改变LCD显示模块的显示效果,效果如图4所示。

当然,还可以做些其他效果变化,例如光标闪烁、文字更改、左移或者右移等等变化。如有兴趣的可以自己做下,在此就不一一做演示。

图3 显示效果

图4 显示效果

4 结束语

本文利用Cyclone系列FPGA器件,实现液晶控制功能模块的设计。采用Verilog HDL语言,运用FPGA技术,经过一系列的模块设计,从行为级和RTL级上进行综合描述,并经过Quartus II的编译、综合、验证、下载等过程,实现了核心设计方案的所有功能,最终在一片FPGA芯片上完成了对1602字符型液晶显示模块的控制。实际测试结果表明,本系统满足对液晶显示模块的控制要求,达到了设想的效果。该接口控制器设计简洁可靠,在一些低速和低端的液晶显示应用中具有一定的使用价值。

[1]周兴华.手把手教你学单片机C程序设计[M].北京:北京航空航天大学出版社,2008.

[2]邵青.基于STM32F4x9的LCD显示设计方案[J].单片机与嵌入式系统应用,2014,14(6):82-83.

[3]华清远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.

[4]陈立克,许存禄,辛遥,等.基于FPGA技术的液晶显示控制器设计[J].微电子学,2011,41(6):852-855.

[5]曹勇,沈斌,熊伟.SOPC中NiosII的LCD显示驱动IP设计[J].单片机与嵌入式系统应用,2010,10(6):16-18.

[6]杜慧敏,李宥谋,赵全良.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学出版社,2006.

盛象飞(1991—),男,河南驻马店人,硕士研究生,主要研究方向:fpga、单片机、硬件电路。