基于FPGA的非周期信号等效采样原理和实现

2015-02-05中煤科工集团重庆研究院有限公司张海鹏

中煤科工集团重庆研究院有限公司 张海鹏

基于FPGA的非周期信号等效采样原理和实现

中煤科工集团重庆研究院有限公司 张海鹏

分析了高精度测量仪表中信号高速ADC采样的迫切性,实际应用时信号等效采样的必要性,结合非周期信号的特点确定了顺序等效采样的方法,阐述了顺序等效采样的原理,基于FPGA内部锁相环(PLL)倍频和移相的特点,最终实现了用50MSPS的ADC达到了1.6GSPS的等效采样速率,为解决毫米级激光测距和分米级电磁波故障定位的精度问题提供了理论依据和实际措施。

非周期信号;等效采样;顺序等效采样法;随机等效采样法;FPGA

引言

随着数字信号处理技术的迅速发展,模拟信号数字化越来越靠近设备前端,波形数字化[1]一直是前端读出电子学系统设计的难点,对高速变化的模拟信号进行采样例如高精度的激光测距仪、电磁波故障定位仪、数字示波器等,都要求有超高采样率的ADC电路和数据处理电路。低速ADC无法对高频信号实时采集,高速ADC芯片价格居高不下,并且采购还受国外因素制约,必须采用等效采样技术。它以增加采集时间为代价降低采样率,通过对多次采样的数据进行重构实现周期信号或非周期信号的数字化。等效采样分顺序和随机等效采样两种方法[2]。对于周期信号可以采用随机等效采样并实现预触发,多应用于数字示波器;对于非周期信号只能采用顺序等效采样,本设计的创新在于充分利用FPGA内部锁相环倍频和移相实现了0.625ns实时时移,可编程逻辑电路控制顺序等效采样时序,结合50MSPS的ADC等效实现了1.6GSPS的采样速率。

1 发射非周期信号的特点

1.1 发射信号具有时限性[3]

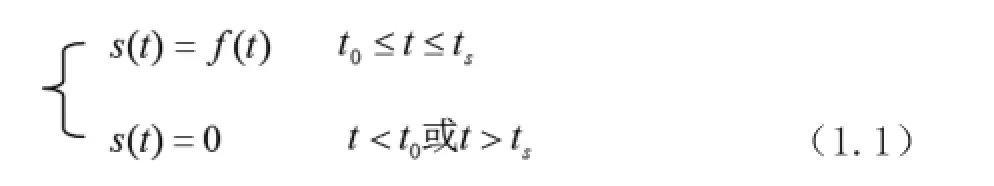

发射信号无论是单个单极性脉冲、单个双极性脉冲,还是多周期脉冲串,它都具有在某个时间区间有信号,其余时间都为0的共性,是典型的非周期信号,测量信号满足式(1.1):

1.2 发射信号系统具有线性时不变特性

首先发射信号系统具有时不变特性,当内部控制信号有一个时移时,发射信号也产生相同的时移,除此之外无任何其它变化。当式(1.1)中产生一个时移变为时,,其它为0。

1.3 发射信号具有可配置性

发射信号系统满足线性时不变特性,同时硬件系统能实现配置发射信号的极性、幅度、持续时间、多周期重复等功能,支持信号正负双极性输出、幅度k倍缩放、持续时间a倍拉

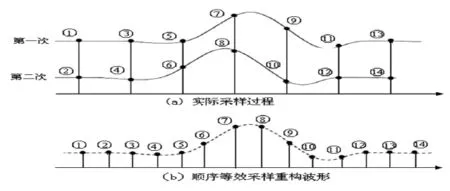

图1 两次顺序等效采样示意图

图2 发射信号电路框图

图5 FPGA上顺序等效采样电路

图6 AD采样电路

图3(a) 发射信号脉宽和极性控制电路

图3(b) 发射信号基准时钟产生电路

图3(c) 发射信号触发延时电路

采样的示意图如图1所示,更多倍数的顺序等效采样原理以此类推。在工程技术上,提供一个时间极小△t的延迟比较容易,因此顺序取样能提供很高的时间分辨率和精度,能够极大的提高系统的采样率。

2 非周期信号采样的FPGA实现

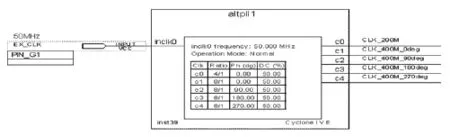

以电磁波电缆故障定位仪为例,FPGA芯片选用Altera公司Cyclone IV[4]系列EP4CE30F23I7N,用VHDL语言实现的自定义模块[5],发射信号产生电路如图3(a)、(b)、(c)所示,实现了根据测量范围TDR_SEL信号自动选择脉冲宽度和脉冲极性。

3 顺序等效采样的实现

激光脉冲测距仪和电磁波电缆故障定位仪都由片上系统(SOPC)根据测量范围配置顺序采样等效次数,控制地址自动生成器产生单次触发控制信号和触发延时控制,实现每次发射信号比上次触发提前一个△t时间,发射信号都经被测对象反射形成接收信号,接收信号经过信号调理电路调整好幅度和基线,AD采样电路在地址自动生成器的配合下,将采样数据依次存入片上双端口RAM,片上系统从双端口RAM中读出顺序等效采样数据,完成波形重构和数字信号相关技术处理,顺序等效采样电路框图如图4所示:

图4 顺序等效采样电路框图

以电磁波电缆故障定位仪为例,在FPGA上用VHDL语言实现的自定义模块,顺序等效采样电路路如图5所示,实现了自动地址生成器、单次触发控制和片上双端口RAM,根据仪表测量范围选择双端口RAM的容量,在本例中等效采样最高速率1.6GSPS,双端口RAM每个AD采样值对应距离分辨率为:

保证这个分辨率测量800m的范围,就要选择至少8Kbytes的双端口RAM容量。

外部硬件AD采样电路如图6所示,采用ADI公司的AD9283BRSZ-50芯片,475MHz模拟带宽,8bit采样,1.25V内置基准,温漂系数130ppm/℃,50MSPS的实时采样速率,经过32次等效采样最高可达1.6GSPS的采样速率。

4 结语

本文针对激光脉冲测距仪和电磁波电缆故障定位仪中用到的非周期信号提出了顺序等效采样的方法,结合FPGA内部的锁相环倍频和移相实现了50MSPS的32倍频1.6GSPS等效采样。在设计举例中选用经济型Cyclone IV系列EP4CE30F23I7N芯片,片上最高频率只支持437.5MHz,最高等效采样速率受到限制。如果选用功能更强大的其它系列或其它厂家的FPGA芯片,又或者随着电子技术的进一步发展,采用这种原理的顺序等效采样方法也能达到更高的采样频率,能更好地解决非周期信号采样的问题。

[1]唐邵春.基于时间并行交替技术的超高速高精度波形数字化研究[D].中国科学技术大学 博士论文,2012(5).

[2]石明江.100MHz数字存储示波器等效采样的研究[D].电子科技大学硕士论文,2006(2).

[3]郑君里等.信号与系统[M].高等教育出版社,2000.

[4]Altera.Cyclone IV Device Handbook[J].Altera Corporation, 2013(5).

[5]任爱锋等编著.基于FPGA的嵌入式系统设计[M].西安电子科技大学出版社,2005.

张海鹏(1983—),男,陕西榆林人,工程师,大学本科,主要从事矿用产品的资质申办及质量管理工作。