KeyStone多核DSP中断系统原理及实现

2015-02-05中国电子科技集团公司第七研究所陈玉生

中国电子科技集团公司第七研究所 陈玉生

KeyStone多核DSP中断系统原理及实现

中国电子科技集团公司第七研究所 陈玉生

本文概述KeyStone多核DSP中断系统的架构,分析DSP中断系统原理以及中断系统的实现,最后以TCI6614 GPIO为例说明中断系统的实现。

KeyStone多核DSP;中断系统

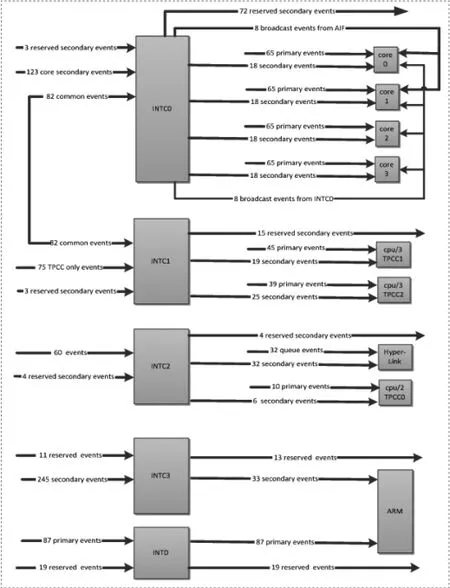

1 多核DSP中断系统架构

TI keystone系列DSP中断由两部分组成[1],芯片中断控制器(INTC)和DSP核中断处理控制器(corePac Interrupt Control)。INTC共有4个,如图1所示, INTC0主要负责core0,core1,core2,core3,INTC1主要负责控制EDMA3的TPCC1和TPCC2,INTC2主要负责控制EDMA3的TPCC0和HyperLink的中断,INTC3负责与ARM中断。corePac内部的中断控制器位于corePac内部,主要负责将外部中断事件转换为CorePac内部的中断信号,在DSP的Core0到Core3各有自己的核内中断控制器。

图1 TCl6614中断处理系统框图

INTC0的输入系统事件有3预留的二级事件,123个内核二级事件和82个公共事件,共有128个输入系统事件;而INTC0输出给Core0的主机事件有AIF的广播事件8个,二级主机事件18个,INTC0广播事件8个,INTC0输出给Core0的主机事件共有34个 。

2 INTC中断控制器

INTC中断控制器[2]主要作用是负责将系统事件映射为CorePac可直接处理的主机事件。系统事件可以是外部设备模块产生。INTC接收到系统事件并将其映射到内部通道,内部通道将其为映射到主机中断接口上。在KeyStone架构中,中断信道和主机事件之间的映射关系是确定的,一一对应的映射关系。

通过编程配置C66x CorePac中断控制器产生CPU中断事件,INTC中断控制器最多同时输入128个系统中断事件,经过INTC的逻辑组合,最后输出12个CPU中断、1个CPU的异常中断。

INTC中断控制器通过以下4个步骤将系统事件映射为主机事件,如图2所示,这4个步骤如下:

步骤1:使能系统事件;

步骤2:获取中断状态信息;

步骤3:信道映射;

步骤4:主机事件映射。

图2 lNTC中断控制器系统

步骤1:使能系统事件

通过编程设置使能系统事件,被使能的系统事件将会产生并映射为主机事件。

步骤2:获取中断状态信息

INTC从状态寄存器获取系统事件状态信息,通过状态信息去判断系统事件是否在处于使能状态。状态寄存器中的每个比特位是独立的,当状态寄存器的状态位被置位时,使能相应的系统事件;当状态寄存器被清除,其对应的系统事件状态被清除。

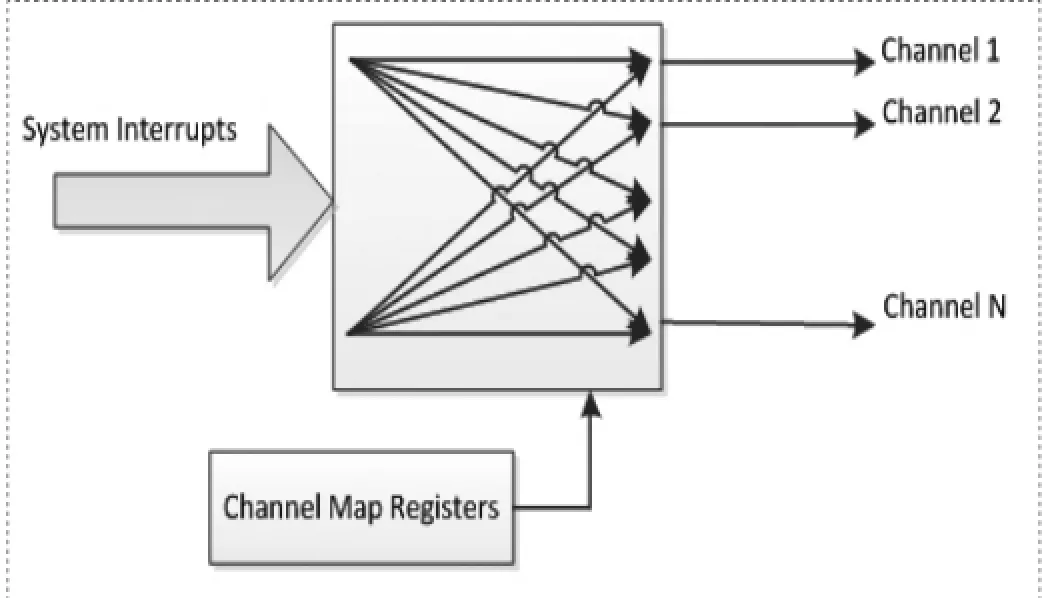

步骤3:信道映射

INTC把已使能的系统事件映射到内部通道,如图3所示。当多个系统事件被映射到相同的信道时,通过逻辑组合的方式将多个系统事件映射为多个或者一个主机事件,或操作将多个系统事件进行组合在一起。

步骤4:主机事件映射

主机事件映射是固定的,一对一的对应关系,INTC将已定义好的信道事件映射到主机事件中。每个信道映射均有一个寄存器来定义主机事件。

图3 信道映射模块

2.1 中断映射方法和原理

2.1.1 通道中断映射寄存器(CH_MAP_REGx)

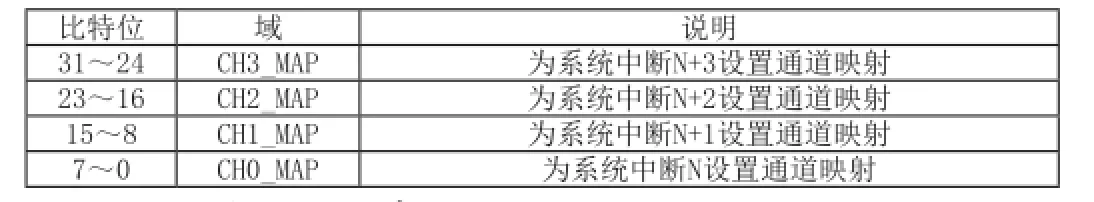

通道映射寄存器定义了每个系统事件对应的信道。每个系统事件映射需要8bit,因此1个32bit的中断映射寄存器可以配置4个系统事件,如图4所示,表1-通道中断映射寄存器比特位域说明。系统事件数最多为1024个,因此最多需要256个中断映射寄存器(CH_MAP_REGx)。

图4 中断映射寄存器

表1-通道中断映射寄存器比特位域说明

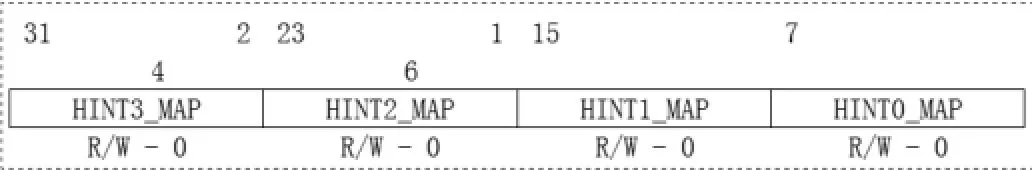

2.1.2 主机中断映射寄存器(HINT_MAP_REGx)

主机中断事件映射寄存器为每个主机事件映射到每个通道,这个寄存器完成INTC的信道到CorePac中断控制器的主机事件的映射。INTC信道和主机事件的映射关系是固定的,一一对应关系。每个通道需要8bit,因此1个 32bit的主机中断事件寄存器映射4个通道。由于映射通道数最多为256个,因此最多需要64个主机中断映射寄存器(HINT_MAP_REGx),如图5所示,表2-主机中断映射寄存器比特域说明。

图5 主机中断映射寄存器

表2-主机中断映射寄存器比特位域说明

3 CorePac中断控制器

CorePac中断控制器[3]将外部中断信号转换为CPU中断的输入(INT[15∶4])。外部输入中断信号有3个,分别是1个RESET事件(复位信号)、1个NMEVT事件(不可屏蔽中断信号)、128个EVT事件(普通中断事件信号)。在CPU内部,可供处理的中断信号为INT[15:4],即CPU可处理的中断信号只有12个,如图6所示。

CorePac中断控制器负责将输入事件通过逻辑组合方式产生17个中断信号给CorePac DSP,这17个中断信号为:

1个可屏蔽硬件异常中断;

1.3.3 随访时间 本观察组所有患者均于2016年1月起开始随访,至2017年12月结束,当随访期满、复发或发生死亡事件即终止。随访方式主要通过上门随访或门诊随访。对照主要是收集所有入组病人在建立健康档案前一年没有经过社区指导与监护的各项对比指标情况。

12个可屏蔽硬件中断;

1个不可屏蔽中断;

1个复位中断信号。

CorePac中断控制器包括有中断选择器,事件组合器,异常组合器。其中中断选择器负责将任意的系统事件通过逻辑组合后产生12个可屏蔽中断;事件组合器主要作用是将大量的系统事件通过逻辑组合生成4个事件;异常事件组合器将任意的系统事件组合产生1个硬件异常中断。

图6 CorePac中断控制器

3.1 中断选择寄存器(lnterrupt Mux Register)

图8 DlR寄存器

图10 上升沿触发寄存器

图11 事件标志寄存器

中断选择寄存器通过编程的方式从128个源中断事件中选择12个可用的中断输入到DSP的INT中断事件,如图7所示,表3-中断选择寄存器比特位域说明。每个中断选择寄存器可以配置保存4个中断事件的信息,因此12个DSP的INT中断事件需要3个中断选择寄存器。

图7 中断选择寄存器

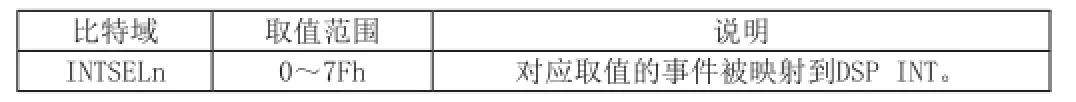

表3-中断选择寄存器比特位域说明

综上所述,每个DSP最多有1024个系统事件,经过中断映射后只有12个DSP的INT中断,

4 TCI6614中断系统实现

通过TCI6614 GPIO[4]说明中断系统的实现说明。

4.1 初始化GPlO状态

4.1.1 设置GPIO的输出状态

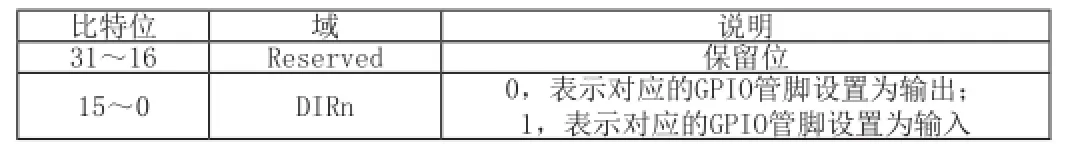

通过配置Direction Register(DIR)寄存器,GPIO端口可以作为输入端口或输出端口,如图8所示,表4-GPIO方向寄存器比特位域说明。由于需要GPIO端口产生中断给CPU,因此将GPIO配置为输出端口,寄存器相应的比特位置0,即:

DIR=0x00000000

表4-GPlO方向寄存器比特位域说明

4.1.2 设置GPIO中断使能

为了使能所有的GPIO作为中断源输入到CPU中断,Bank Interrupt Enable Register(BINTEN)寄存器最低比特位设置为1,如图9所示,表5-BINTEN寄存器使用说明。即:

BINTEN=0x00000001

图9 BlNT寄存器

表5-BlNTEN寄存器使用说明

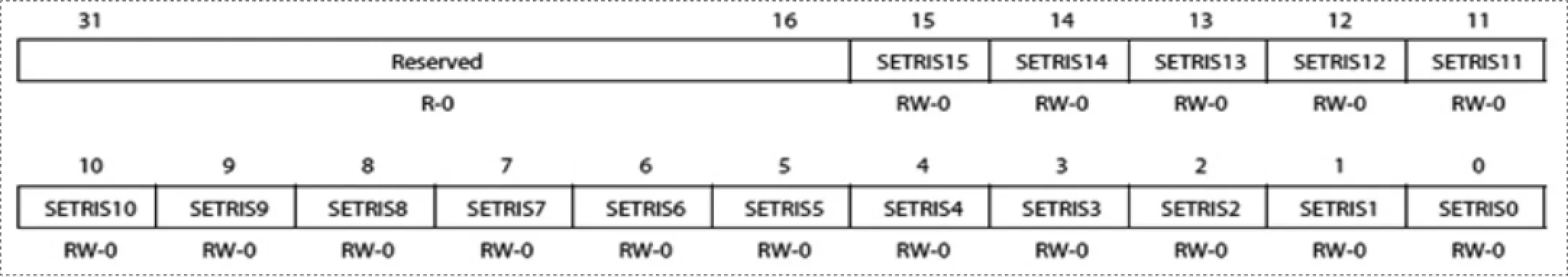

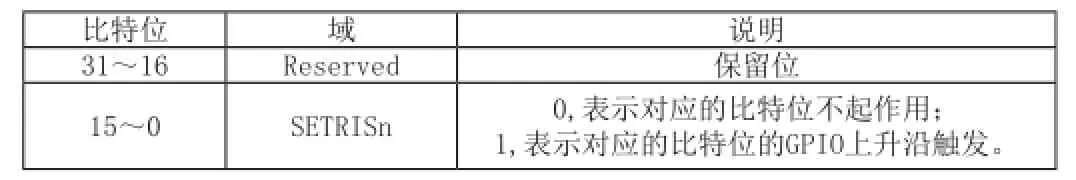

4.1.3 设置GPIO中断触发方式

触发中断可以是上升沿或下降沿,如设置上升沿为中断触发沿,则将寄存器SET_RIS_TRIG相应的比特位置1,如图10所示,如表6所示,上升沿触发寄存器使用说明,即:

SET_RIS_TRIG=0x0000ffff.

表6-上升沿触发寄存器使用说明

4.2 GPlO的中断通道映射

根据TCI6614系统事件映射,128个中断事件,前面4个是combiner的输出,其余每个中断事件号对应着EVTMASK0~EVTMASK3的比特位。GPIO的GPINT4~GPINT15对应着EventNumber事件号78~89,并且EventNumber事件号78~89对应Event Mask Register 2(EVTMASK2)寄存器的第15~25比特位。如GPINT4中断对应Event Number 78,通过设置EVTMASK2的第15比特位为0,则表示GPINT4被使能,并将作为系统事件,通过逻辑组合产生INTC2中断事件(映射到通道2上),如图11所示,表7,事件标志寄存器使用说明。

EVTMASK2=~((1〈〈14)|(1〈〈15)|(1〈〈16)|(1〈〈17)| (1〈〈18)|(1〈〈19)|(1〈〈20)|(1〈〈21)|(1〈〈22)|(1〈〈23)| (1〈〈24)|(1〈〈25))