SpaceWire系统芯片测试技术

2015-02-05王小强孙宇

王小强,孙宇

(工业和信息化部电子第五研究所,广东 广州 510610)

SpaceWire系统芯片测试技术

王小强,孙宇

(工业和信息化部电子第五研究所,广东 广州 510610)

SpaceWire总线是一种专门用于空间高速数据传输的新型总线,针对该总线设计的系统芯片是实现高速传输通信的关键,其指标的优劣决定着系统的优劣。以AT7911E为例,分析了该类芯片的结构特点,针对主要参数进行了测试分析,并提出了集成电路自动测试系统与协议功能测试相结合的综合测试方法,实现了芯片全面的性能测试验证,对于SpaceW ire系统芯片的测试具有指导意义。

系统芯片;结构特点;主要参数;自动测试系统;协议功能测试

0 引言

随着航天科技的不断进步、航天技术的应用领域的不断拓展以及航天器 (包括卫星、载人和货运飞船、空间站、月球探测器以及深空探测器等)的功能的不断提升,航天器内部设备处理数据的强度和交换信息的数量变得越来越大了。面对越来越复杂的数据处理需求,越来越多的外围设备超出了原总线例如1553等的处理能力,这对航天器设备系统网络性能的改善提出了新的挑战。

SpaceWire总线是 ESA与 NASA、JAXA和RKA等国际空间组织合作,基于IEEE 1355和IEEE 1596.3两个商用标准,通过对IEEE 1355可靠性、功耗等方面的改进,使其能够更好地满足航空航天应用而提出的一种专门用于空间高速数据传输的总线标准。SpaceWire网络具有成本低、速度以及容错高等特点,总线的单线速率最高可达400 Mbps[1]。针对上述总线协议,英国的STARDundee公司推出了协议相关产品的IP核,并授权ATMEL公司生产相关的系统芯片产品,主要包括节点芯片AT7911E和AT7912E、路由芯片AT7910E,以及远程终端控制芯片AT7913E等系列产品。

由于国内的应用需求强烈,国内多家科研院所先后开展了航天器SpaceWire信息网络构建与IP核的国产化研究,同时对SpaceWire系统芯片产品的功能测试验证方法提出了迫切需求,因此,本文通过对产品的结构以及SpaceWire总线协议等进行分析,提出了集成电路自动测试系统 (ATE:Atomatic Test Equipment)与总线协议分析相结合的Spacewiret系统芯片的测试方法。

1 芯片的基本架构

1.1 结构特点

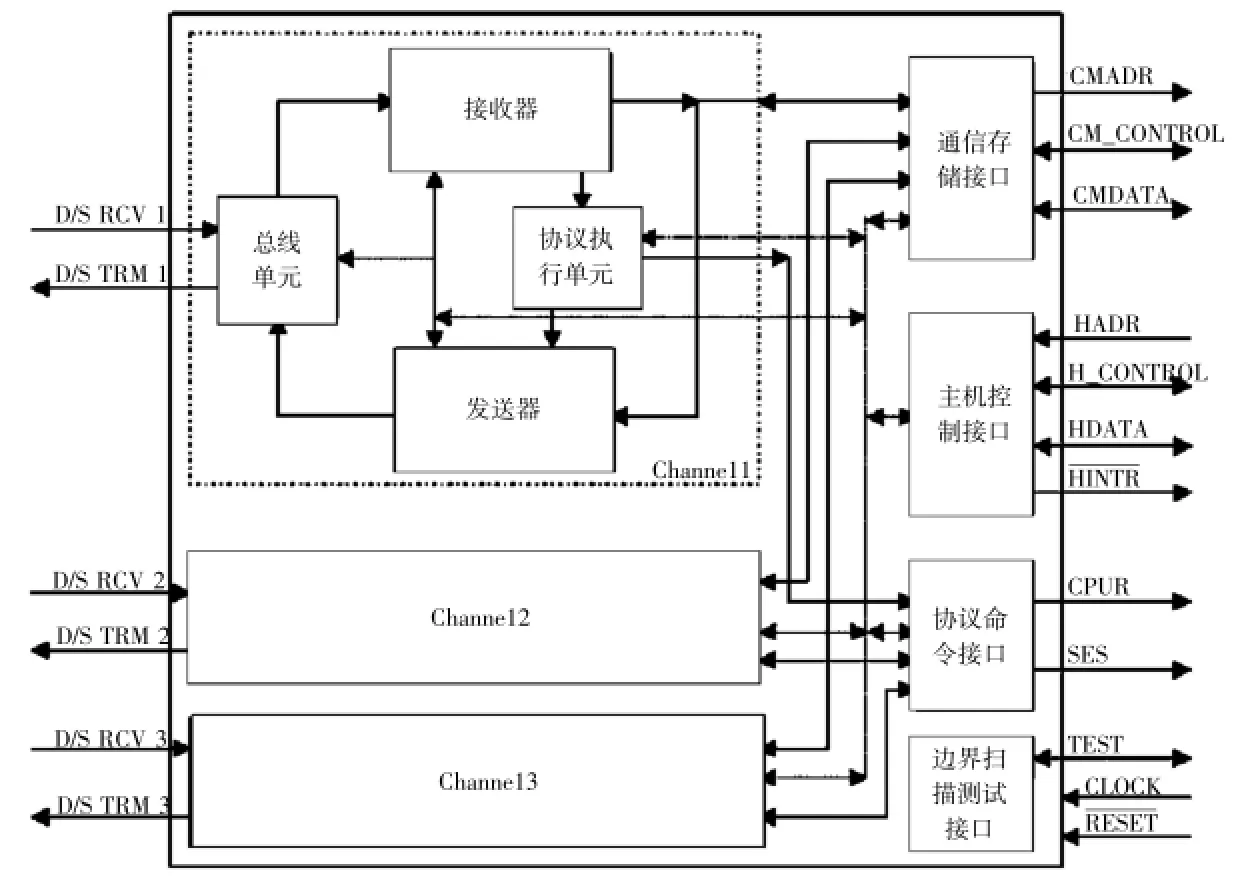

以ATMEL公司3通道SpaceWire高速信号控制器AT7911E为例进行分析,该器件由5大部分组成[2],其结构框图如图1所示。

a)3组双向SpaceWire数据通道

每组通道包含接收、发送、协议处理单元以及数据接口。其中,协议处理单元是整个器件的关键部分。

b)通信存储接口

该部分通过控制存储器地址,存储通过总线接收或发送的数据。

c)主机控制接口

该部分完成对芯片的状态控制,通过控制芯片的字读写操作来实现对芯片的功能控制。

d)协议命令接口

通过专用信号引脚来收集与内部协议处理单元有关的信息。

e)边界扫描测试接口

提供与IEEE1149.1兼容的扫描测试端口。

图1芯片的基本架构

2.2 协议功能

SpaceWire总线有点到点连接和基于路由的连接2种基本连接方式,在同一网络中可以同时使用多条总线,网络拓扑具有很高的自由度。如果设备间各条连接总线的数据传输的速度不高,则可通过增加总线的数量的方式来成倍地提高整个网络的数据传输速度[3]。各相关仪器设备通过SpaceWire系统芯片进行连接,芯片主要完成基于SpaceWire总线协议的信息控制和交换功能。

a)点到点连接

SpaceW ire总线应用最多、最广泛的连接方式为点到点的连接方式,设备通过SpaceWire总线与大容量存储单元连接,典型的连接方式如图2所示。

图2点到点连接方式

这种结构具有连接简单、单位传输数据率功耗低、应用中可以全带宽传输等优点,同时也存在一定的缺点。例如:该结构中无冗余单元,如果传输路径出现故障,设备将可能因无法连接而丢失;此外,当未全速传输时,带宽的利用效率也比较低。

2)基于路由的连接

SpaceWire路由器可以允许更多的设备进行数据交换。典型的基于路由器的连接方式如图3所示。

该架构具有多变灵活的结构、所有节点上的设备均能够通过路由与其他的设备进行数据交换、数据及控制可以通过网络实现、控制信息流通常可以与数据流分开等优点,但存在需要考虑信息堵塞情况、路由存在潜在单点故障以及系统会增加路由器的功率消耗等缺点。

图3基于路由的连接方式

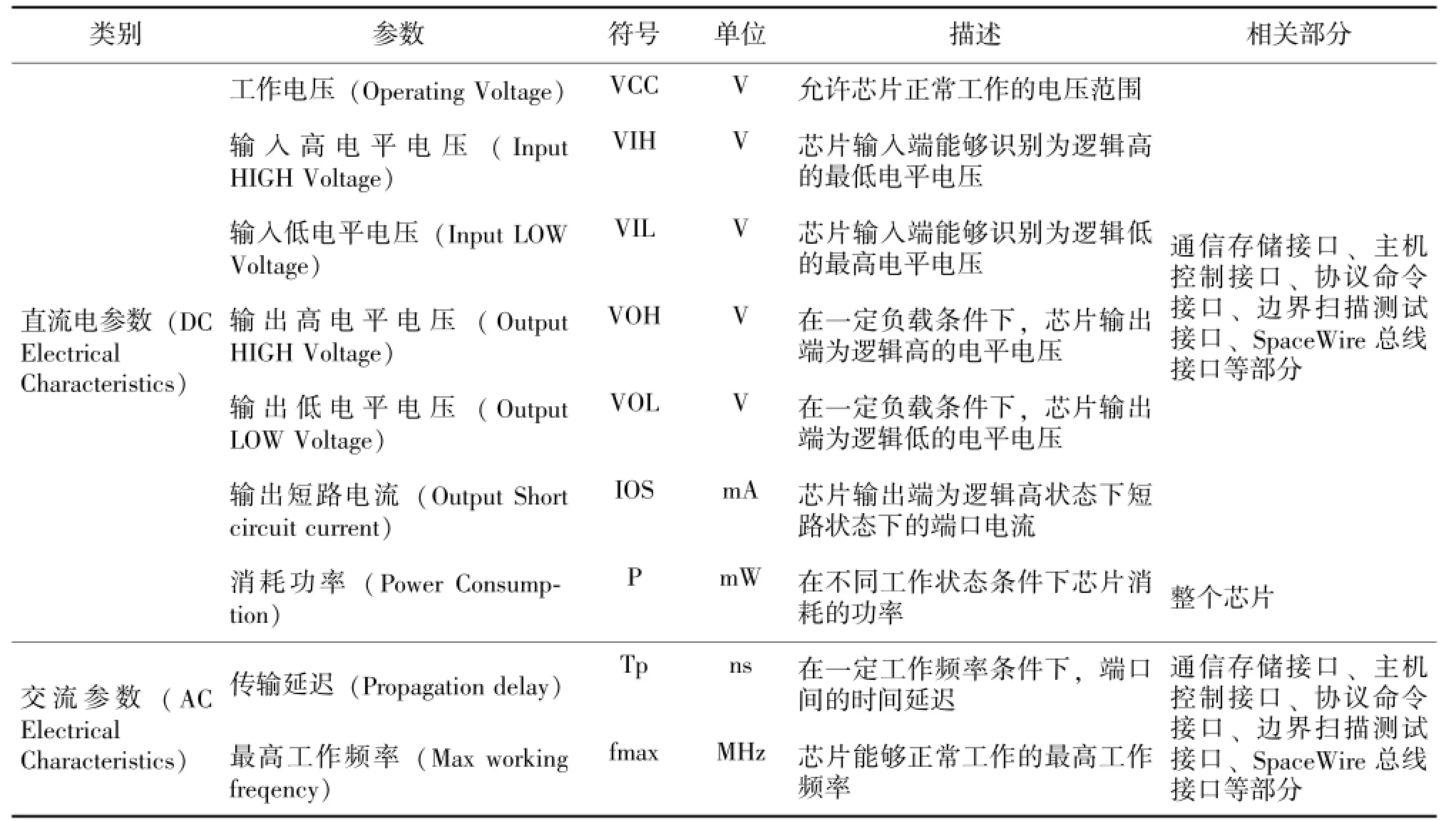

2.3 参数分析

通过对该产品的性能参数进行分析,发现该类芯片的性能指标主要包括系统功能测试 (Function Test)、直流电参数 (DC Electrical Characteristics)、交流参数 (ACElectrical Characteristics)3大部分。直流电参数主要描述了引脚接口的端口特性,交流参数主要描述了引脚接口的时序特性。相关参数的描述如表1所示。

2 测试方法

2.1 交直流参数测试

芯片出厂前都必须经过测试验证以保证芯片的质量,传统芯片的测试主要是基于ATE进行的,ATE是一种集成了多种测试功能的测试设备,具有数字测试分析、电源和信号采集分析以及混合信号分析等测试能力,系统可靠,测试效率高,能够迅速地完成产品的直流电参数、交流参数的测试[4]。

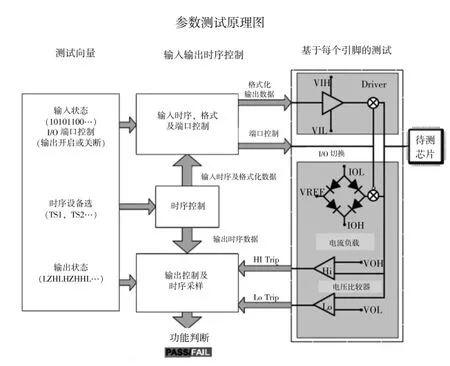

参数测试的基本原理如下所述。

a)根据反映端口特性的测试向量转换为ATE可以识别的逻辑状态文件,内容包括输入状态、时序设置和输出状态等相关文件。

b)在ATE的编程控制软件系统中,完成输入输出时序控制设置等相关操作,包括格式化输入数据、端口控制以及输入输出时序控制等。

c)在不同的时序时刻,待测器件的每个引脚输出状态与正常输出文件进行比较,所有时刻一致则判断时序功能正常,在此基础上完成输入输出电平、带负载能力以及时序采样等测量工作,实现交直流参数的测试。

交直流参数测试的基本原理图如图4所示。

表1 主要参数

图4 交直流参数测试原理图

利用ATE测试系统,通信存储接口、主机控制接口、协议命令接口、边界扫描测试接口和SpaceWire总线接口等的交直流参数能够得到精确的定量测量,但是SpaceWire系统芯片的协议组网功能测试无法在ATE测试系统上完成,该系统功能需要通过其他的手段进行测试验证。

2.2 协议功能测试

为了验证SpaceWire系统芯片兼容SpaceWire标准ECSS-E-50-12A,需要对协议的兼容性开展测试,对应在芯片上,即需要对芯片内部SpaceWire数据通道中协议处理单元的功能进行验证。

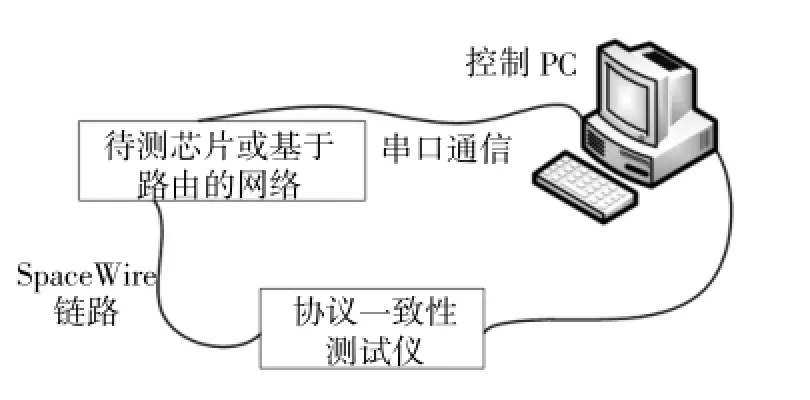

协议功能测试需要利用专用的协议一致性测试仪搭建协议测试系统,系统包括控制PC、待测芯片以及协议一致性测试仪等,测试系统的架构如图5所示。控制PC控制整个测试过程,以及通讯过程的实时监控。待测芯片或基于路由的芯片网络,需要以测试板形式测试,板上包括供电、数据交换接口等。串口能够用于被测电路测试板的配置、测试程序的下载以及将被测电路的状态信息发送到控制PC上等过程中,控制PC接受到的信息会在显示器上实时显示。

图5 协议测试验证框图

功能协议测试主要通过软件进行控制,采用大量的测试用例,发送或接收广播消息、信息标识、数据位和命令控制的信息,并根据通信协议判断数据接收的有效性和准确性,实现SpaceWire器件的协议兼容性[5]。

3 结束语

本文通过对SpaceWire系统芯片开展结构分析,对芯片的参数进行了总结分类,针对参数的特点以及协议功能测试提出了系统全面的测试解决方案,即ATE测试系统与协议测试系统联合测试。该测试方法既实现了芯片的交直流参数的定量精确测试,又完成了对芯片协议功能的设计验证,为行业内该类芯片的质量控制、设计验证提供了技术指导。

[1]徐曙清,王震,董瑶海,等.SpaceW ire与SpaceFibre高速总线发展与研究 [J].上海航天,2014,31(1):29-36.

[2]AT7911E triple SpaceWire links high speed controller [DB/OL].ATMEL,7737B–AERO–05/08.

[3]STEVE Parkes.SpaceWire User's Guide[M].STARDundee Limited,2012.

[4]陈新军.基于ATE的LVDS芯片测试技术 [J].电子产品可靠性与环境试验,2012,30(S1):207-210.

[5]ECSS-E-ST-50-12C-2008,SpaceWire-Links,nodes,routers and networks[S].

SpaceW ire System Chip Testing Technology

WANG Xiao-qiang,SUN Yu

(CEPREI,Guangzhou 510610,China)

SpaceW ire is a new bus standard used for high speed data transmission between space instruments.And the system chip designed for it is the key to realize high speed transmission,whose quality determines the merits of the system.Taking AT7911E as an example,the structure characteristics of the chip are analyzed, and the main parameters are tested.At last,a comprehensive test method combining ATE and protocol function test is put forward, which achieves the overall performance testing and verification of system chip and has the guiding significance for the test of SpareWire system chip.

system chip;structure characteristics;main parameter;ATE;protocol function test

TN 407

:A

:1672-5468(2015)05-0024-04

10.3969/j.issn.1672-5468.2015.05.006

2015-05-21

王小强 (1982-),男,江苏宿迁人,工业和信息化部电子第五研究所元器件中心高级工程师,从事集成电路测试验证研究工作。