PCB阻抗测试研究

2015-02-05刘文敏王红飞广州兴森快捷电路科技有限公司广东广州510063深圳市兴森快捷电路科技股份有限公司广东深圳518057

刘文敏 王红飞 陈 蓓(广州兴森快捷电路科技有限公司,广东 广州 510063)(深圳市兴森快捷电路科技股份有限公司,广东 深圳 518057)

PCB阻抗测试研究

Paper Code: S-113

刘文敏 王红飞 陈 蓓

(广州兴森快捷电路科技有限公司,广东 广州 510063)

(深圳市兴森快捷电路科技股份有限公司,广东 深圳 518057)

信号高频、高速化发展对信号完整性要求越来越严格,阻抗匹配性成为信号完整性至关重要问题。PCB阻抗测试准确性受测试方法、设备差异等因素影响,因此如何准确、有效测试PCB阻抗越来越受到人们的关注。文章探讨了阻抗测试设备类型、测试方式、阻抗线长、迹线取值区间对PCB阻抗测试结果的影响,并进一步分析了采用不同设备测试非常规阻抗结果的差异性,给出了不同设备非常规阻抗的测试方法,对PCB阻抗测试具有指导意义。

信号完整性;阻抗;测试;PCB

1 前言

信号高频与高速化发展对信号完整性要求越来越高,阻抗匹配性是影响信号完整性的一个重要因素,阻抗匹配性的提高对阻抗测试准确性要求也越来越高。IPC推荐采用时域反射计(Time Domain Reflectometry ,简称TDR)测试PCB阻抗,其测试原理为:当传输路径中发生阻抗变化, 部分能量会被反射, 剩余的能量会继续传输,注入到媒介的能量、反射回的能量与阻抗的变化有理论上的数学关系。只要知道发射波的幅度及测试反射波的幅度,就可以计算阻抗的变化,同时只要测试由发射到反射波再到达发射点的时间差就可以计算阻抗变化的位置,如图1所示。

PCB阻抗测试根据设备类型可分为时域基、频域基测试设备。时域基设备信号源直接发射时域信号;频域基设备(又称VNA设备)发射的频域信号经傅里叶逆变化后转化为时域信号,二者发射信号源不同,阻抗测试结果也会有差异。另外,操作人员的测试方式、阻抗线长、测试设备信号上升时间以及阻抗的阻抗设计值都会对测试结果产生影响,因此,本文研究阻抗测试设备、阻抗测试方式、阻抗线长及迹线取值区间、设备上升时间、非常规阻抗设计等因素对阻抗测试结果的影响,为PCB阻抗测试提供指导。

图1 TDR阻抗测试原理图

2 试验

2.1 试验材料及仪器

材料:覆铜板、半固化片

仪器:TDR设备(时域基、频域基)

2.2 试验方法

试验设计多层PCB板,按照设计要求制作不同线长、不同阻抗值(10Ω~120Ω)的阻抗coupon。

试验流程:开料→烘板→内层干膜→内层蚀刻→内AOI→棕化→层压→钻孔→去钻污→沉铜→板镀→外层干膜→电镀→外层蚀刻→外AOI→阻焊→沉金→铣板

3 结果与讨论

3.1 不同测试设备测试结果差异

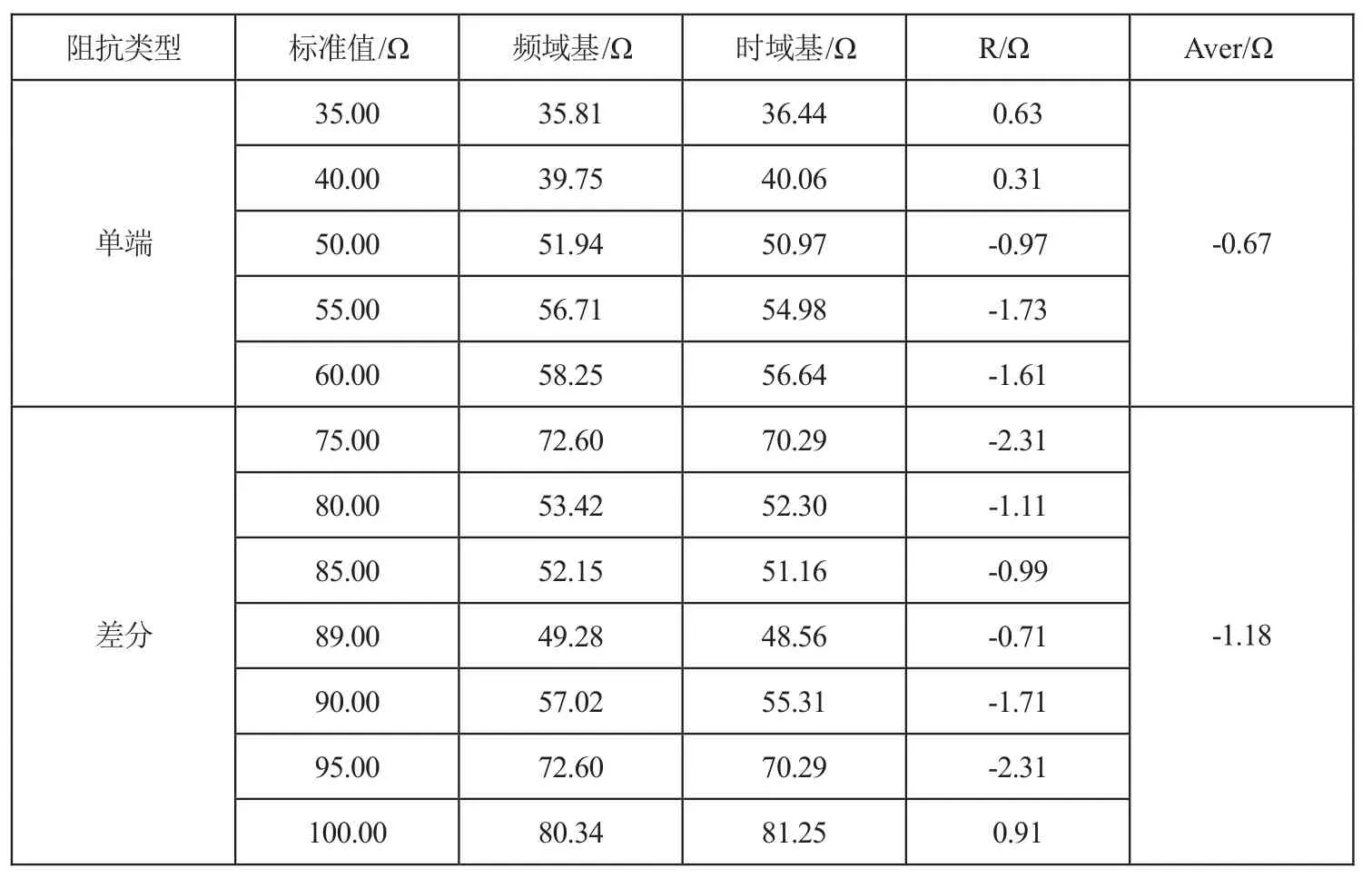

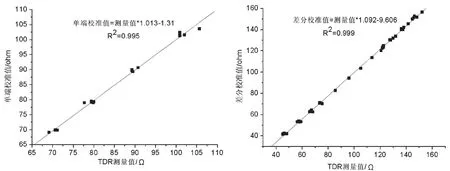

对于不同的阻抗测试设备,校准方式,线缆、探头等各不相同,因此相同阻抗线使用不同阻抗设备进行测试时,测试结果会有差异。表1给出了在不同单端、差分阻抗设计值下,分别使用时域基、频域基阻抗测试设备的测试结果。由表看出,分别使用两种测试设备测试单端及差分阻抗,测试结果平均差异分别为0.67Ω、1.18Ω。图3为两种设备测试偏差统计图,由图看出两种设备测试结果平均偏差可控制在±2%以内。

表1 不同测试设备阻抗测试结果对比

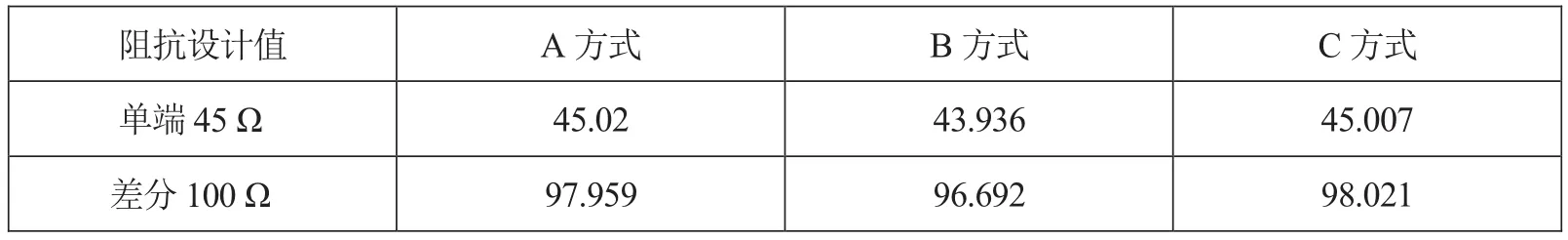

3.2 测试方式对测试结果影响

PCB厂家多采用探头方式测试PCB阻抗线阻抗值,采用这种方式测试PCB外层阻抗时,阻抗板放置方式会对测试结果产生影响。试验待测阻抗条采用A、B、C三种方式放置(如图4),分别测试相同外层阻抗线阻抗值,测试结果如表2。由表看出,采用A、C两种方式测试结果差异性可控制在0.5Ω内,可以忽略;采用B方式测试结果明显低于A、C两种方式,采用B方式测试阻抗值与真实值相差约2Ω,因此阻抗测试时待测阻抗线不可接触测试台面。

图2 两种设备测试偏差统计

表2 三种测试方式阻抗结果

3.3 阻抗线长对测试结果影响

信号经过PCB阻抗线传播时,信号会发生衰减,线长越长,信号衰减越严重,TDR曲线会出现“阻抗上扬”现象,导致测试结果偏大。图5为相同阻抗设计值、不同线长时,阻抗测试TDR曲线,由图看出,阻抗线线长由127 mm增加至431.8 mm,TDR曲线“上扬”情况越来越严重,当线长为431.8 mm时,单端、差分TDR曲线最大值与最小值差异分别为4Ω、10Ω。表3给出了不同线长阻抗测试结果,由表看出,相同阻抗线,线长越长,阻抗测试结果越大,线长为127 mm与431.8 mm阻抗测试结果相差约3Ω,这对于高精度阻抗测试来说是不可接受的。“阻抗上扬”属于测试固有现象,不可避免,因此测试PCB图形阻抗时,在满足测试设备能力条件下,尽量选择长度较短的阻抗线进行测试。

表3 不同线长阻抗测试结果

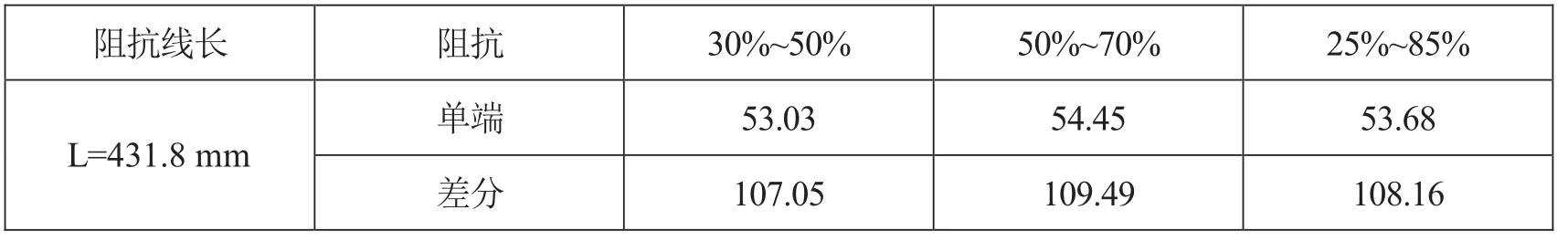

3.4 迹线取值区间对测试结果影响

阻抗迹线取值区间直接决定测试结果准确性。图3为L=152.4 mm单端28Ω阻抗TDR曲线图。由图看出,TDR曲线0~50%区间内阻抗波动较大,50%~70%区间内曲线较平滑,取值范围若取25%~85%,测试结果并不准确,取50%~70%区间,测试结果较为准确。表4为L=431.8 mm的单端、差分阻抗线不同取值区间测量结果。由表看出,取值区间在50%~70%测试结果相比30%~50%取值区间结果要高1Ω~2Ω,而当取值区间范围在25%~85%时,其测量结果介于30%~50%与50%~70%测试结果之间。这是因为当线长较长时,由于“阻抗上扬”现象导致TDR曲线后端阻抗值偏大,当取值区间为50%~70%时,其测量结果要比真实值大,导致平均值变大。因此当阻抗线较短时,取值区间建议取50%~70%区间,当线长较长时,取值区间建议取(30%~50%)Ω,测量时应根据实际情况灵活选择测量区间。

图3 L=152.4mm单端28Ω TDR曲线

表4 不同阻抗取值区间测试结果

3.5 设备上升时间对测试结果影响

采用TDR设备测试传输线阻抗时,当传输线上出现阻抗不连续的现象时,在阻抗变化的地方阶跃信号就会产生反射的现象。TDR 设备感知传输线阻抗不连续的分辨率取决于TDR 设备所发出的阶跃信号上升时间的快慢,上升时间快所获得的分辨率就高。而TDR 设备的上升时间往往和测试系统的带宽紧密相关,带宽高的测试系统有更快的上升时间。图4给出了不同上升时间时,测试相同阻抗线TDR曲线,由TDR曲线图看出,当上升时间≤35 ps时,测试L=12 mm的阻抗线,TDR曲线可以看到明显平滑区域,此区域阻抗值即为线路区域阻抗值;当上升时间≥100 ps时,TDR曲线上看不到平滑区域,线路区域阻抗无法测试。综合可看出,测试系统上升时间直接决定了设备所能测试最短阻抗线长度,表5给出了不同上升时间测试系统所能测试最短阻抗线长。

图4 不同上升时间TDR曲线

表5 系统上升时间与测试最短线长

3.6 非常规阻抗测试

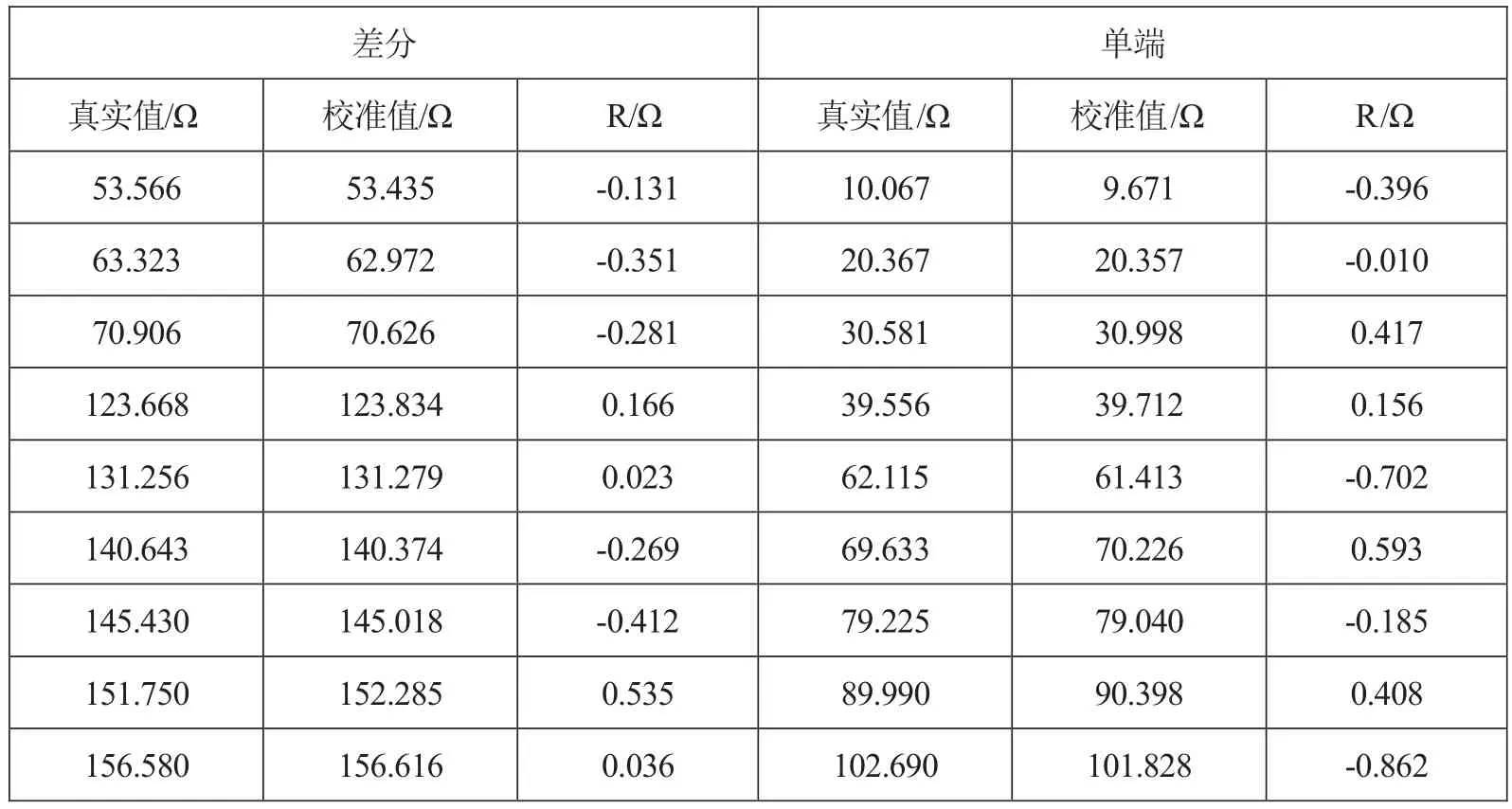

使用TDR设备测试非常规阻抗(单端:Z≤40 Ω或Z≥60 Ω,差分:Z≤80ohm或Z≥120 Ω),需要使用与待测阻抗值接近的空气线校准,对于批量性PCB厂不适合使用这种校准方式。图5给出了使用50 Ω空气线校准后测试非常规阻抗的方法,表6给出了使用公式校准后理论计算值与实测值差异。由图及表看出,使用公式校准测试非常规阻抗与实测偏差可控制在1 Ω内,满足非常规阻抗的测试要求。

图5 非常规阻抗公式校准方法

表6 公式校准值与真实值

4 结论

通过以上研究,可以得出以下结论:

(1)分别使用时域基、频域基测试设备测试单端及差分阻抗,测试结果平均差异分别为067Ω、1.18Ω,两种设备测试结果平均偏差可控制在±2%以内。

(2)测试外层线路阻抗时,当待测阻抗与测试台面接触时,测试结果会偏低约2ohm,阻抗测试时阻抗线不可与台面相接处。

(3)测试图形内阻抗线阻抗,阻抗线越长,“阻抗上扬”现象越明显,在满足设备测试能力条件下,尽量选择较短阻抗线测试。

(4)阻抗线较短时,迹线取值区间范围可选50%~70%,线长较长时,迹线取值区间范围可选30%~50%。

(5)TDR设备上升时间越小,所能测试阻抗线长越短。

(6)使用公式校准方法测试非常规阻抗,校准后测试值与真实值差异可控制在1ohm以内,满足测试要求。

[1] 于争. 信号完整性揭秘[M]. 北京∶机械工业出版社,2013.

[2] Johnson H,Graham M. 高速数字系统设计[M]. 北京∶电子工业出版社,2004.

[3] IPC-TM-650-2.5.5.7. Characteristic Impedance and Time Delay of Lines on Printed Boards by TDR[S]. 2004∶1-15.

刘文敏,硕士,技术中心研发工程师,主要从事PCB信号完整性研究。

Study on PCB impendence measurement

LIU Wen-min WANG Hong-fei CHEN Bei

With the improvement of signal transmission frequency and speed, the requirement is more and more strict with signal integrity(SI). Meanwhile, impedance matching is becoming issue of crucial importance. The accuracy of PCB impedance measurement is related to measuring method and equipment differentiation , so how to measure PCB impedance accurately and effectively has been widely concerned. The effect of equipment varieties, test styles, impedance line lengths, range of trace on the results of PCB impedance measurement was studied. Simultaneously, the variety of results measured by different equipments for unconventional impedance was also investigated, and the methods of measuring unconventional impedance were also provided which have great significance for directing PCB impedance measurement.

Signal Integrity; Impedance; Measurement; PCB

TN41

A

1009-0096(2015)03-0140-06